提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

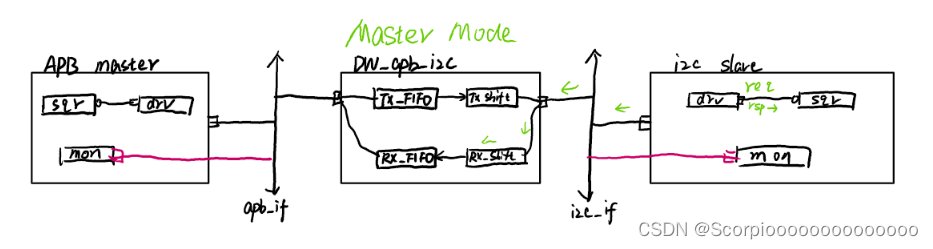

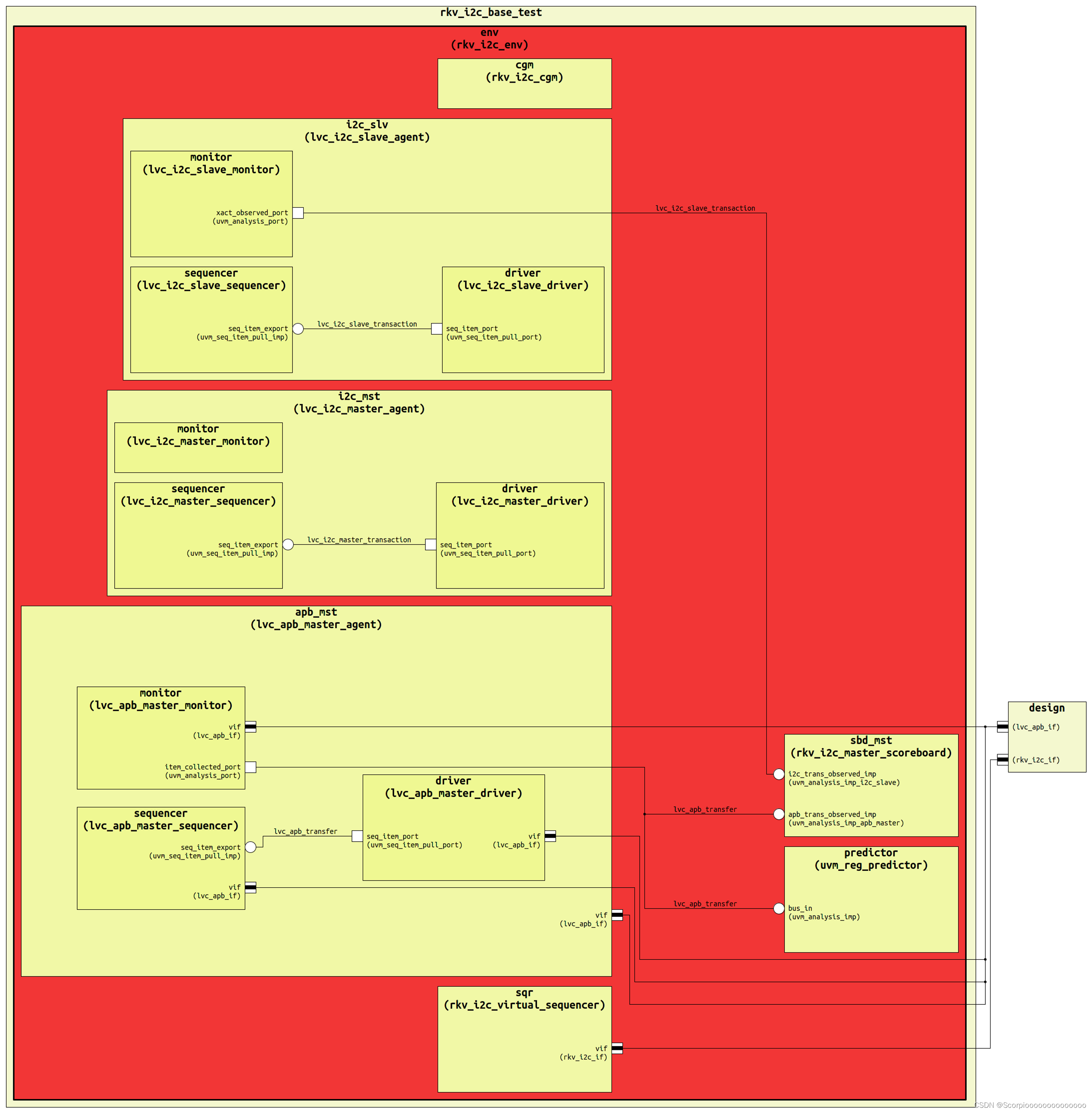

整体结构:

DW_apb_i2c、apb-VIP、i2c-VIP

testbench:

目标:

完成测试序列的编写

提示:以下是本篇文章正文内容,下面案例可供参考

一、准备工作

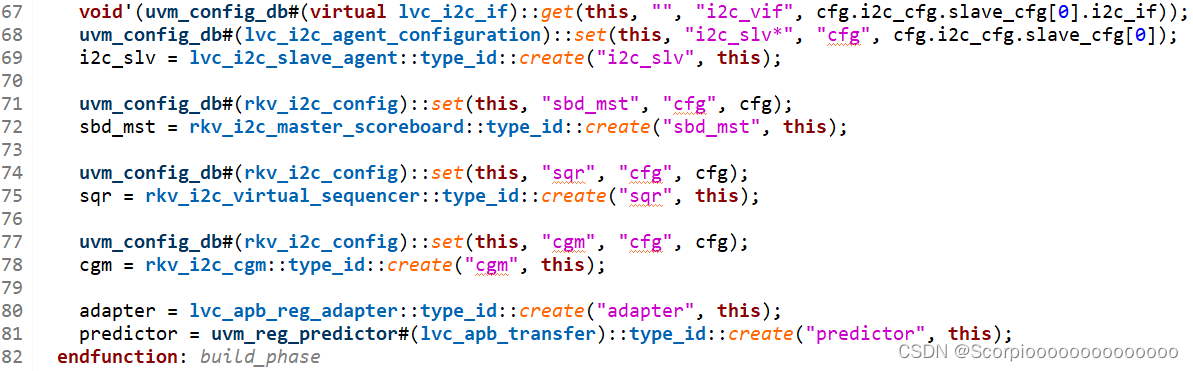

1.1 组件配置传递

- 在env中完成组件配置的传递,env.cfg句柄由顶层写测试用例传递

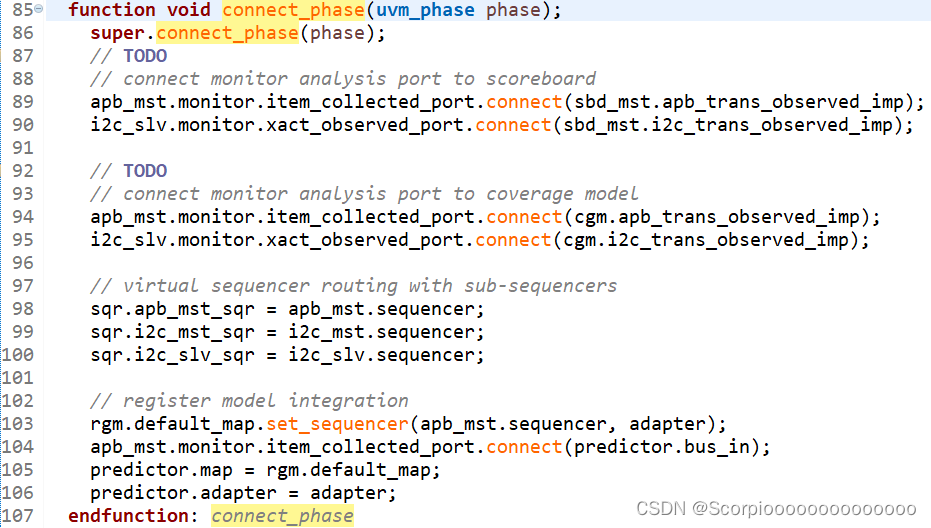

1.2 端口连接

1.3 elem_seq编写

apb一侧的序列

- rkv_apb_config_seq

对一些寄存器域做了基本配置 - rkv_apb_write_packet_seq

apb写入操作,写前TX FIFO不满 - rkv_apb_read_packet_seq

apb读取操作,读取时有三种状态:1.RX FIFO不为空,有数据就读取、2.RX FIFO满了再读取、3.不检查RX FIFO直接读取数据 - rkv_apb_wait_packet_seq

等待TX FIFO为空 - rkv_apb_intr_wait_seq

等待中断发生 - rkv_apb_intr_clear_seq

清除中断

i2c一侧的序列

- rkv_i2c_slave_write_response_seq

i2c_slave响应主设备写操作 - rkv_i2c_slave_read_response_seq

i2c_slave响应主设备读操作

二、冒烟测试

寄存器访问测试、写测试、读测试以及中断测试,相应序列如下:

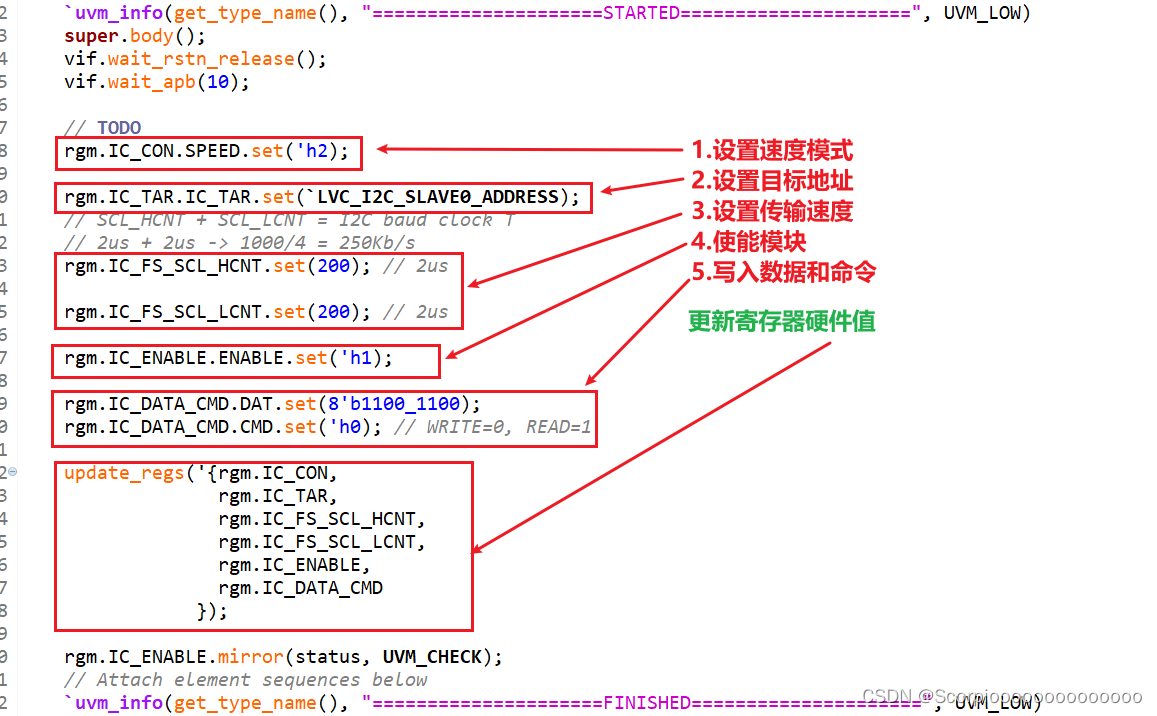

1.rkv_i2c_master_quick_reg_access_virt_seq

测试目的:部分寄存器的访问是否正确

代码

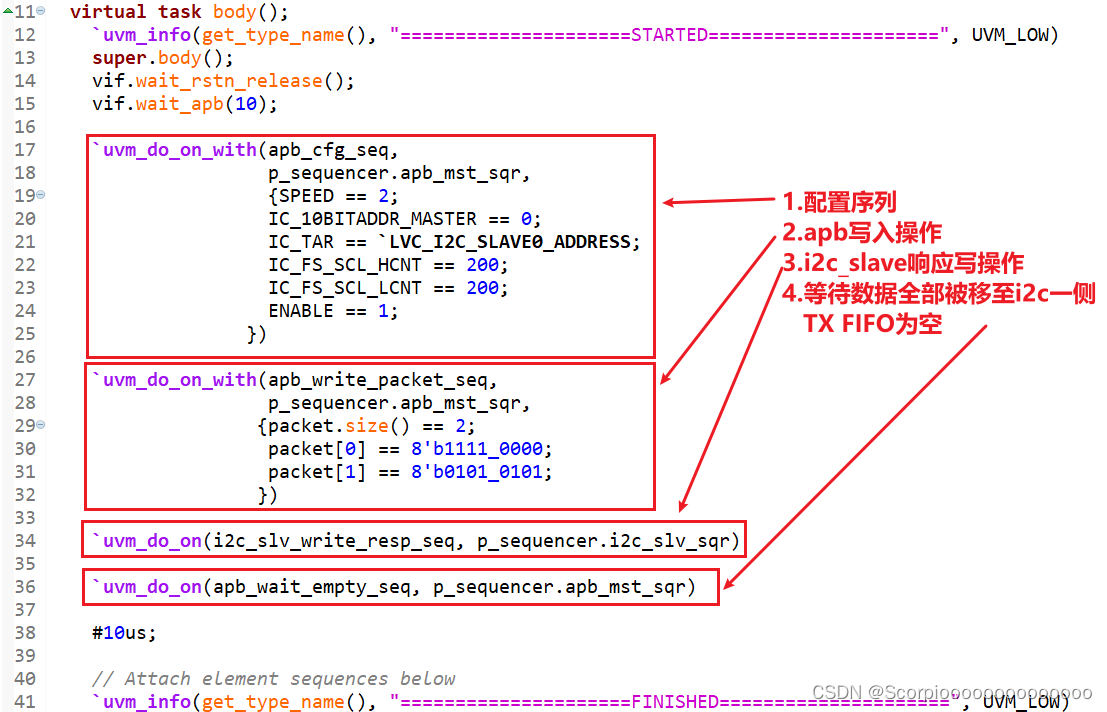

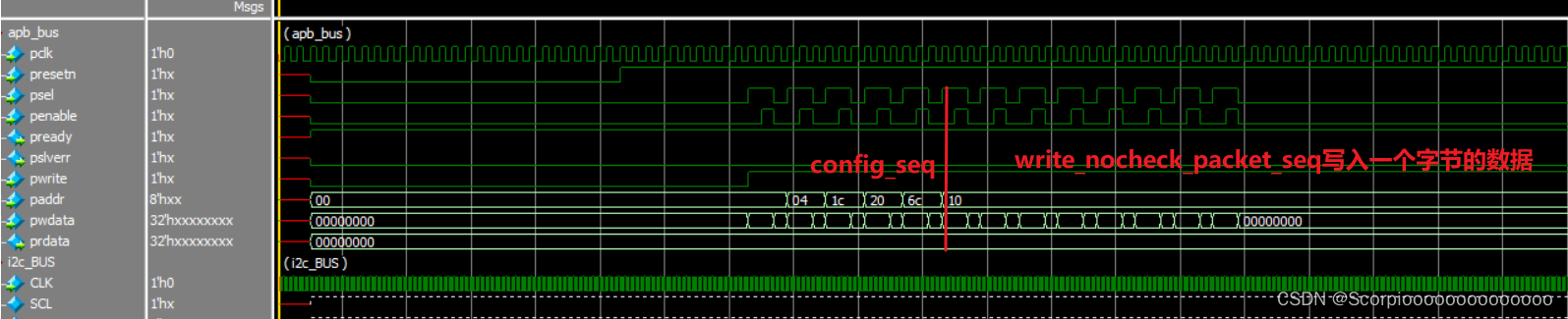

2.rkv_i2c_master_directed_write_packet_virt_seq

测试目的:写入操作是否正确

代码

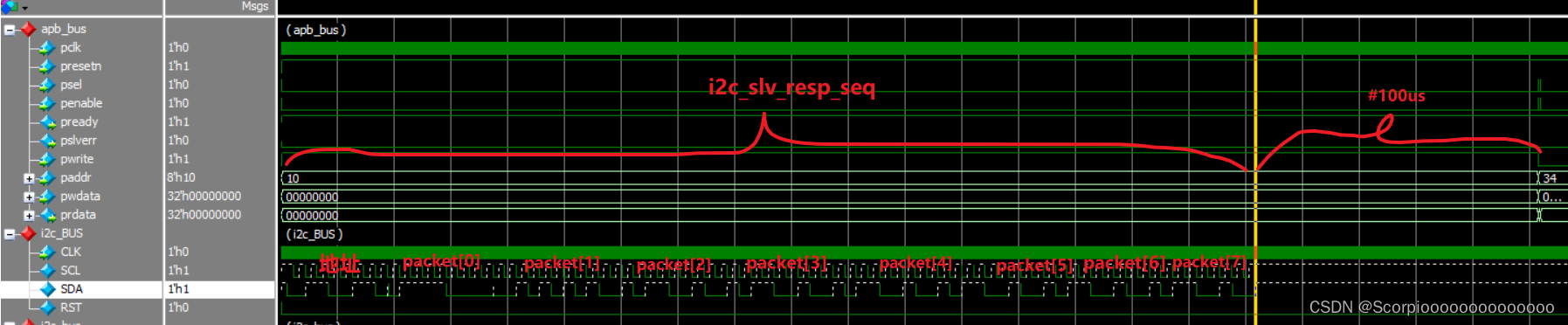

3.rkv_i2c_master_directed_read_packet_virt_seq

测试目的:读取操作是否正确

代码

4.rkv_i2c_master_directed_interrupt_virt_seq

测试目的:中断是否正常发生

代码

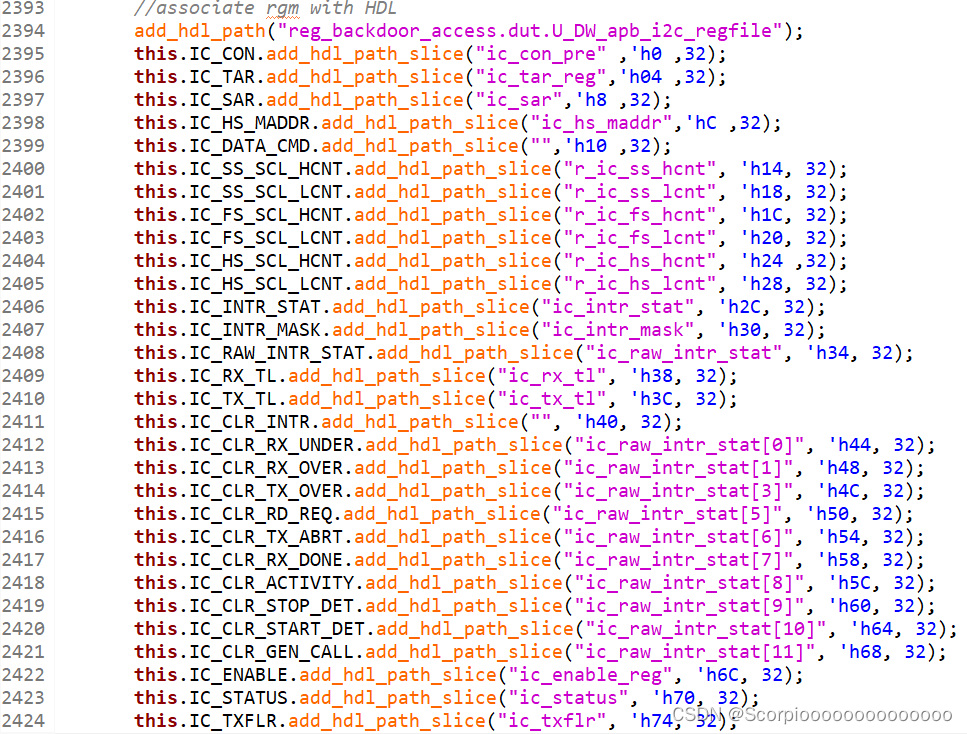

三、寄存器内建序列测试

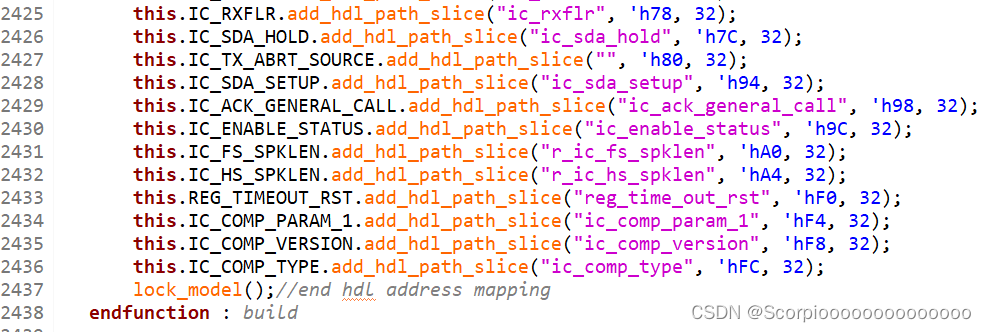

在使用部分内建序列时需要进行后门访问,因此在开始前需要确保寄存器模型在建立时将各个寄存器映射到DUT一侧的HDL路径。

❓问题一: 若add_hdl_path的硬件路径为reg_backdoor_access.dut只要偏移地址正确就能映射成功

❓问题二:

怎么才能跳过只读寄存器的检查?使用禁止域名又出现了问题三

❓问题三:在寄存器域的有效性检查中,对只读寄存器也做了检查,而且有一个寄存器使用了禁止域名却没有跳过bit_bash测试

❓问题四:复位检查时出现访问IC_DATA_CMD期间出现了pslverr,为什么?

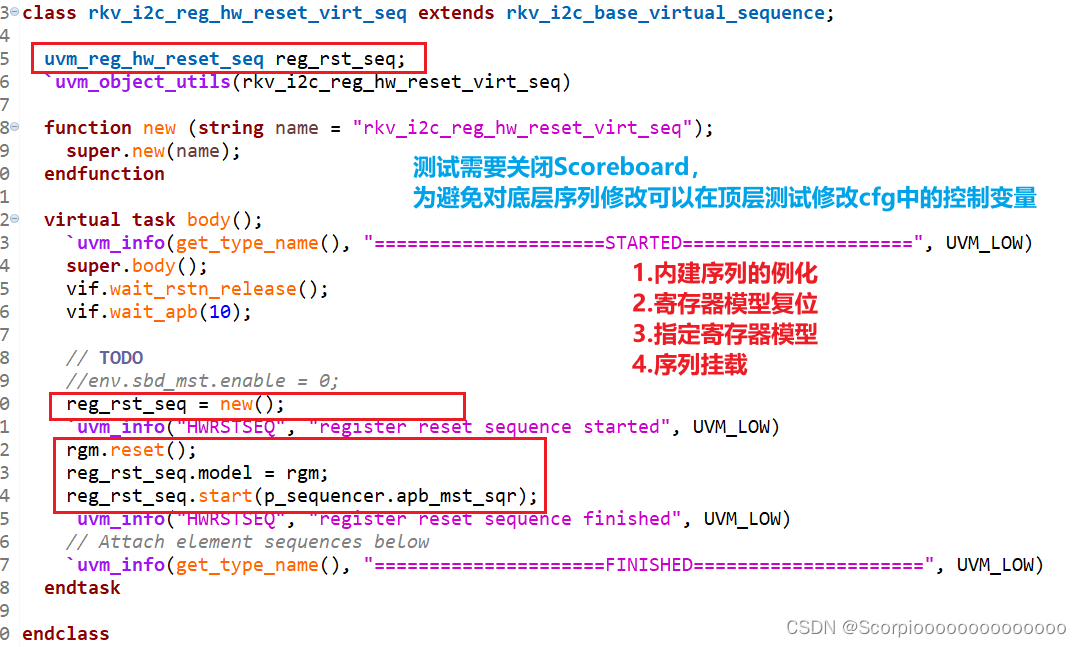

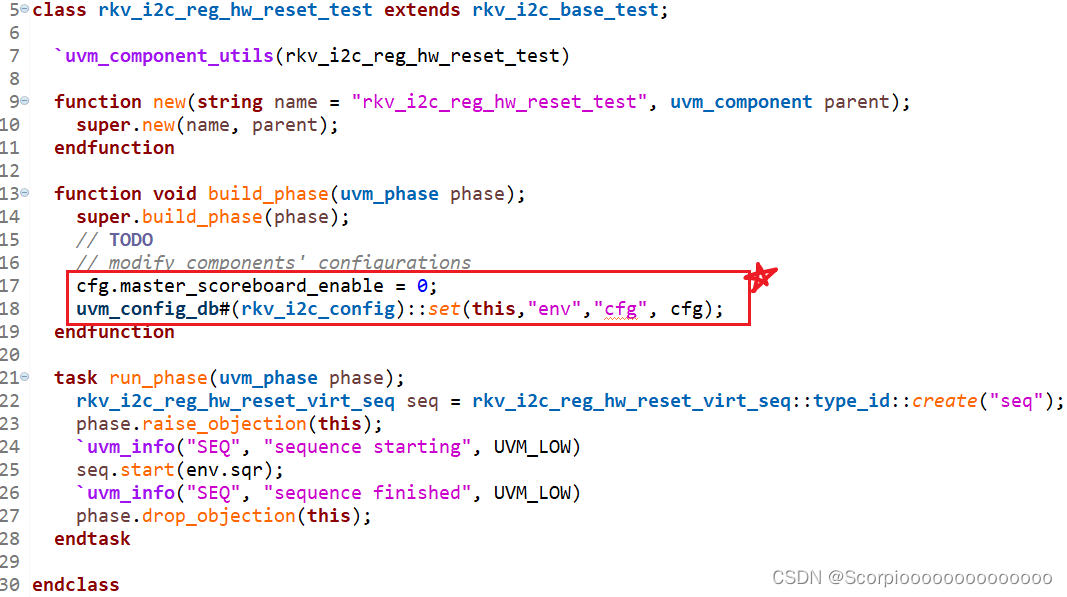

1. rkv_i2c_reg_hw_reset_seq

测试目的:内建序列是否可以正常使用

代码

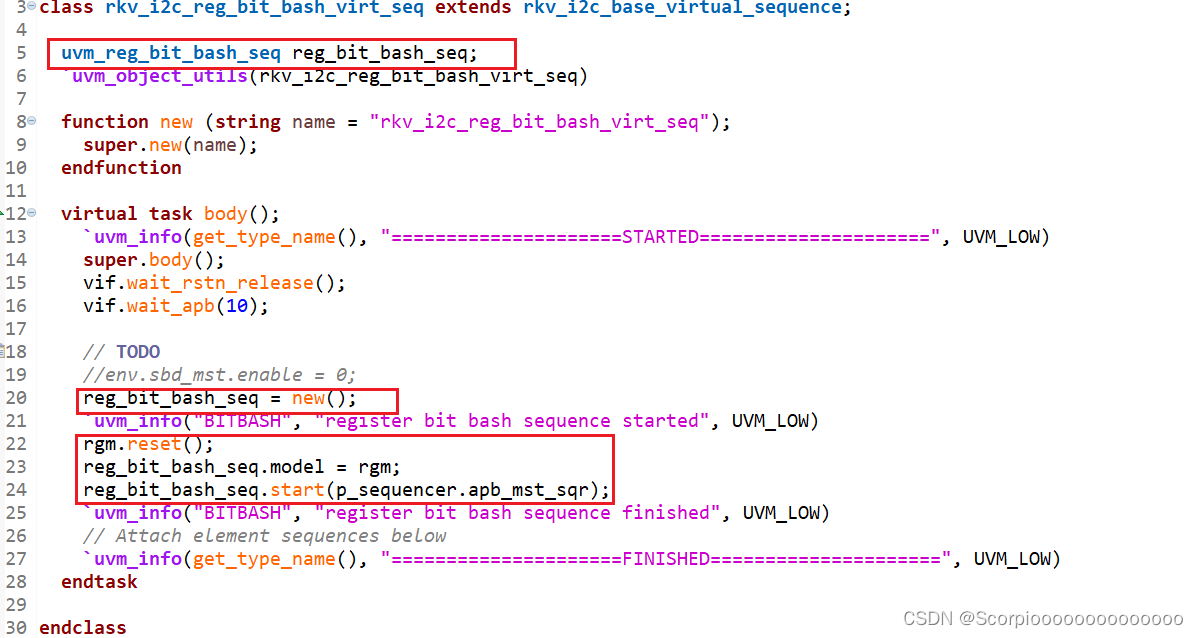

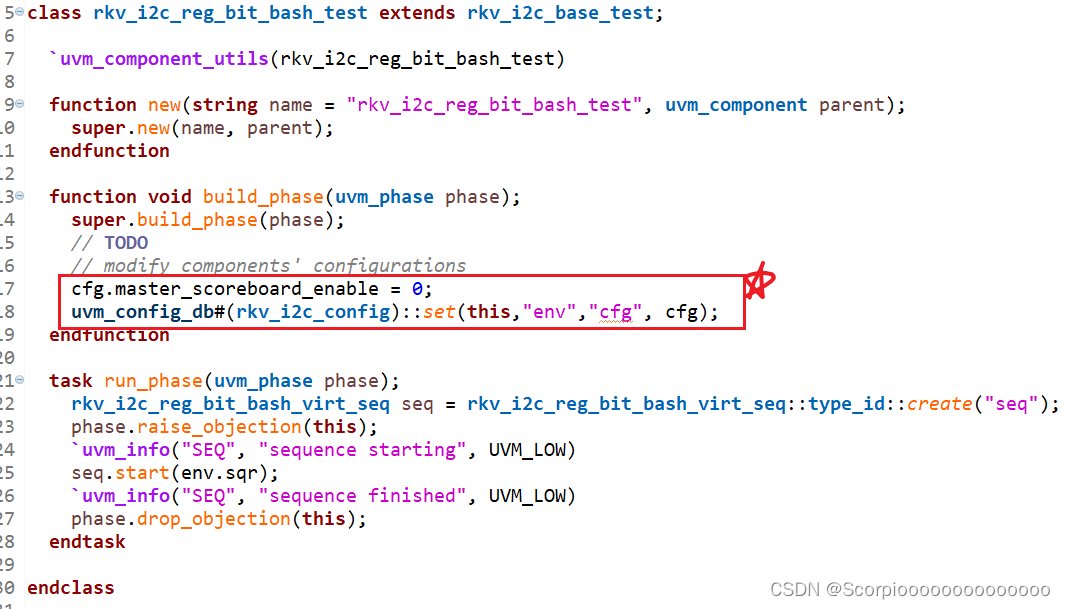

2. rkv_i2c_reg_bit_bash_seq

测试目的:内建序列是否可以正常使用

代码

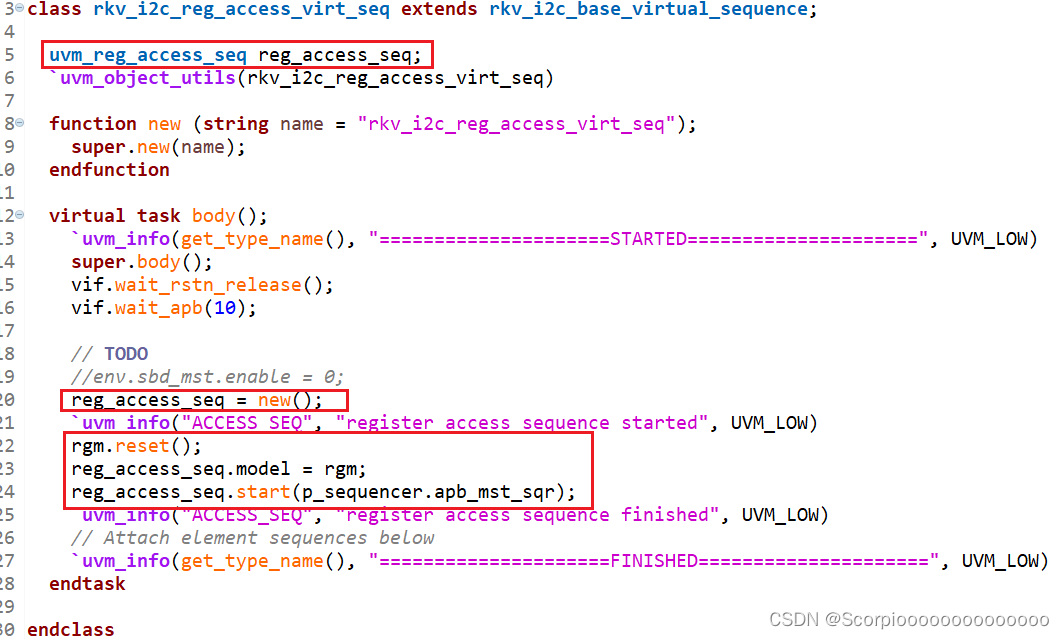

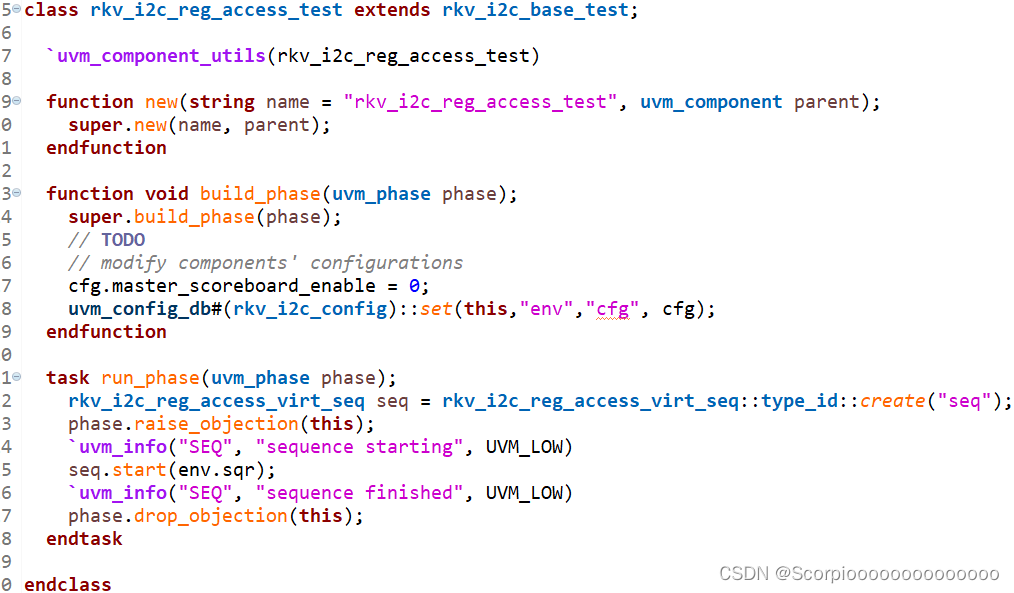

3. rkv_i2c_reg_access_seq

测试目的:内建序列是否可以正常使用

代码

四、自定义测试

1. 中断测试序列

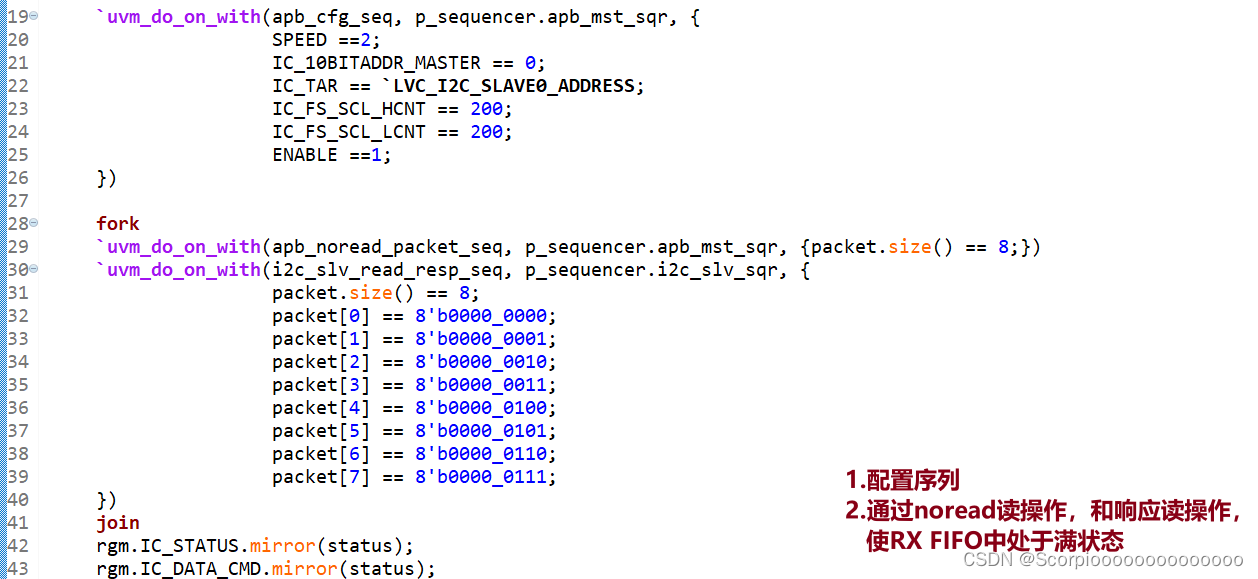

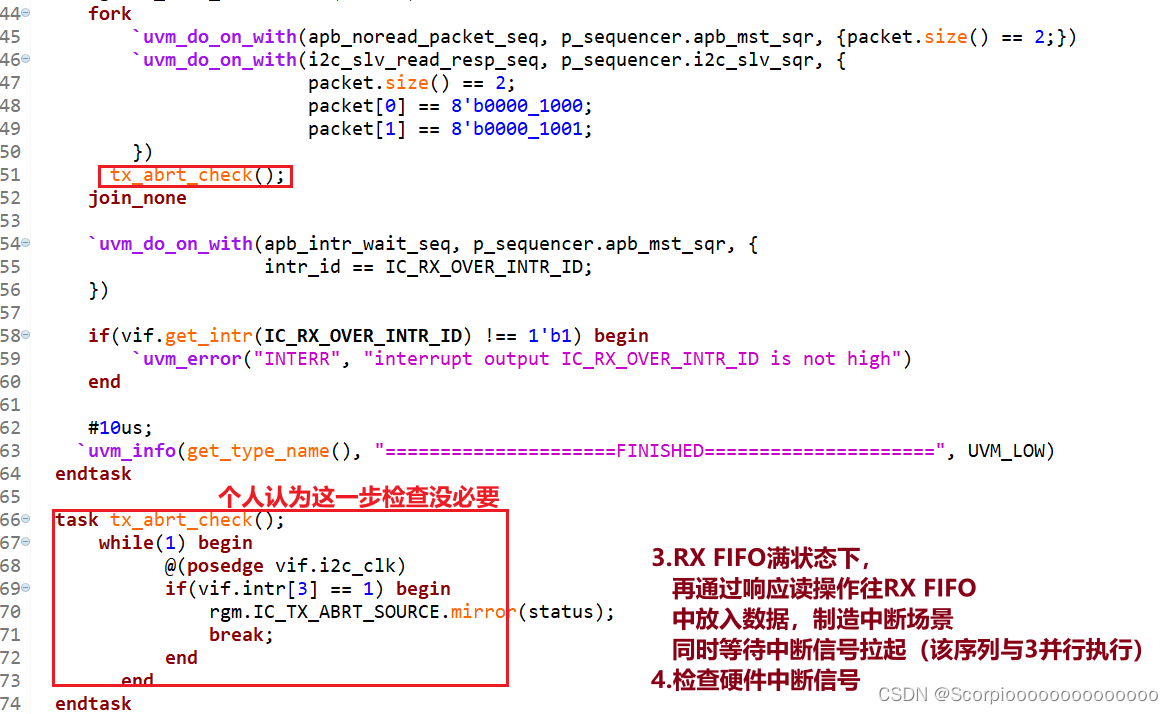

rkv_i2c_master_rx_over_intr_virt_seq

测试目的:触发rx_over中断

中断描述:根据寄存器IC_RAW_INTR_STAT[1]描述当RX FIFO中的数据超过buffer-depth时,再据需往里面填充数据后就会触发RX_OVER中断

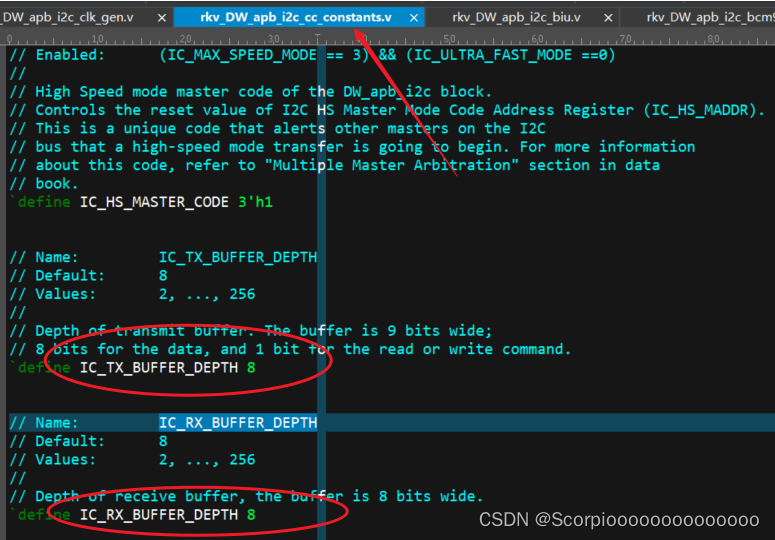

通过设计文件找到定义的buffer-depth

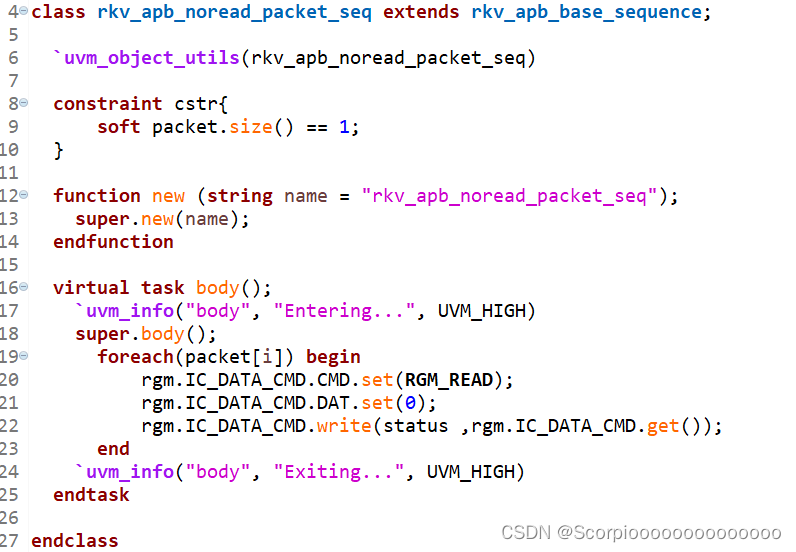

rkv_aob_noread_packet_seq正常读取操作下,RX FIFO不会超过定义的深度,我们需要一个不读回数据的读操作序列,只发送读命令而不读取RX FIFO数据,下面是自定义的直接发送读取命令,不做RX FIFO 检查和读取数据的序列

-

代码

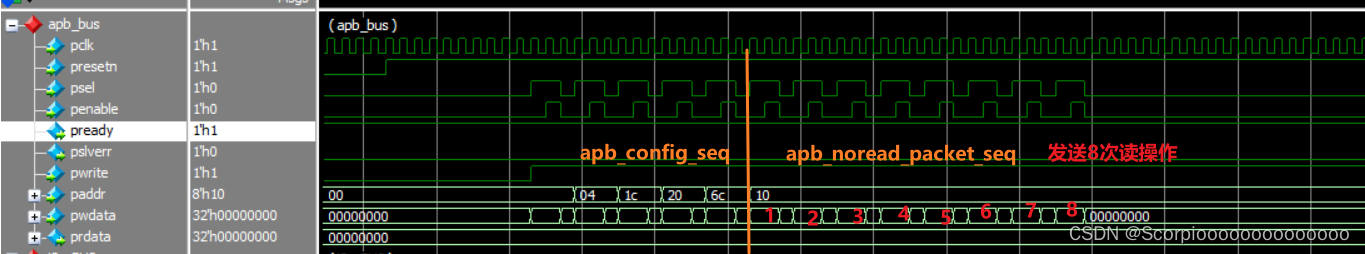

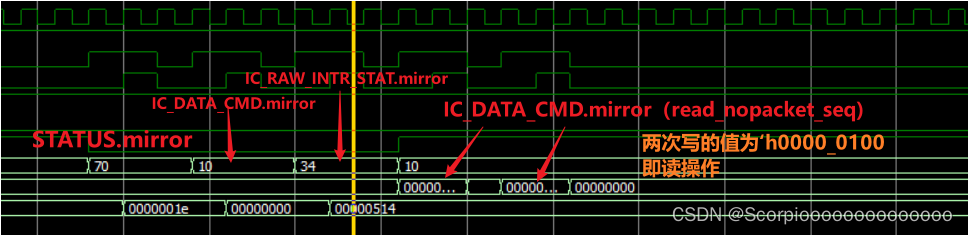

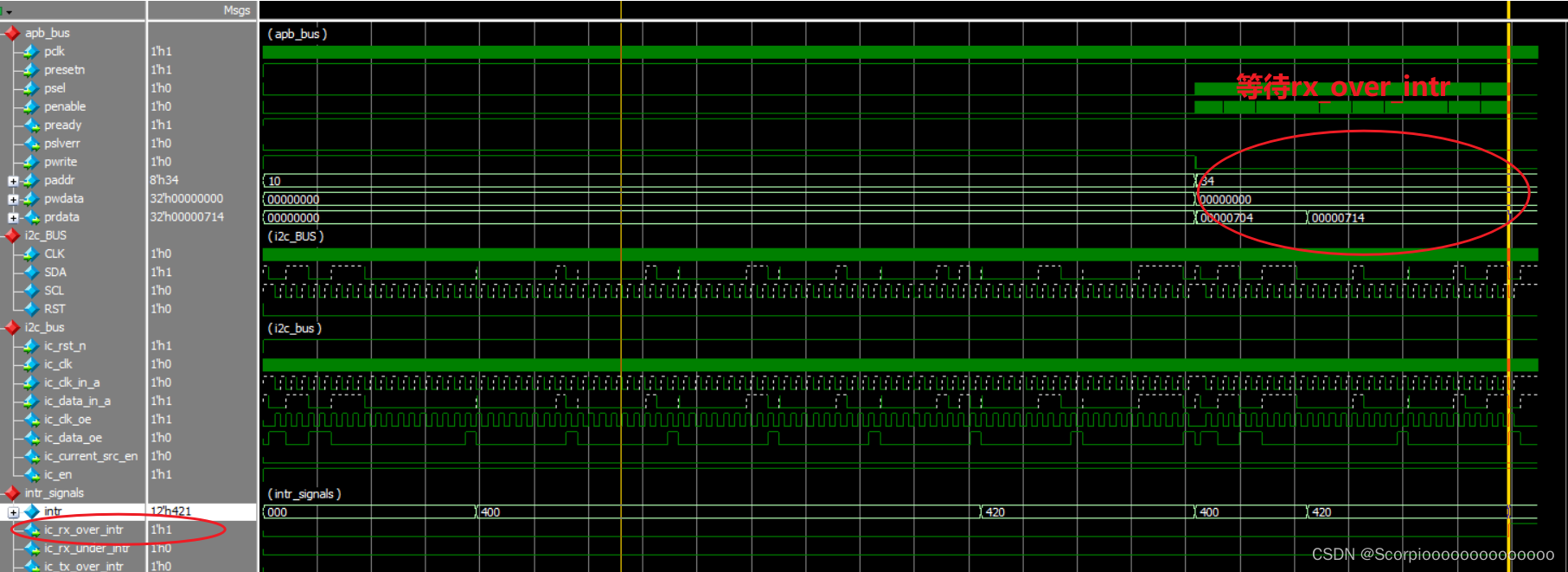

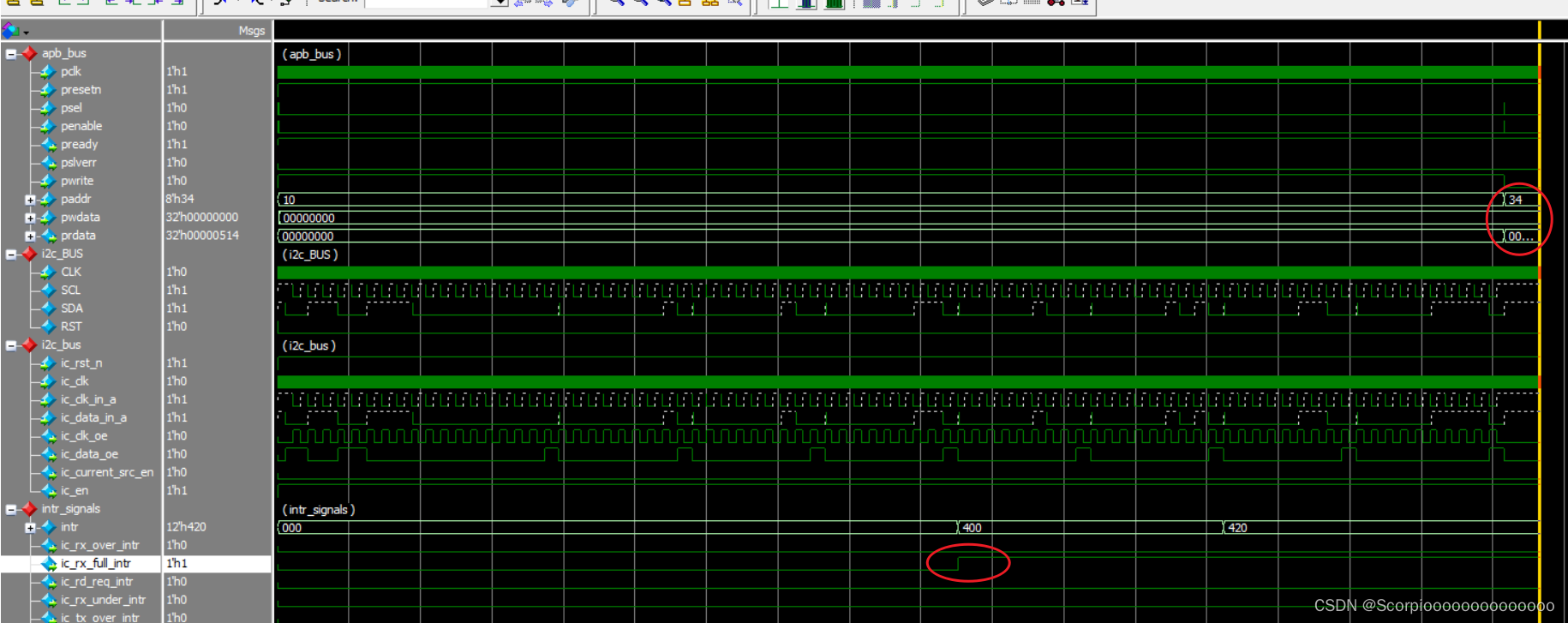

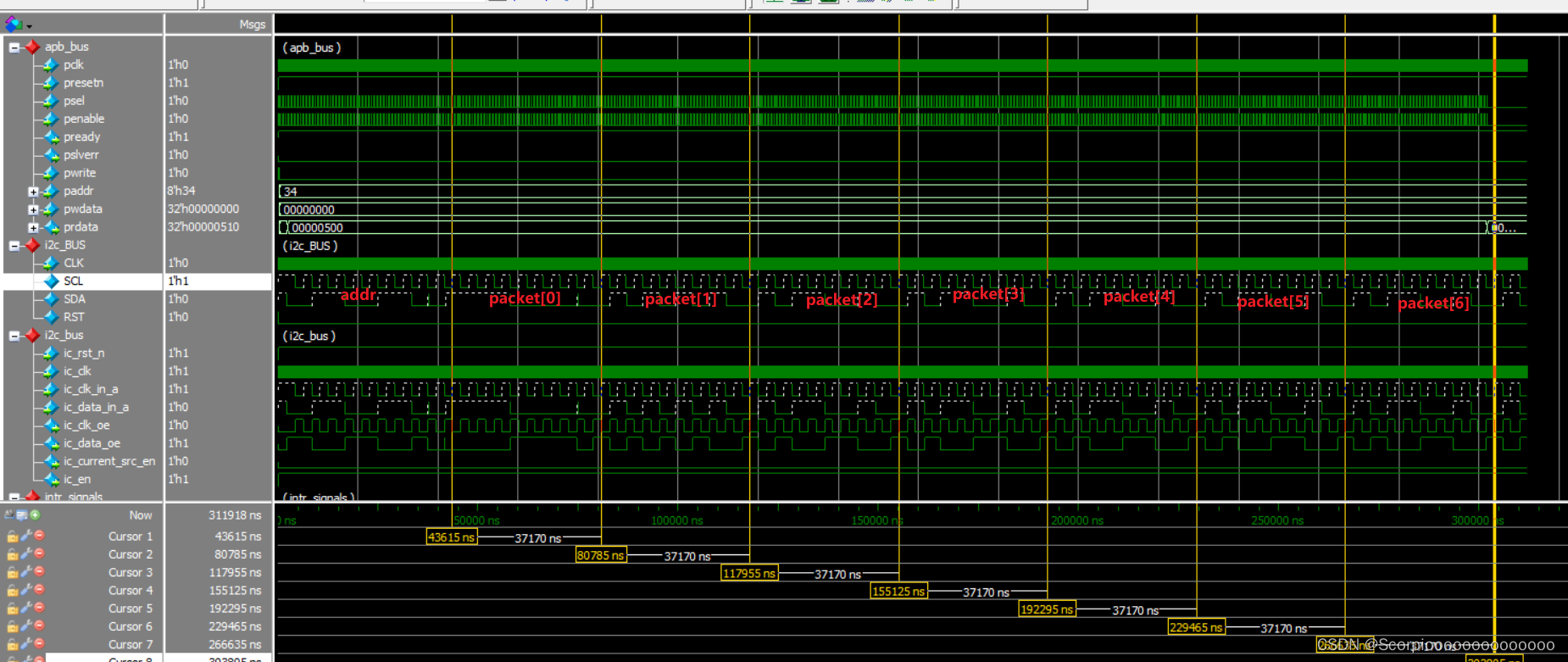

波形如下

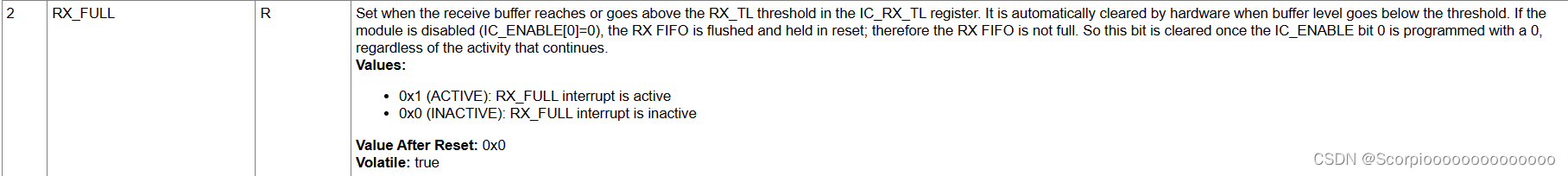

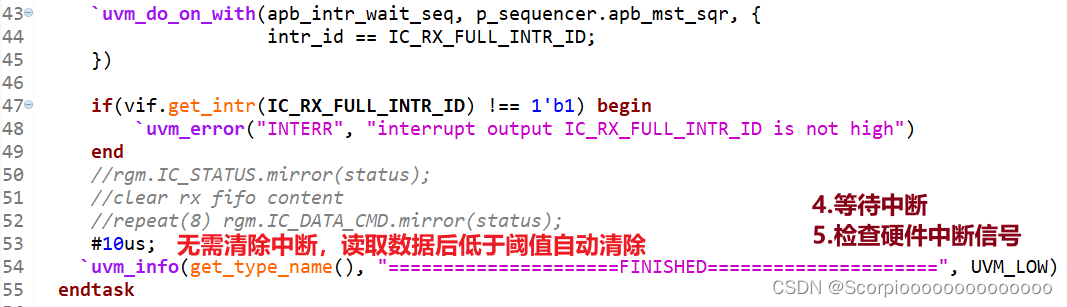

rkv_i2c_master_rx_full_intr_virt_seq

测试目的:触发rx_full中断

中断描述:根据寄存器IC_RAW_INTR_STAT[2]描述当RX FIFO中的数据超过IC_RX_TL寄存器设置的阈值后就会触发RX_FULL中断

代码

波形如下

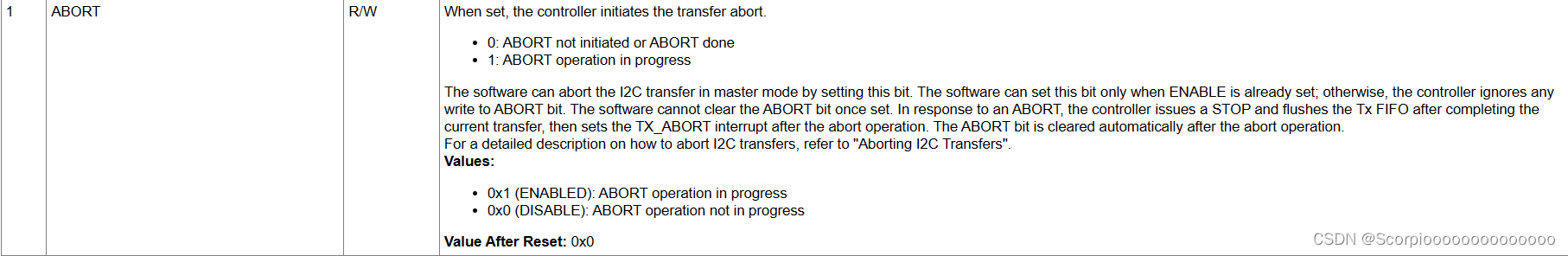

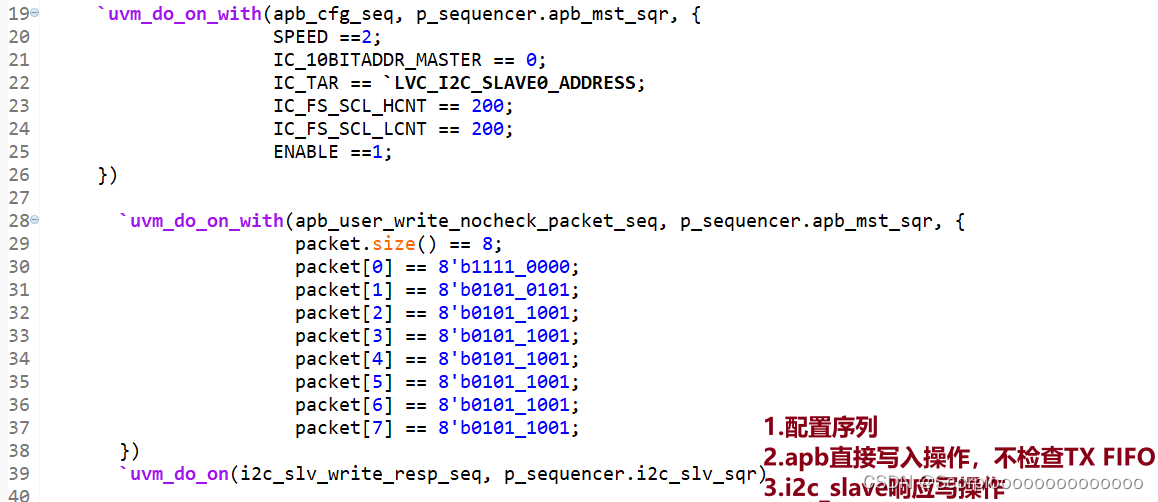

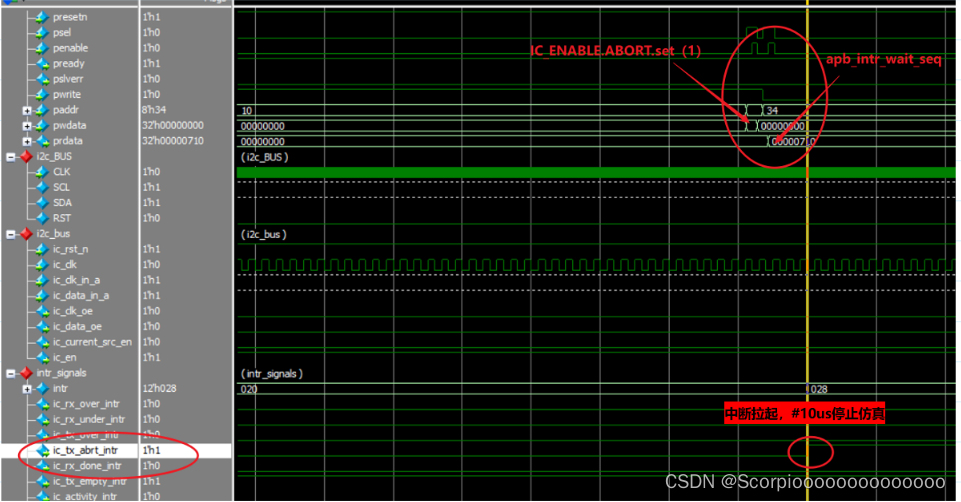

rkv_i2c_master_tx_abrt_intr_virt_seq

测试目的:触发tx_abrt中断

中断描述:根据寄存器IC_ENABLE[1]描述当该位设置为1时发生传输终止,且一旦发生控制器会发出STOP条件并在完成当前传输后清空TX FIFO完成上面的操作后会自动清除ABORT位并设置TX ABRT中断。

代码

波形如下

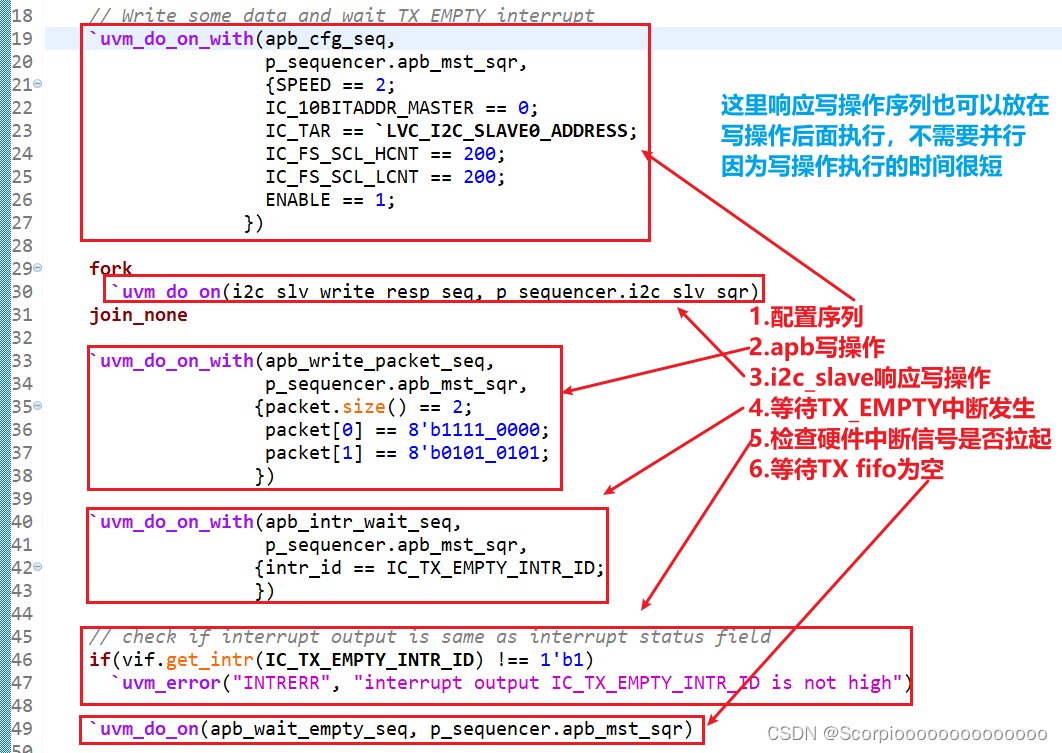

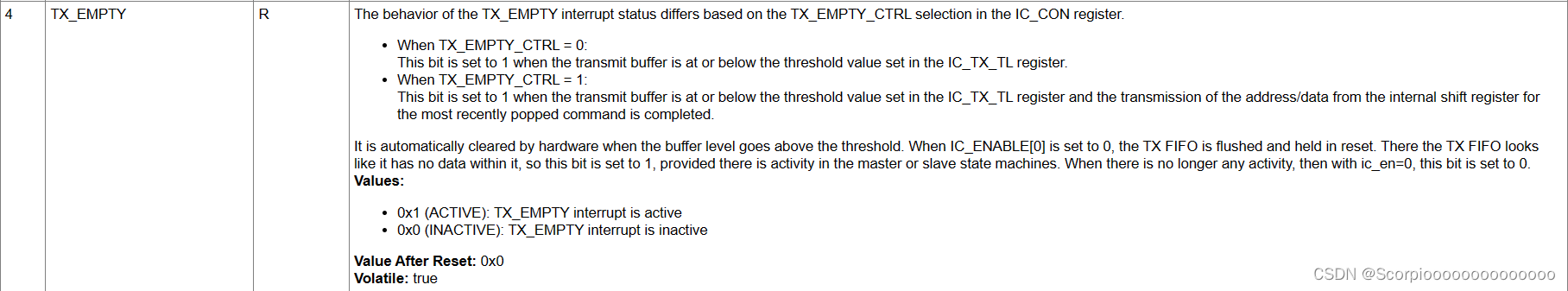

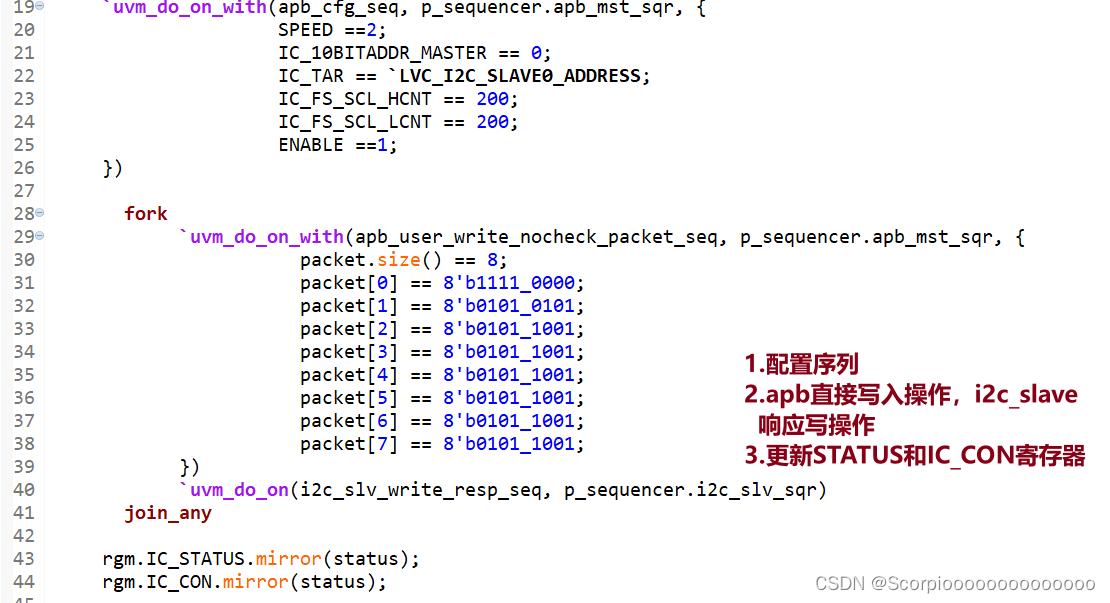

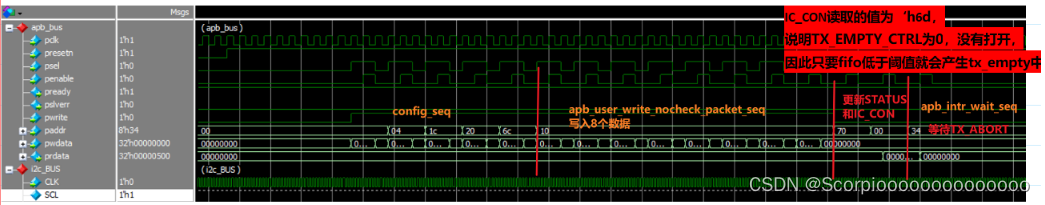

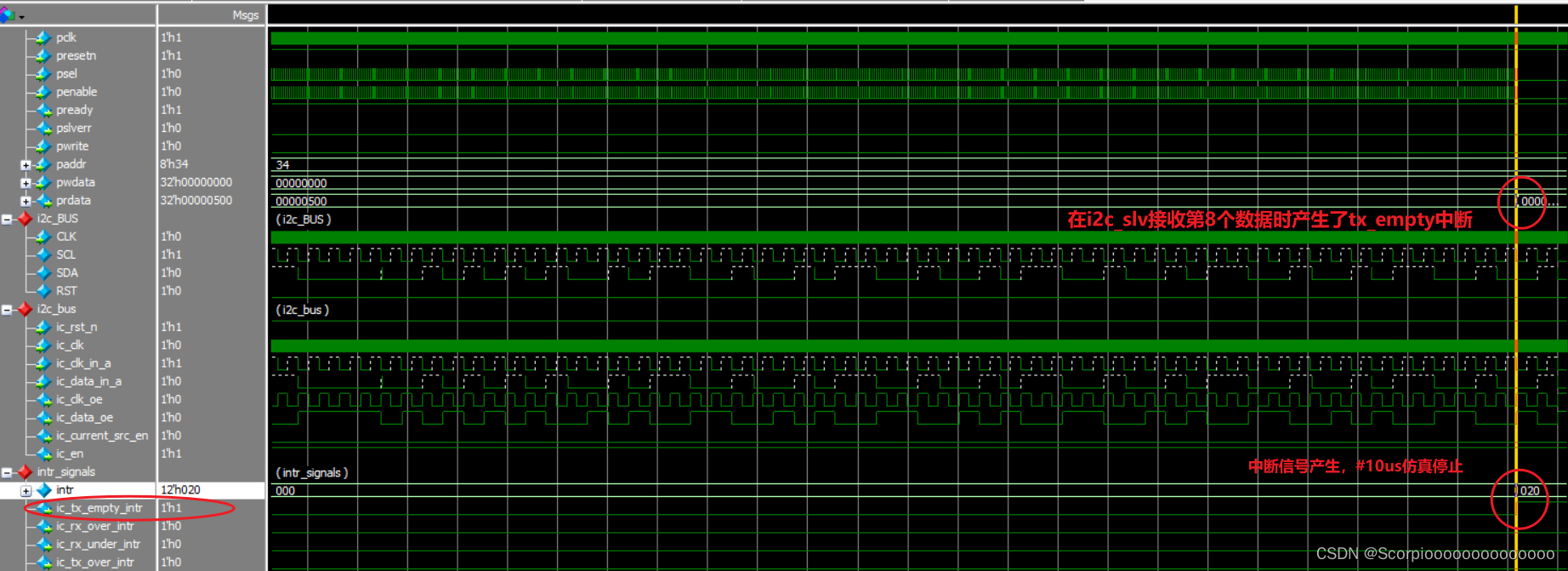

rkv_i2c_master_tx_empty_intr_virt_seq

测试目的:触发tx_empty中断

中断描述:根据寄存器IC_RAW_INTR_STAT[4]描述当该位受到 IC_CON_TX_EMPTY_CTRL位控制

当TX_EMPTY_CTRL=0:buffer低于阈值会设置为1,触发中断

当TX_EMPTY_CTRL=1:buffer低于阈值且 TX shift完成数据传输,触发中断

- TX_EMPTY的触发比较简单,只要低于阈值就会触发,因此正常写入即可出现该中断。

代码

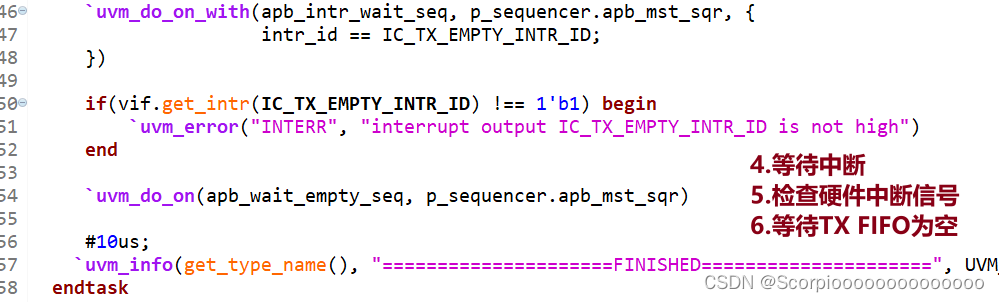

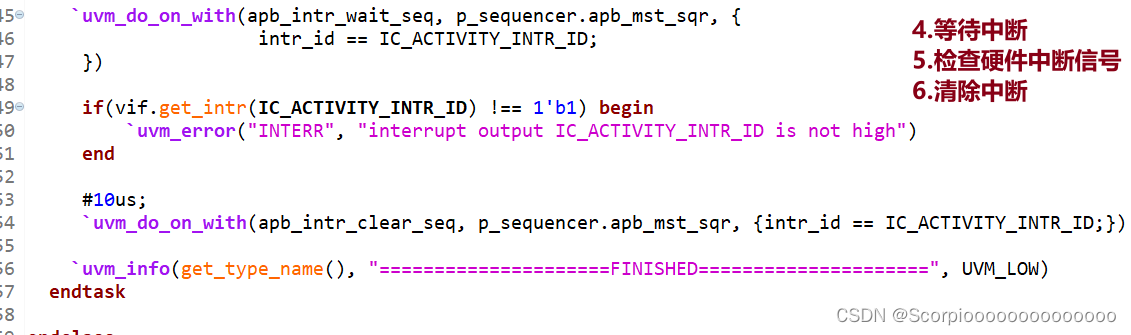

rkv_i2c_master_activity_intr_output_virt_seq

测试目的:触发activity中断

中断描述:根据IC_INTR_MASK[8]描述,默认情况下ACTIVITY中断是被屏蔽的,因此只需要打开即刻触发该中断

代码

波形如下

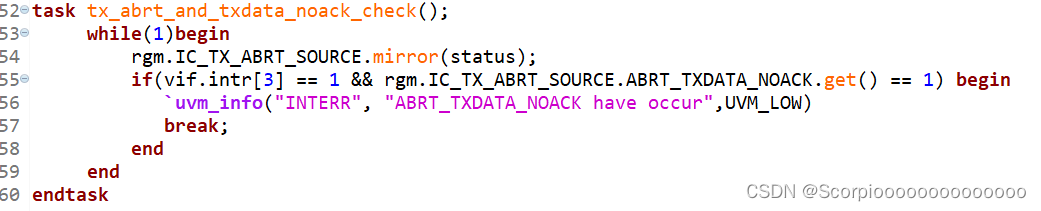

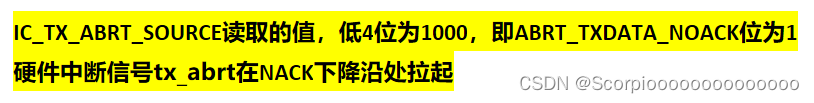

2.tx_abort_source测试序列

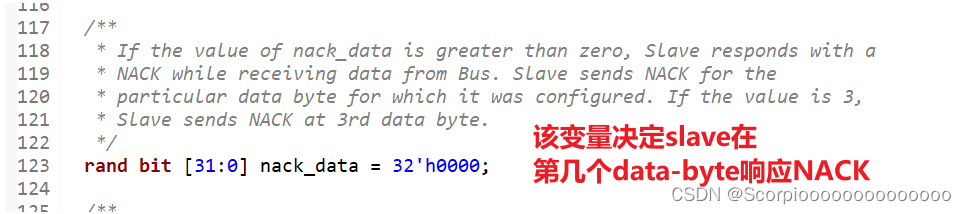

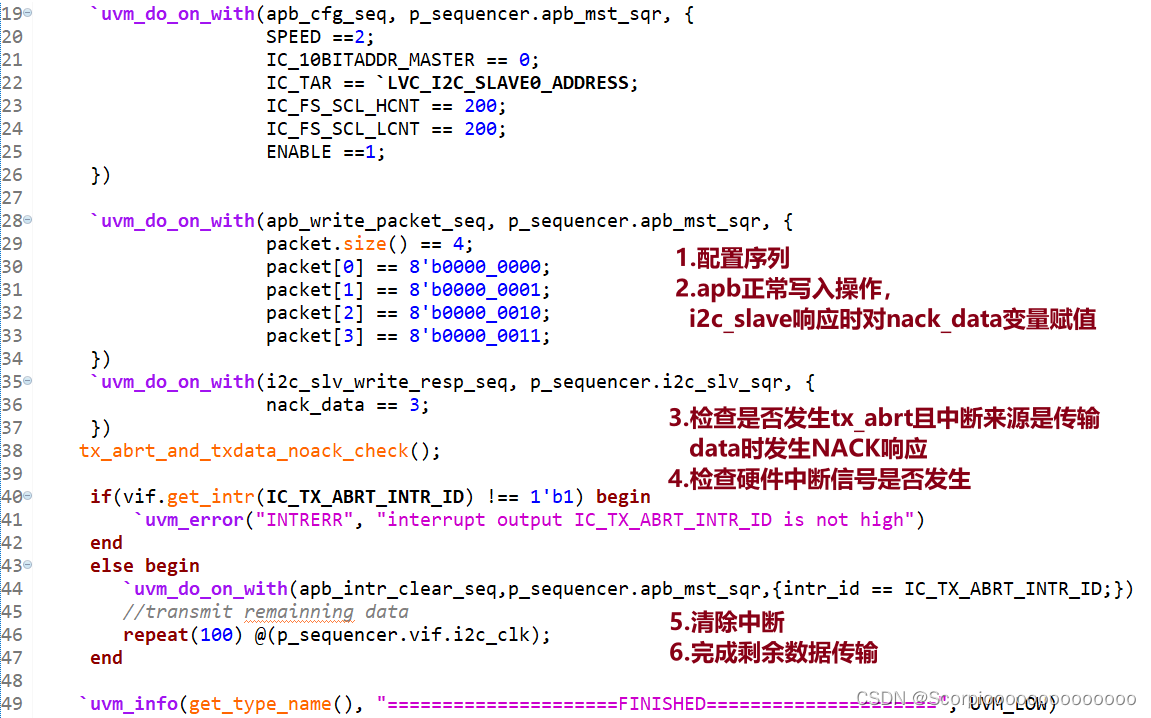

rkv_i2c_master_abrt_txdata_noack_virt_seq

测试目的:传输数据时响应NACK造成传输中断

中断描述:在lvc_i2c_slave_transaction中定义了变量nack_data,该变量决定了slave在第几个data-byte响应NACK信号

代码

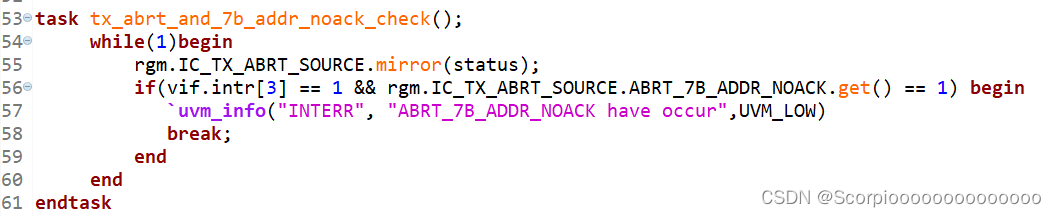

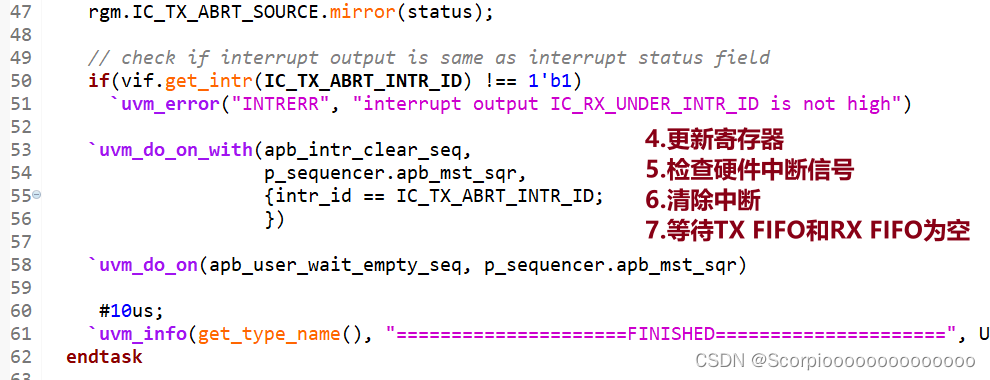

【注】get()方法可前门访问寄存器域值,但获得的是寄存器模型的期望值因此使用前一定要使用mirror()更新。

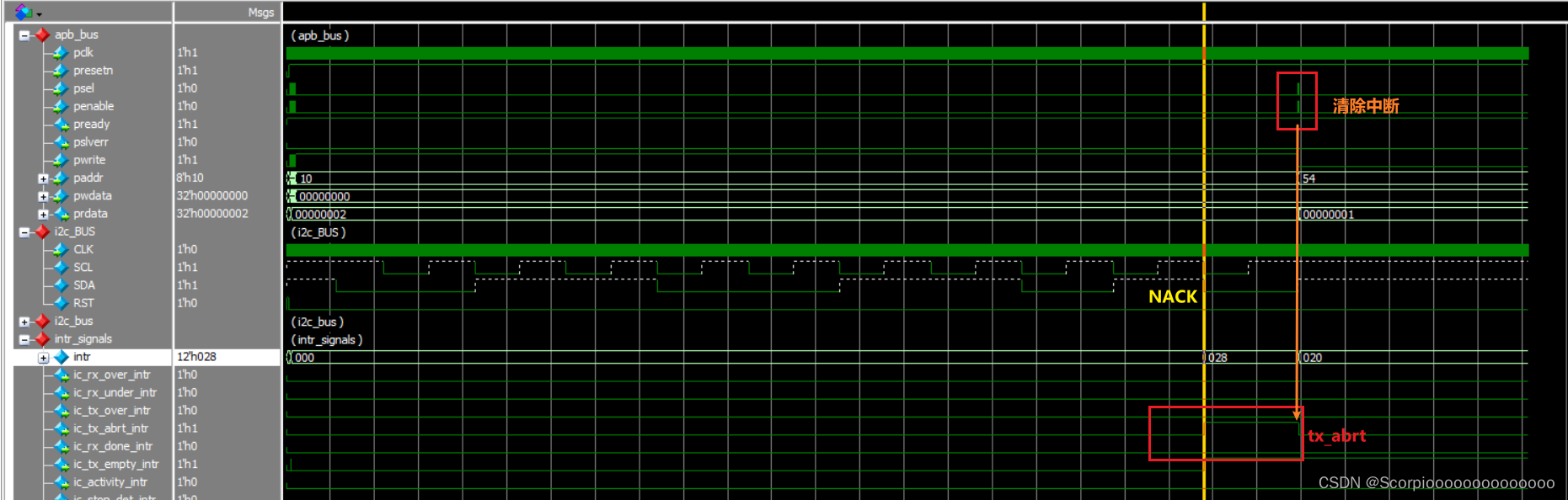

波形

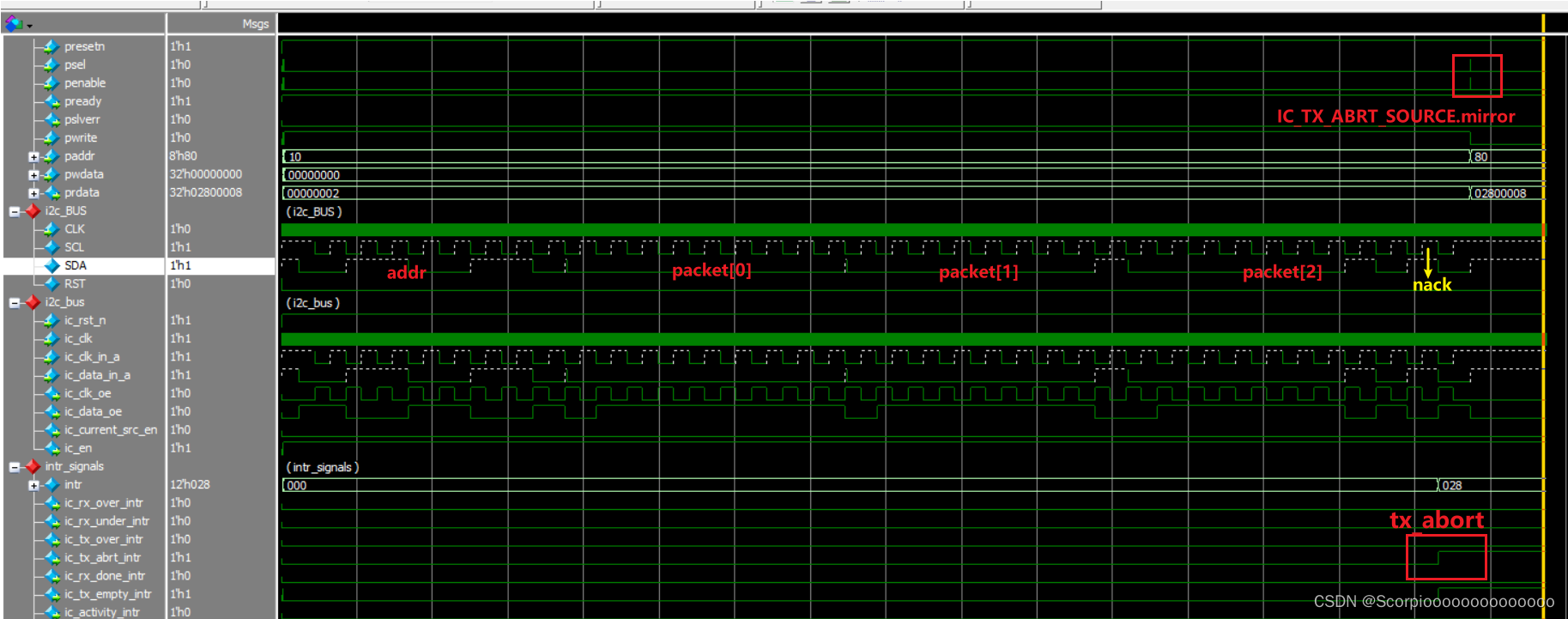

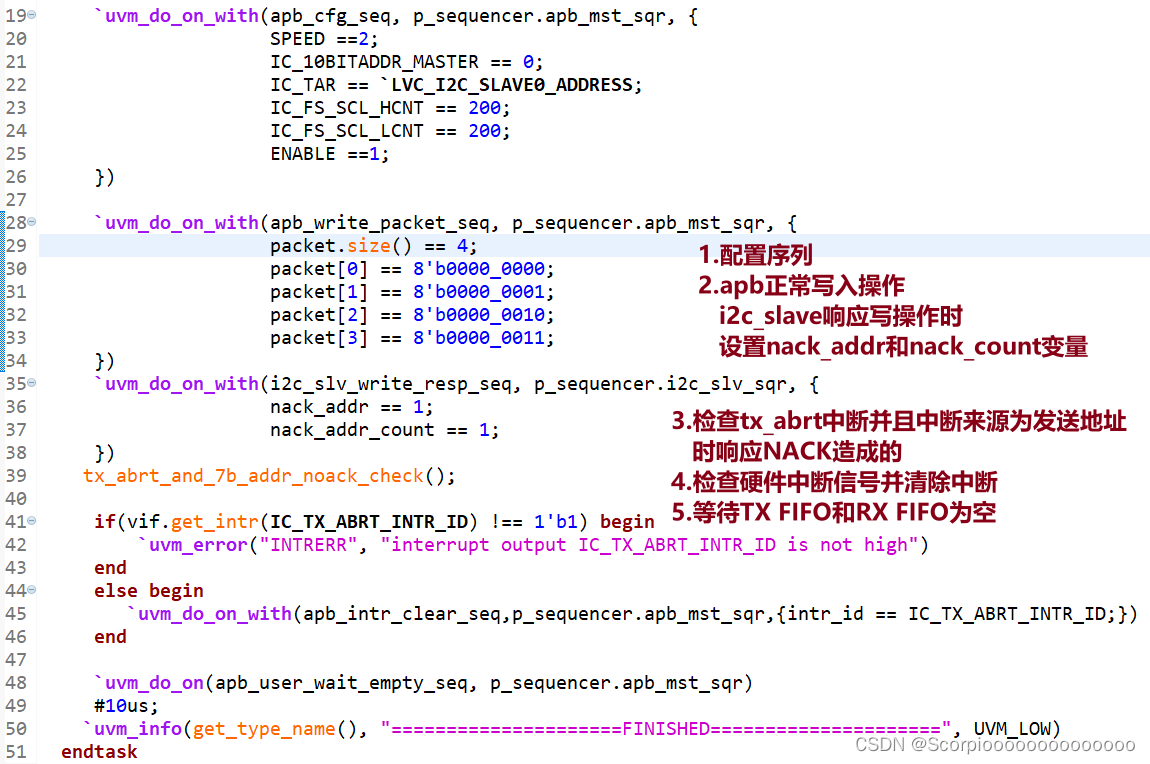

rkv_i2c_master_abrt_7b_addr_nack_virt_seq

测试目的:传输7-bit地址时响应NACK造成传输中断,检查IC_TX_ABRT_SOURCE寄存器的ABRT_7B_ADDR_NACK位

中断描述:在lvc_i2c_slave_transaction中定义了变量nack_addr和nack_addr_count,该变量决定了slave在发送设备地址响应NACK信号

代码

波形

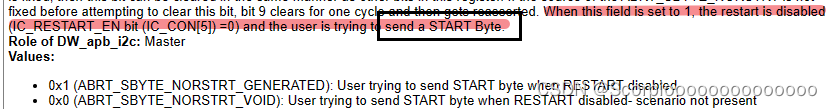

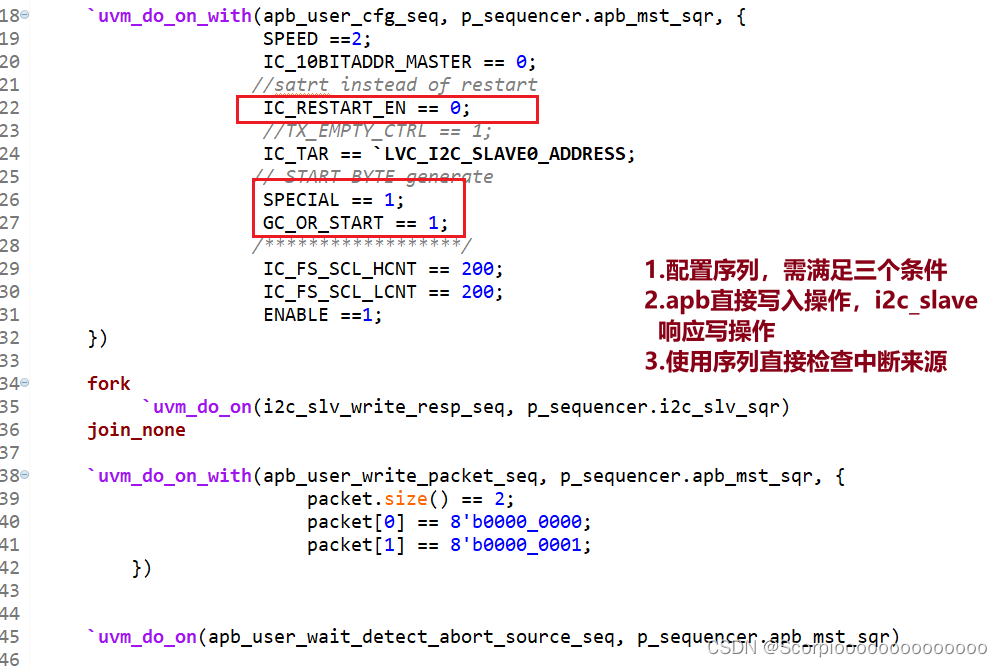

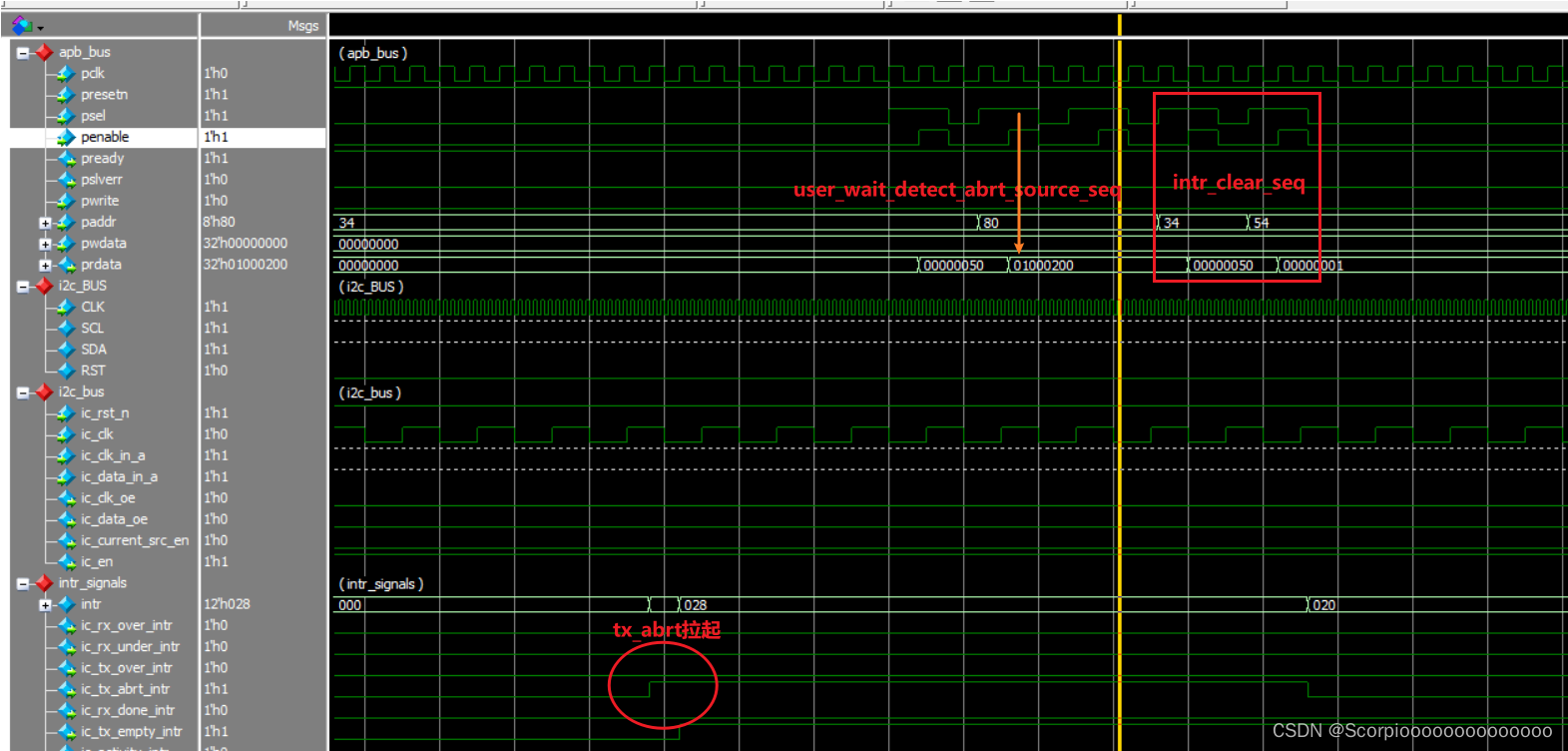

rkv_i2c_master_abrt_sbyte_norstrt_virt_seq

测试目的:检查IC_TX_ABRT_SOURCE寄存器的ABRT_SBTYE_NORSTRT

中断描述:IC_TX_ABRT_SOURCE寄存器描述在发送START字节时若IC_CON_IC_RESTART_EN关闭,则会触发该中断。

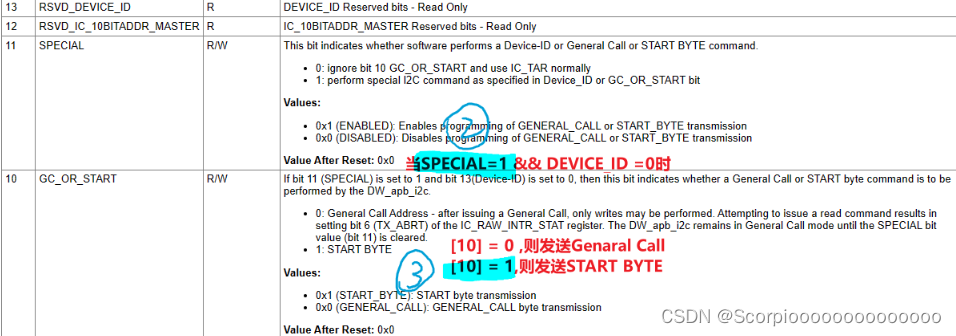

关于START字节的产生可以看IC_TAR寄存器:

也就是说中断发生的条件有三个:①IC_CON_IC_RESTART_EN = 0 ②IC_TAR_SPECIAL = 0 ③IC_TAR_GC_OR_START = 1

代码

波形

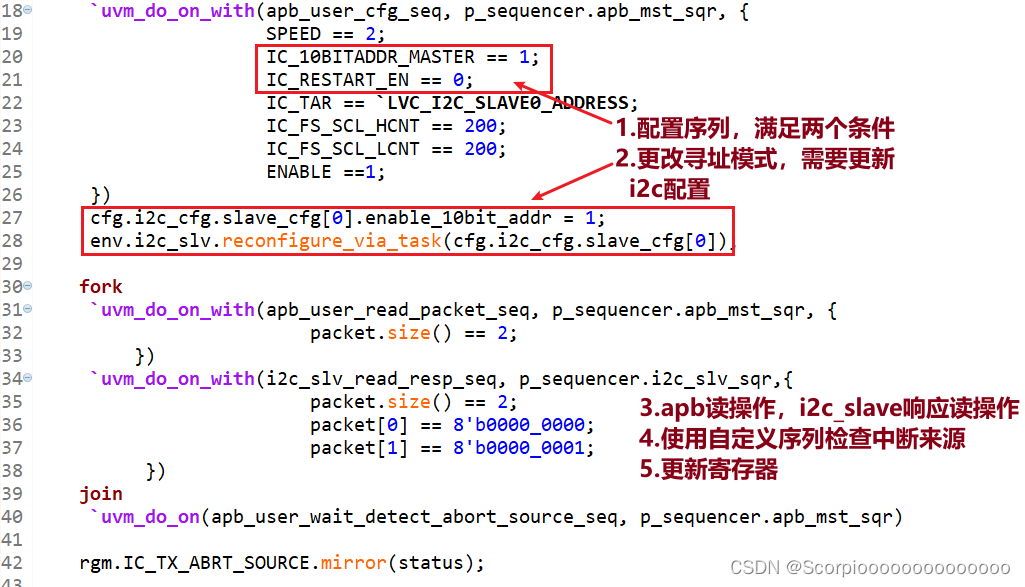

rkv_i2c_master_abrt_10b_rd_norstrt_virt_seq

测试目的:检查IC_TX_ABRT_SOURCE寄存器的ABRT_10B_RD_NORSTRT

中断描述:IC_TX_ABRT_SOURCE寄存器描述在发送读命令时若IC_CON_IC_RESTART_EN关闭,则会触发该中断。

代码

波形

3.speed测试序列

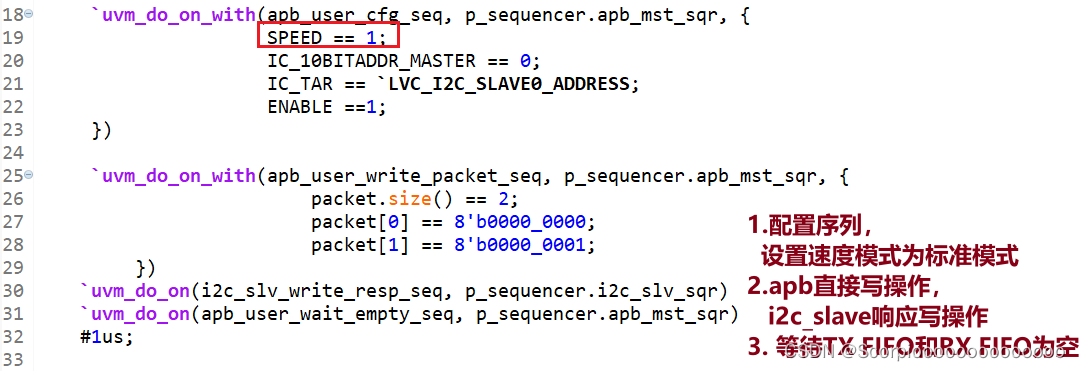

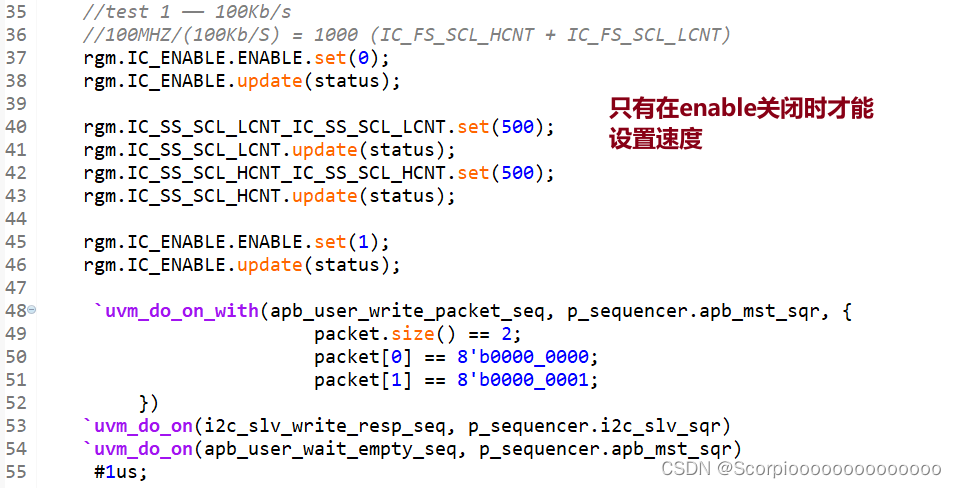

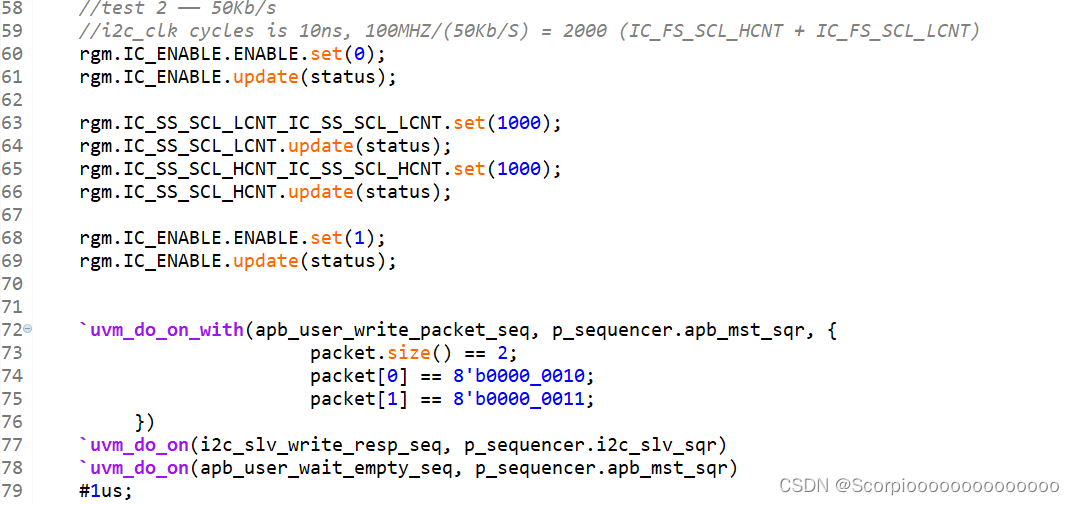

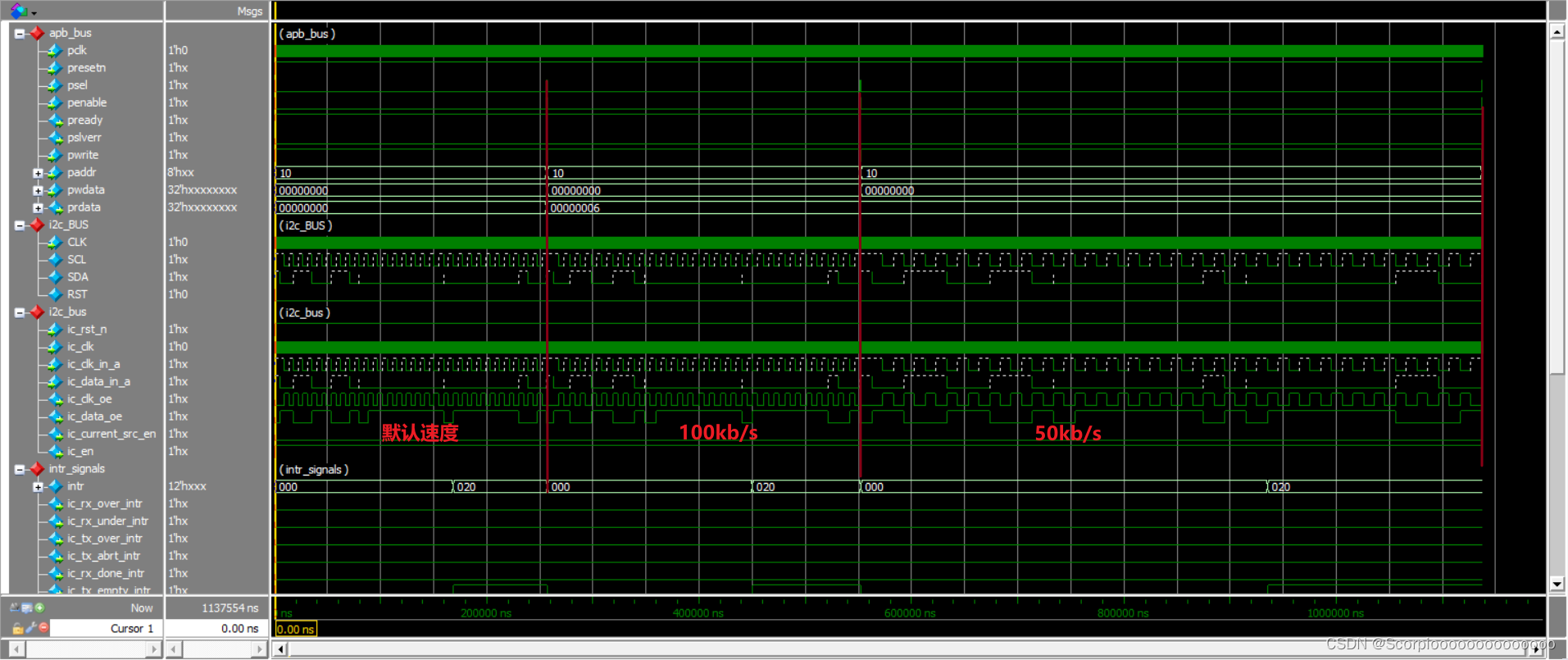

rkv_i2c_master_ss_cnt_virt_seq

测试目的:测试标准模式下的默认传输速度、100kb/s、50kb/s

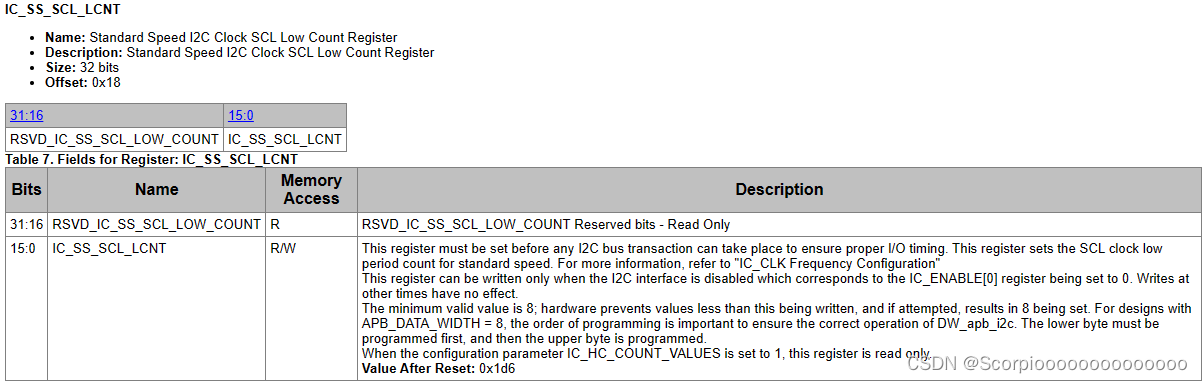

寄存器描述

代码:

波形

❓

寄存器描述中HCNT的复位值为0x190(400),LCNT的复位值为0x1d6(470),传输速度为100M/870 ≈114.9Kb/s,确实符合波形。

但违背该模式下的最高速度不太能理解。😒😒😒😒

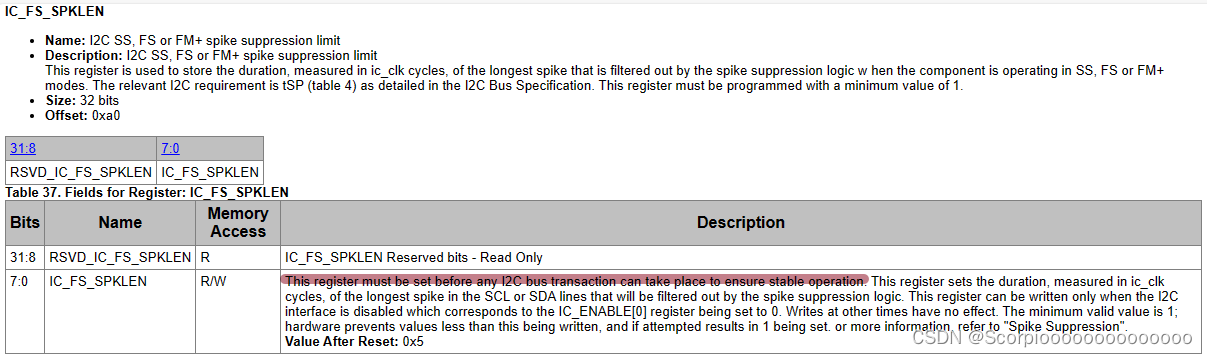

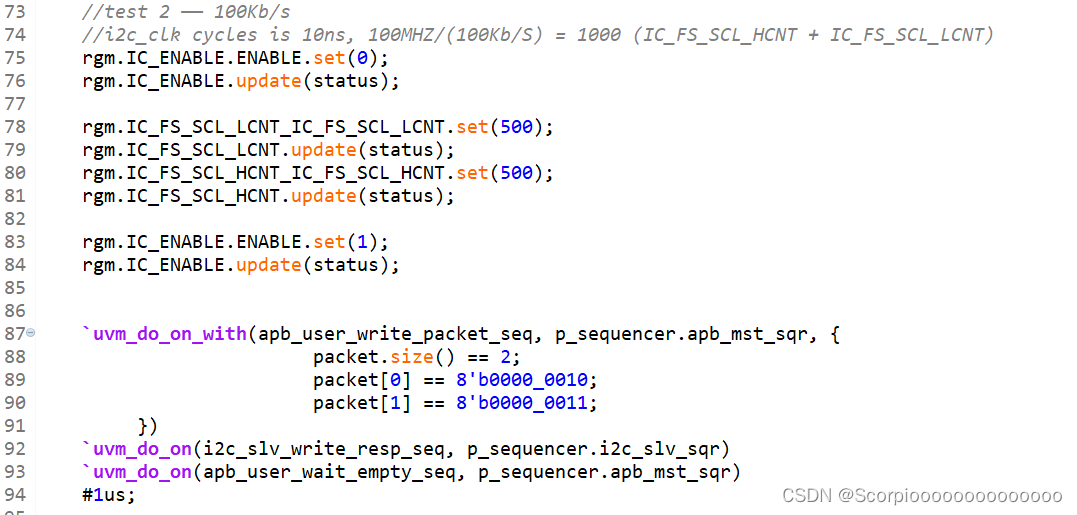

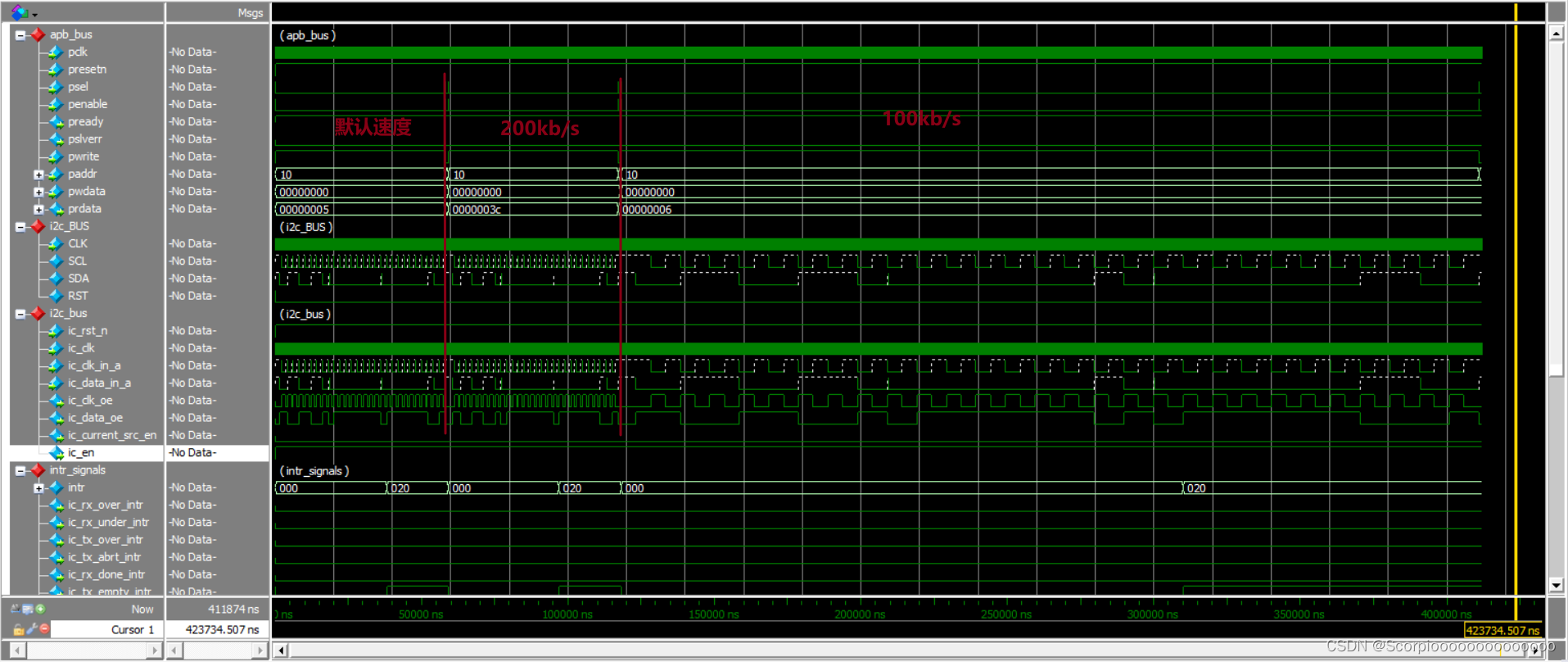

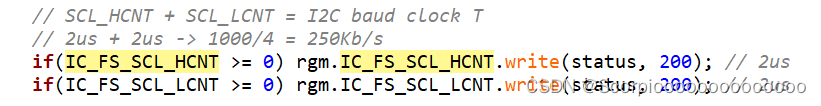

rkv_i2c_master_fs_cnt_virt_seq

测试目的:测试快速模式下的默认传输速度、200kb/s、100kb/s

寄存器描述:设置IC_FS_SPKLEN寄存器不知道是用来做啥的,没看懂

波形

HCNT的复位值为0x3c(60)和LCNT的复位值为0x82(130),传输速度为100M/190 ≈526Kb/s与波形不符。原因在于配置序列默认设置的传输速度为250Kb/s

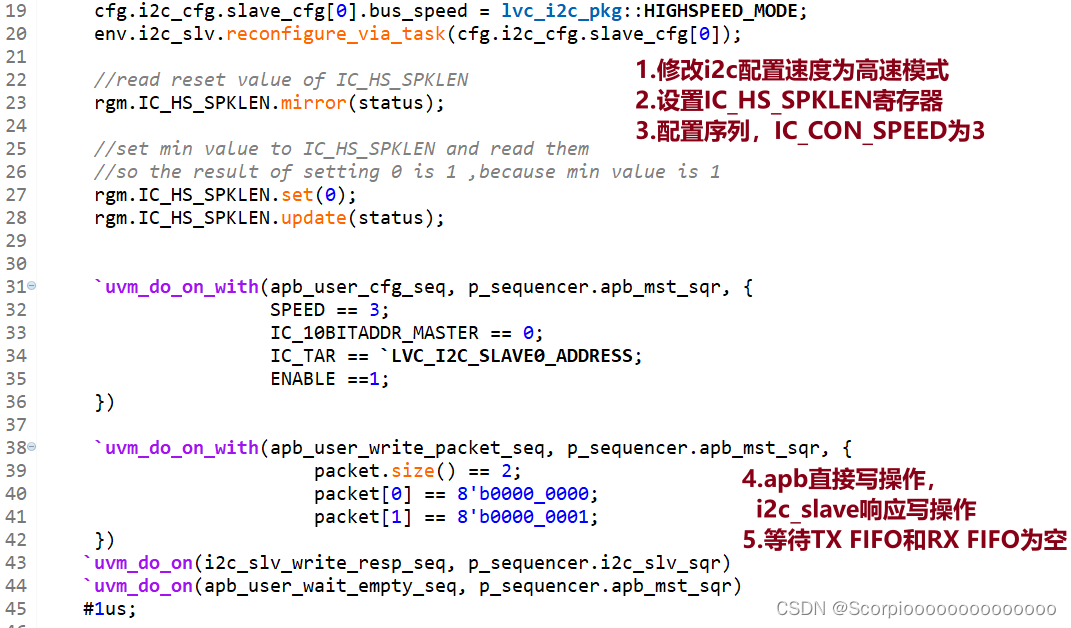

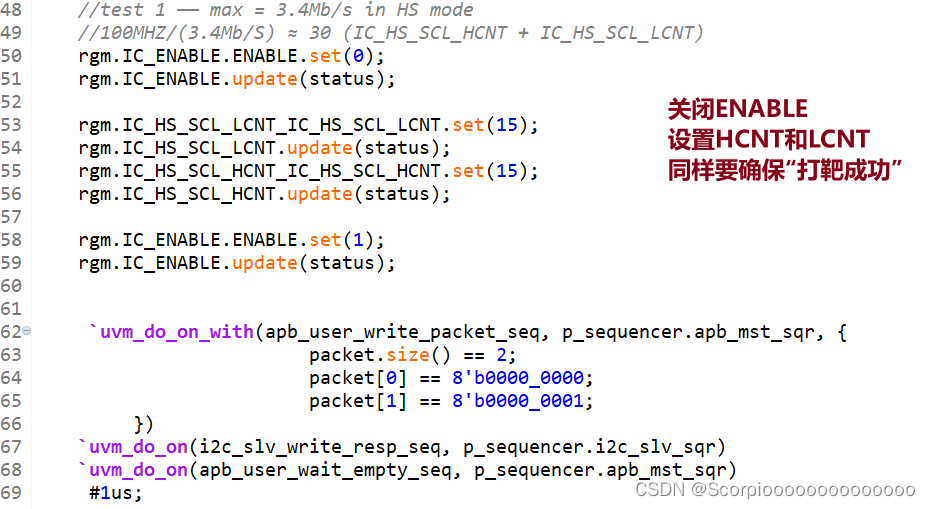

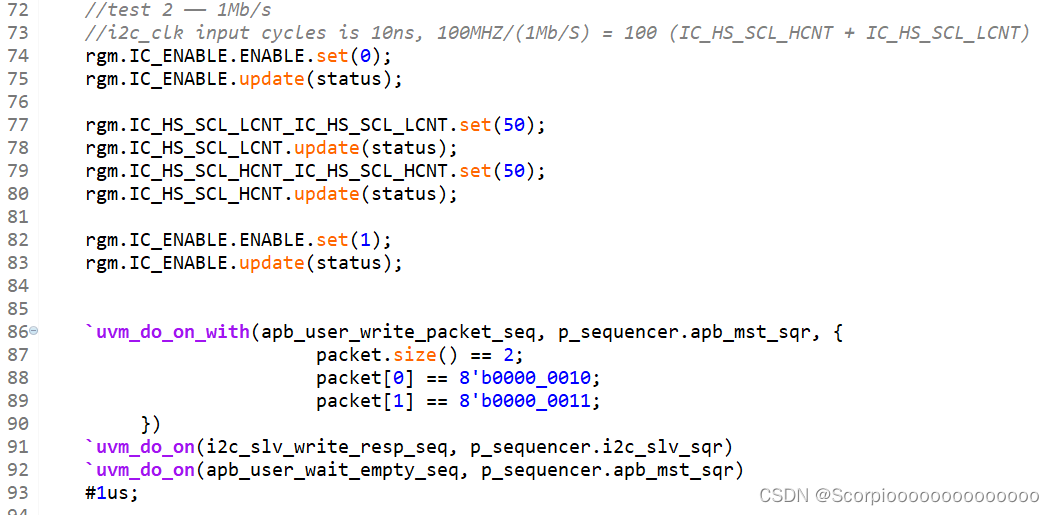

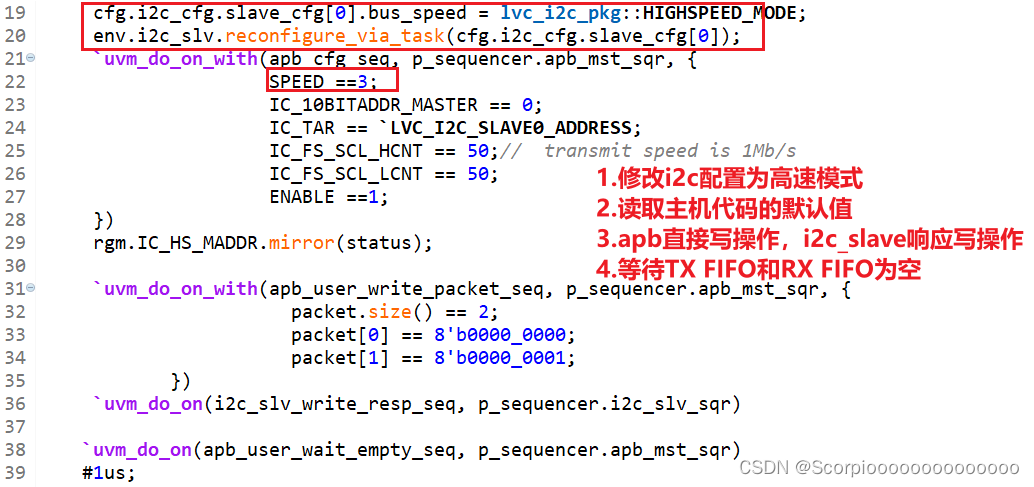

rkv_i2c_master_hs_cnt_virt_seq

测试目的:测试高速模式下的默认传输速度、3.4Mb/s、1Mb/s

寄存器描述:设置IC_HS_SPKLEN寄存器不知道是用来做啥的,没看懂

代码

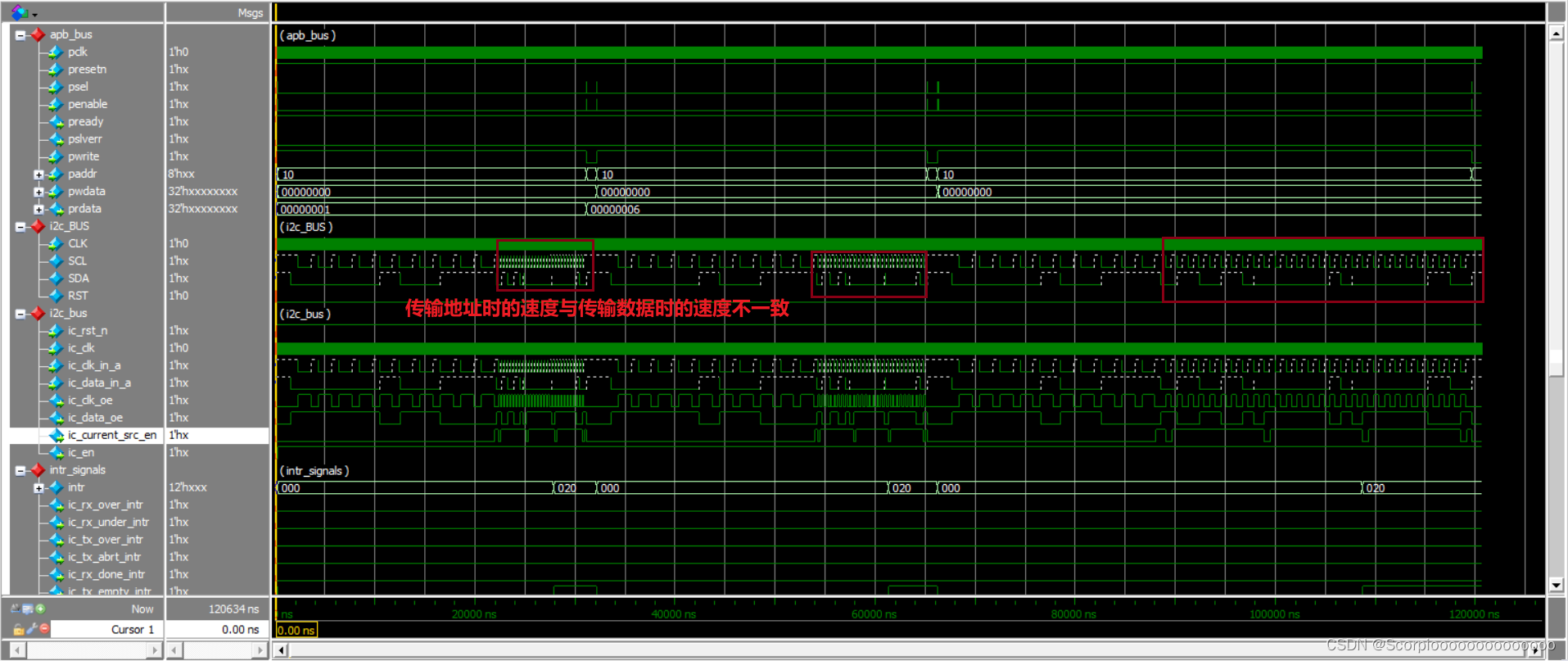

波形

❓为什么传输地址速度与传输数据速度不一致?

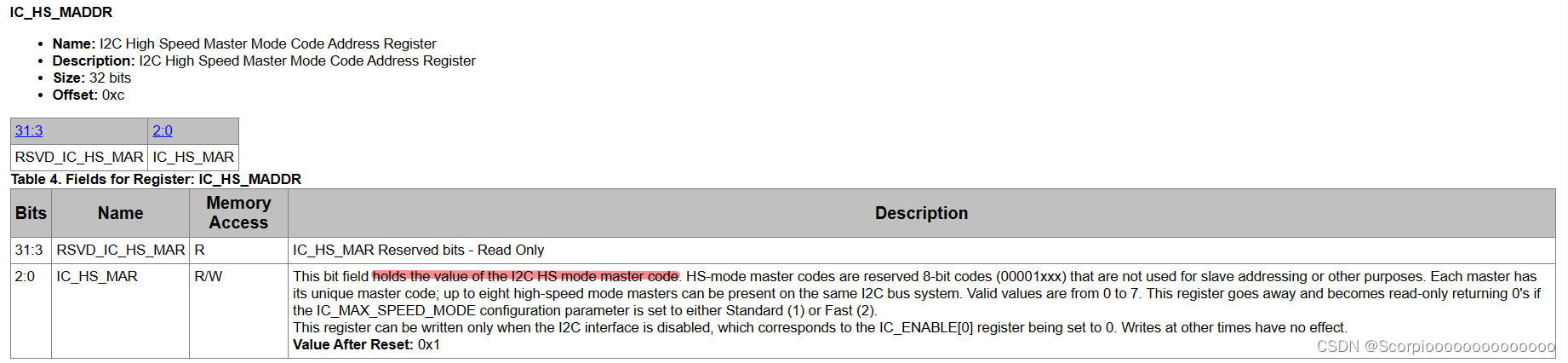

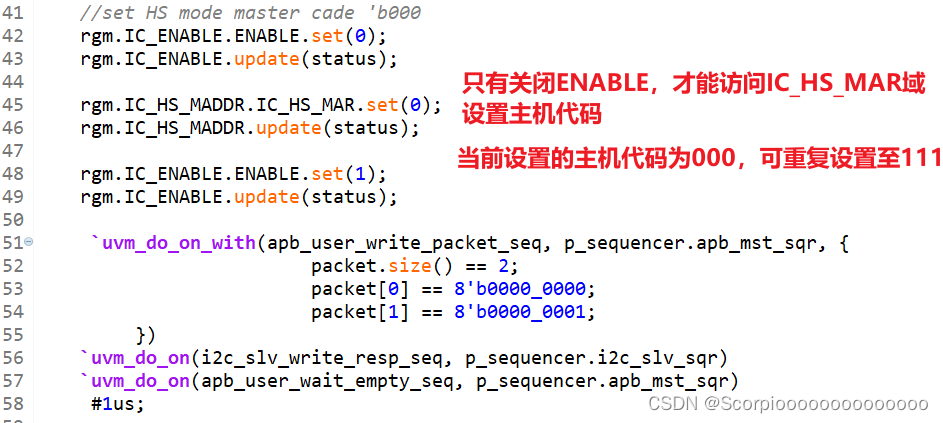

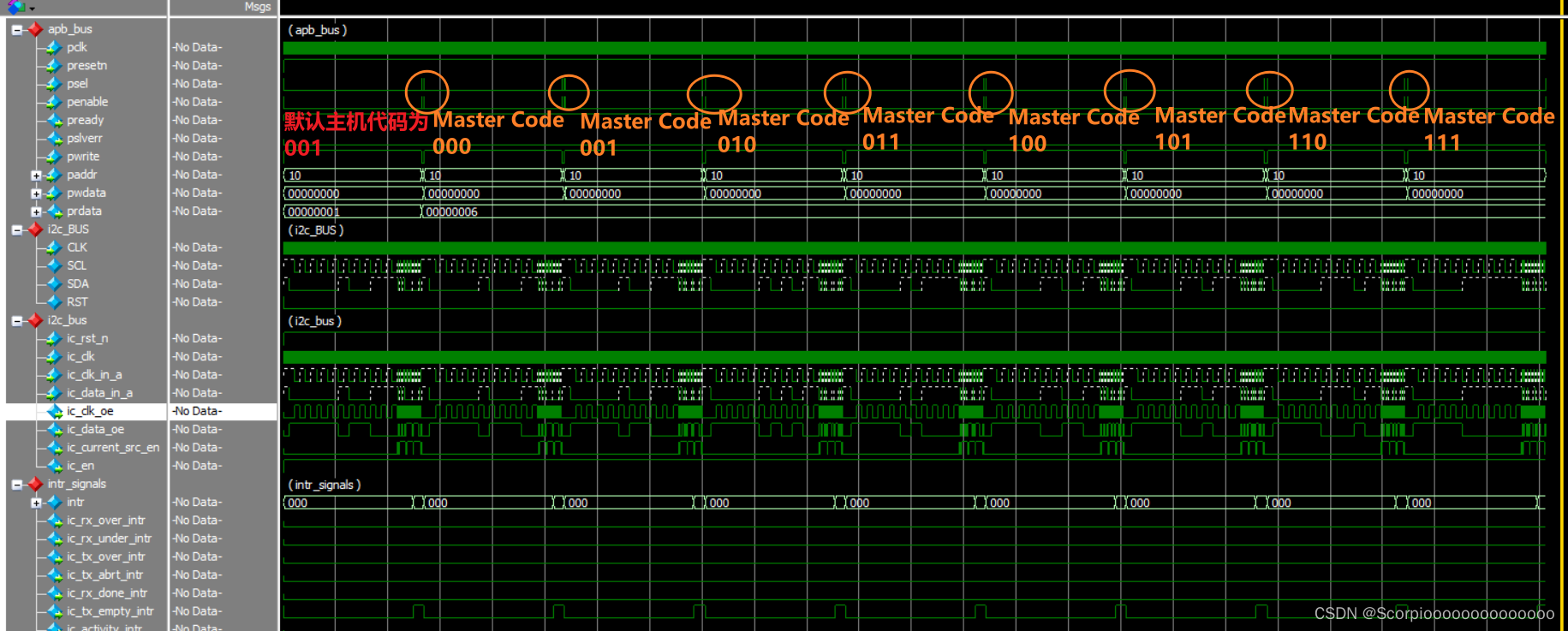

rkv_i2c_master_hs_master_code_virt_seq

测试目的:测试高速模式下主机代码传输

寄存器描述:IC_HS_MAR域用来保存HS模式下的主机代码从000到111共8种,标准或快速模式下变为只读域且读取值为0

代码

建议可使用foreach循环设置主机代码。

波形

3.其他测试序列

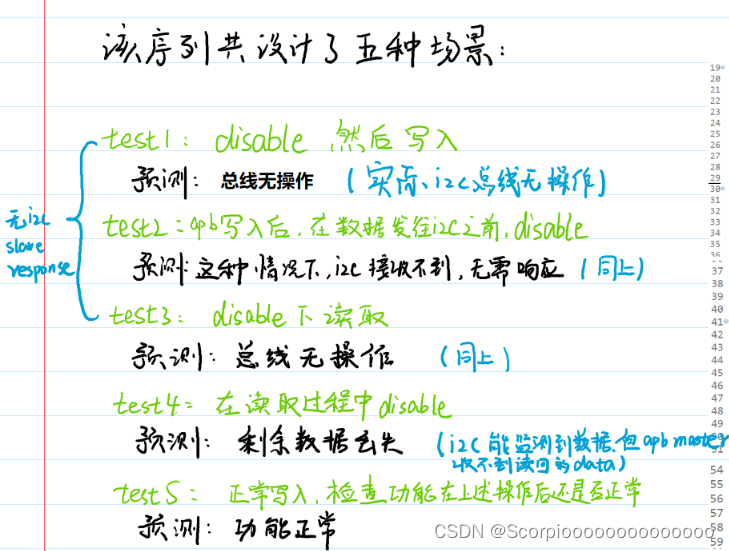

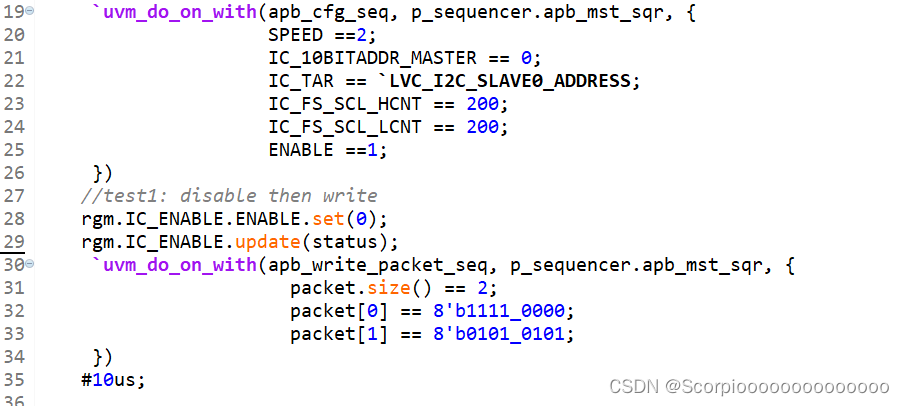

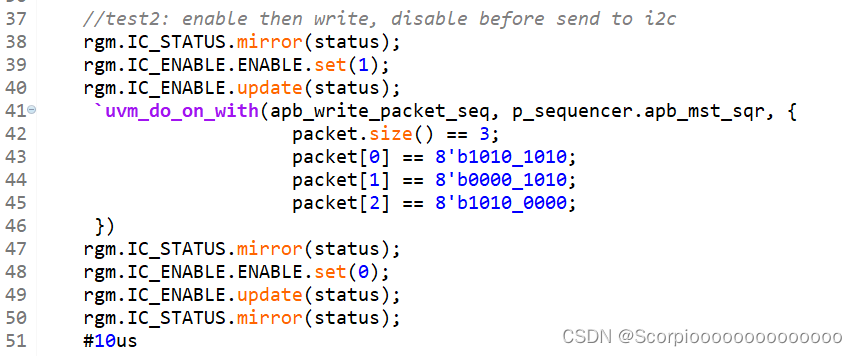

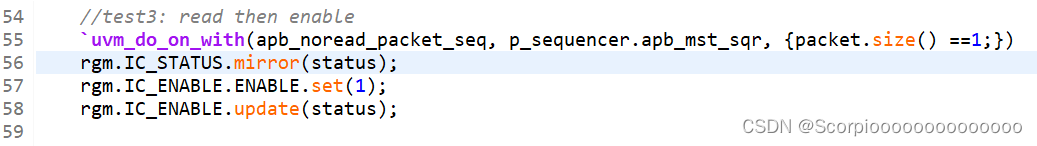

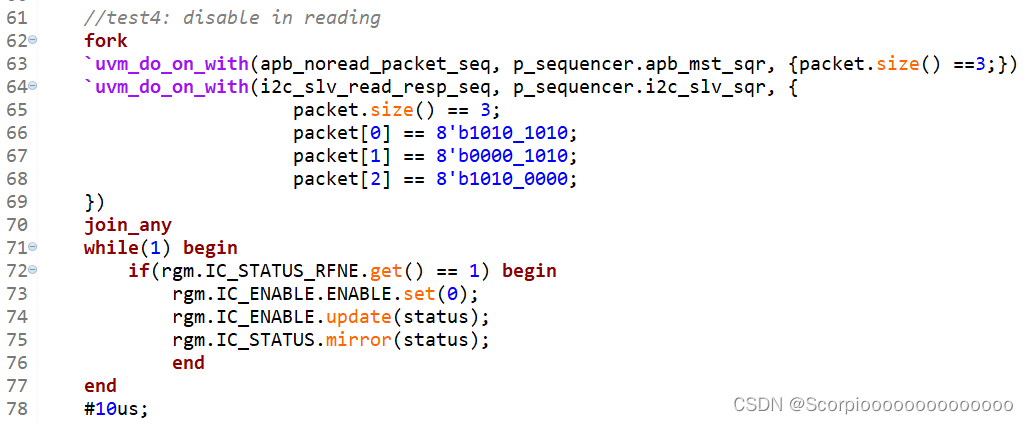

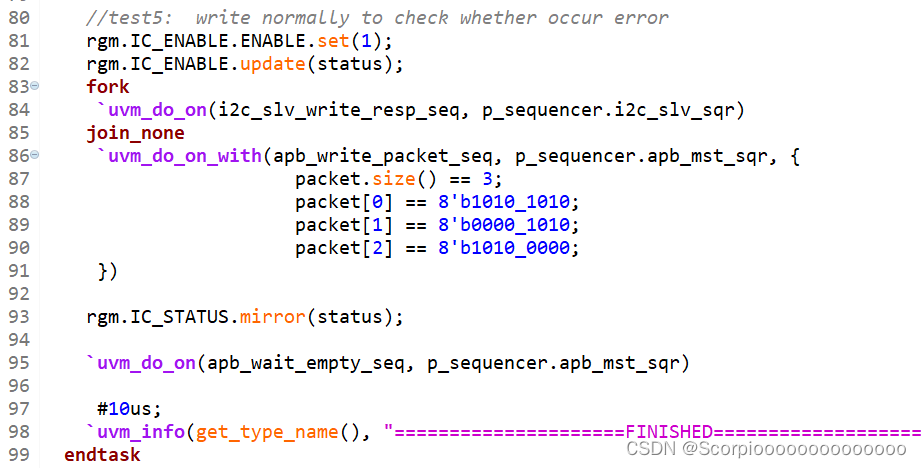

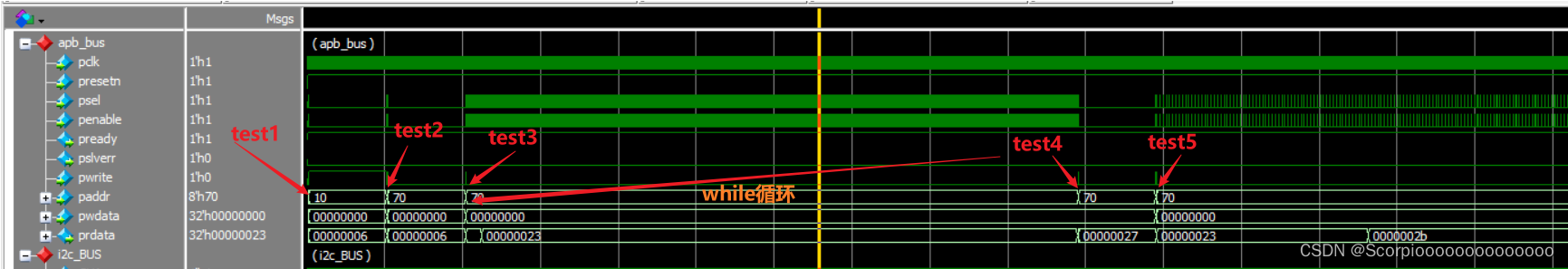

rkv_i2c_master_enabled_cg_virt_seq

测试目的:测试不同使能状态下的读写操作

序列行为描述

代码

波形

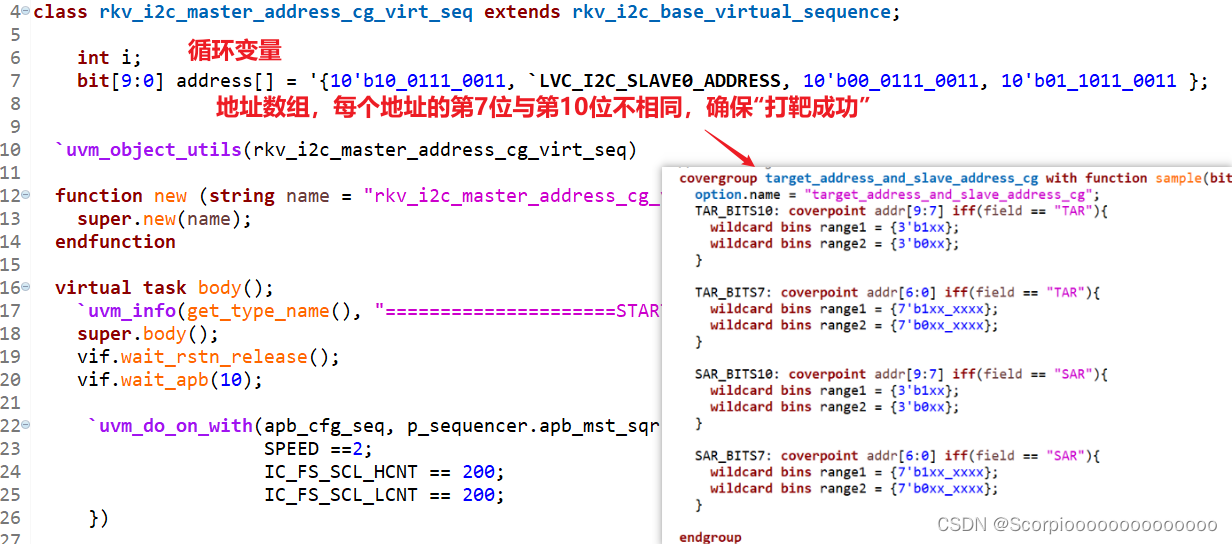

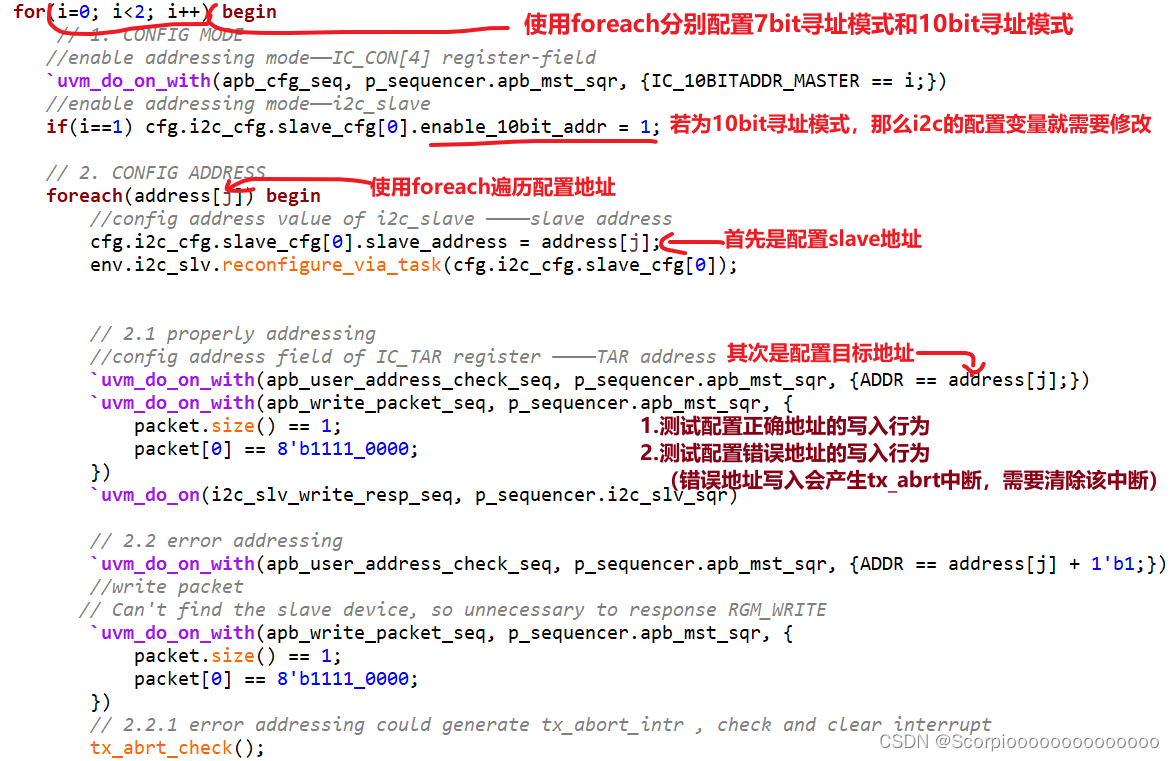

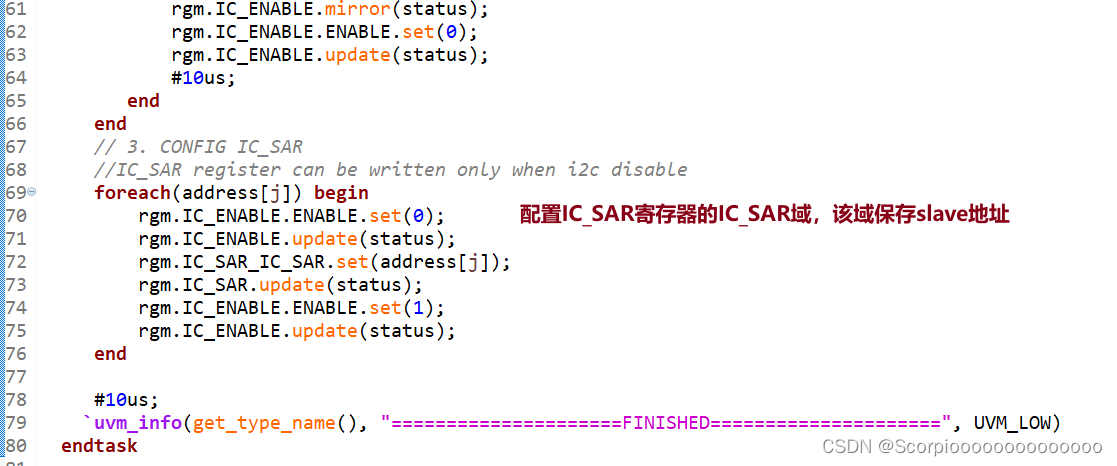

rkv_i2c_master_address_cg_virt_seq

测试目的:测试7bit地址访问和10bit地址访问

代码

❓不太明白为什么在最后设置IC_SAR,是不是可以把它放入apb_user_address_check_seq中?

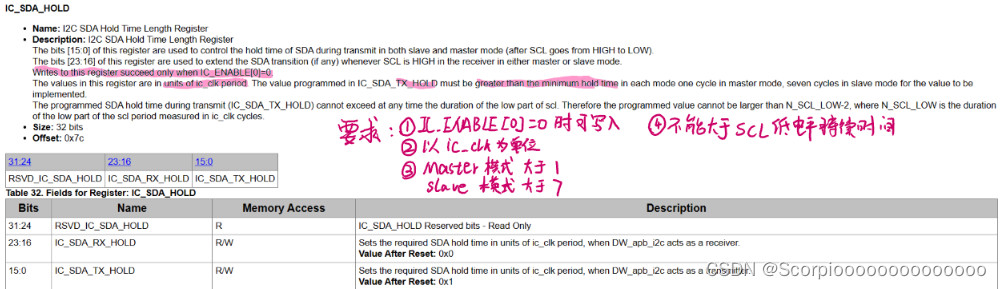

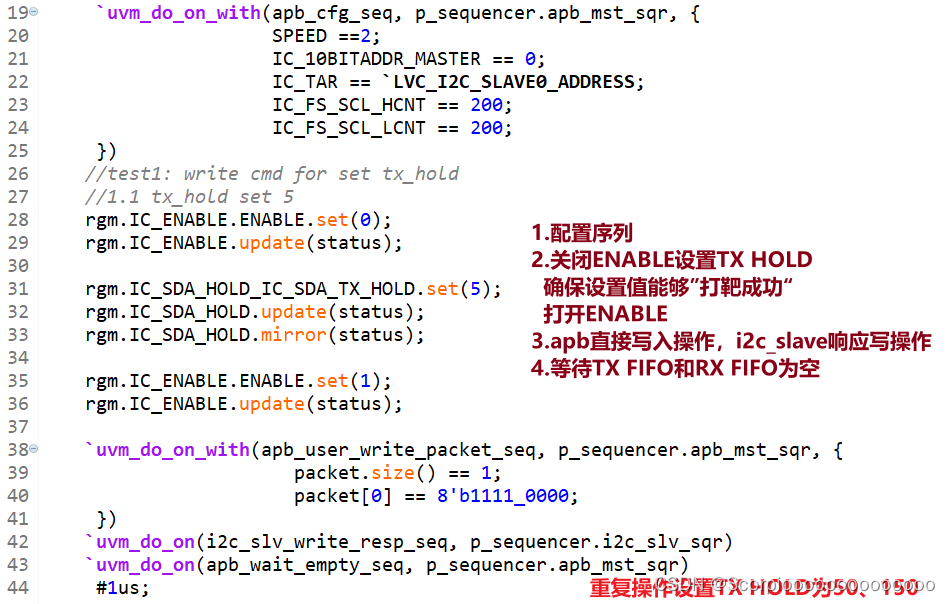

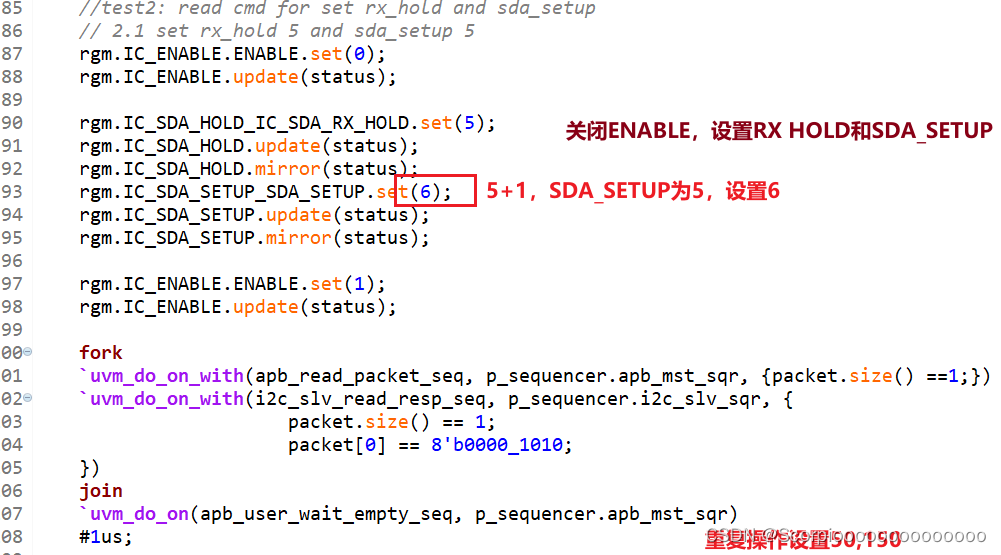

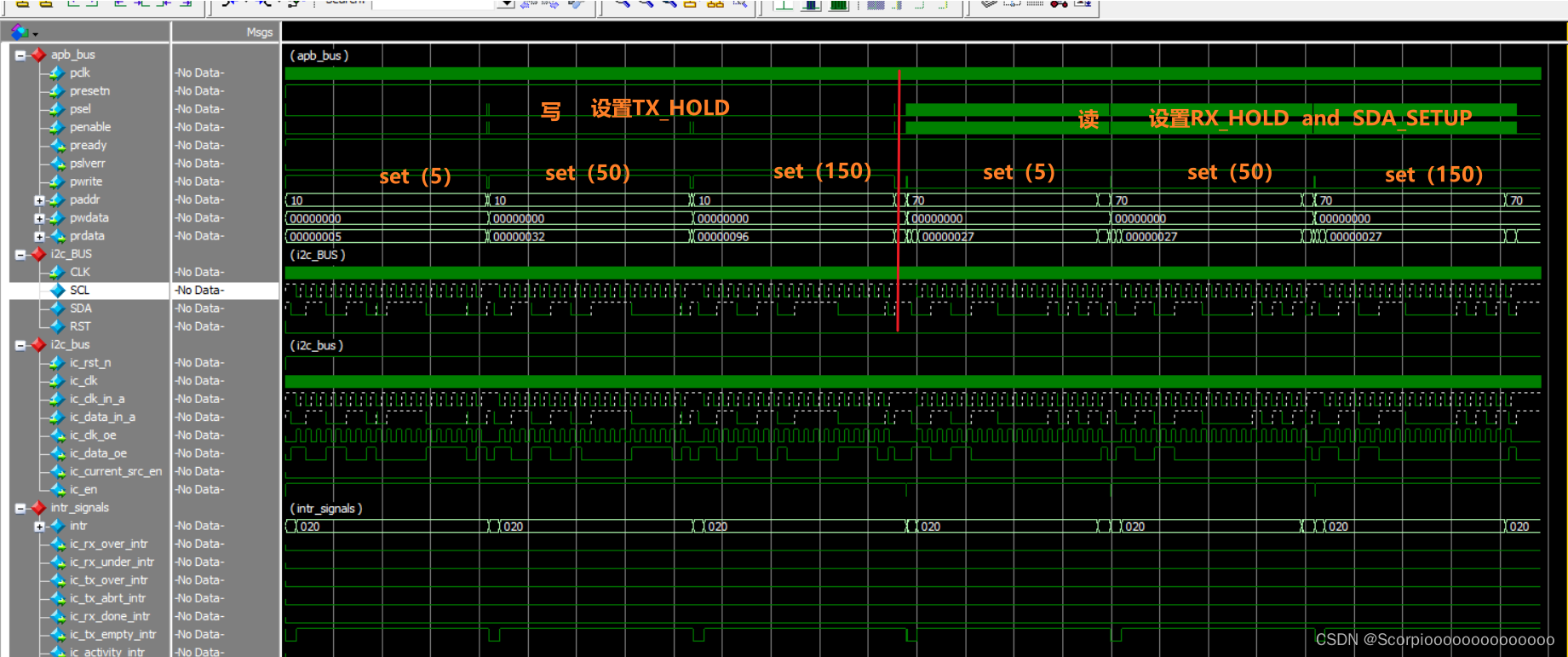

rkv_i2c_master_sda_control_cg_virt_seq

测试目的:测试SDA建立保持时间能否正常设置

寄存器描述

代码

建议使用foreach循环设置域值。

波形

rkv_i2c_master_sda_control_cg_virt_seq

测试目的:测试SDA建立保持时间能否正常设置

寄存器描述

REG_TIMEOUT_RST寄存器的REG_TIMEOUT_RST_rw域表示倒计时计数值,决定倒计时从何时开始,若计数器数到0会将pslverr信号拉高,等待事务中断。

//定义数组存放计数值,对应REG_TIMEOUT_RST_rw域所以是4bit位

bit[3:0] timeout[] = '{'b10, 'b1000, 'b1100};

********************************************

//使用foreach循环设置不同的计数值

foreach(timeout[i]) begin

rgm.IC_ENABLE_ENABLE.set(0);

rgm.IC_ENABLE.update(status);

rgm.REG_TIMEOUT_RST_REG_TIMEOUT_RST_rw.set(timeout[i]);

rgm.REG_TIMEOUT_RST.update(status);

rgm.IC_ENABLE_ENABLE.set(1);

rgm.IC_ENABLE.update(status);

`uvm_do_on_with(apb_user_write_packet_seq, p_sequencer.apb_mst_sqr, {

packet.size() == 8;

foreach (packet[j]) packet[j] == 8'b1111_0000 + j;

})

`uvm_do_on(i2c_slv_write_resp_seq, p_sequencer.i2c_slv_sqr)

`uvm_do_on(apb_wait_empty_seq, p_sequencer.apb_mst_sqr)

#1us;

end

波形

因图片上传过于频繁,无法再贴图了。

930

930

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?