提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

学习内容:

- 对uvm_reg的定义,以及uvm_reg_block的组织

- 对uvm_reg_adapter的定义,以及它与uvm_reg_block之间的关系

- 对uvm_reg_predictor的使用,以及它与uvm_reg_adapter和uvm_reg_block之间的关系

- 改造之前的寄存器发送序列,并以uvm_reg的操作方式去取代

- 应用内建的寄存器序列,做全面的寄存器测试

提示:以下是本篇文章正文内容,下面案例可供参考

一、寄存器模型的完善和嵌入

uvm_reg和uvm_reg_block的定义已经完成,按照要求完成以下步骤:

1.1 Adapter中数据映射的方法实现

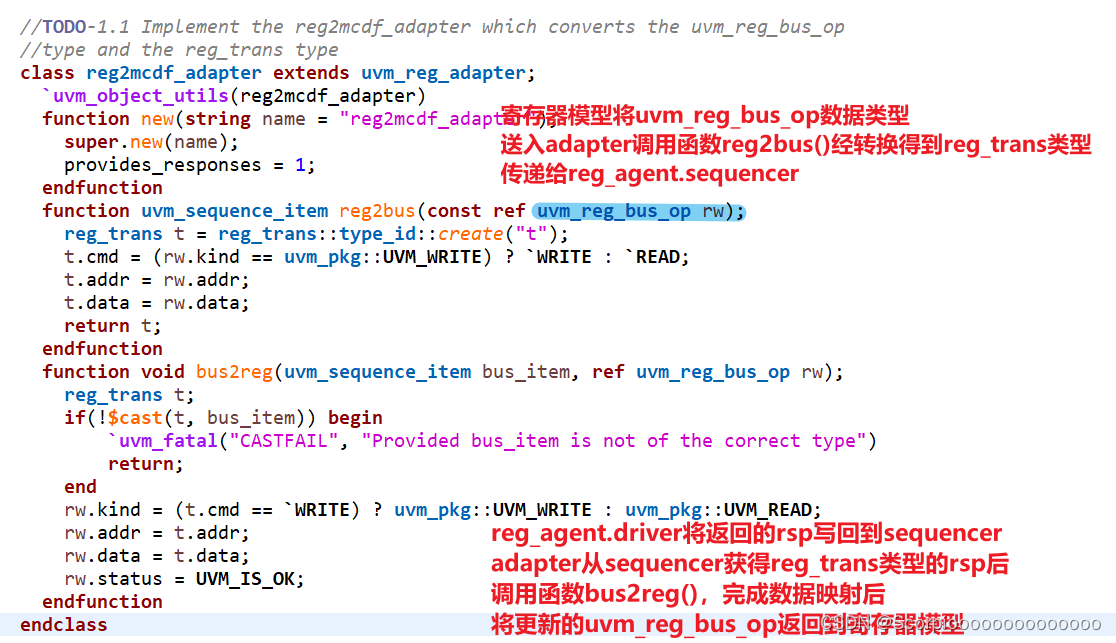

【参考红宝书p416】实现reg2mcdf_adapter类的方法reg2bus以及bus2reg

uvm_reg_adapter的出现是为了解决寄存器模型一侧和总线一侧数据类型不同,需要进行数据类型的转化。前门读写时寄存器模型通过sequence都会产生一个名为uvm_reg_bus_op结构体变量,该变量成员见【红宝书p415,表14.2】,需要通过adapter函数reg2bus以及bus2reg桥接reg_agent.sequencer和rgm一侧,对变量进行类型转化。即adapter的转换功能实际上是将uvm_reg_bus_op事务与成reg_trans事务之间的转换。

函数reg2bus()中的return t 是隐性的类型转换,该函数规定了返回类型是父类item,由于t是子类trans,因此必定会存在类型转换。

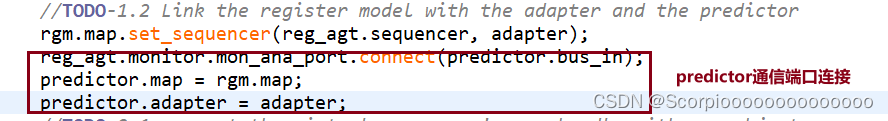

1.2 在env中声明、例化和连接寄存器模型的相关组件

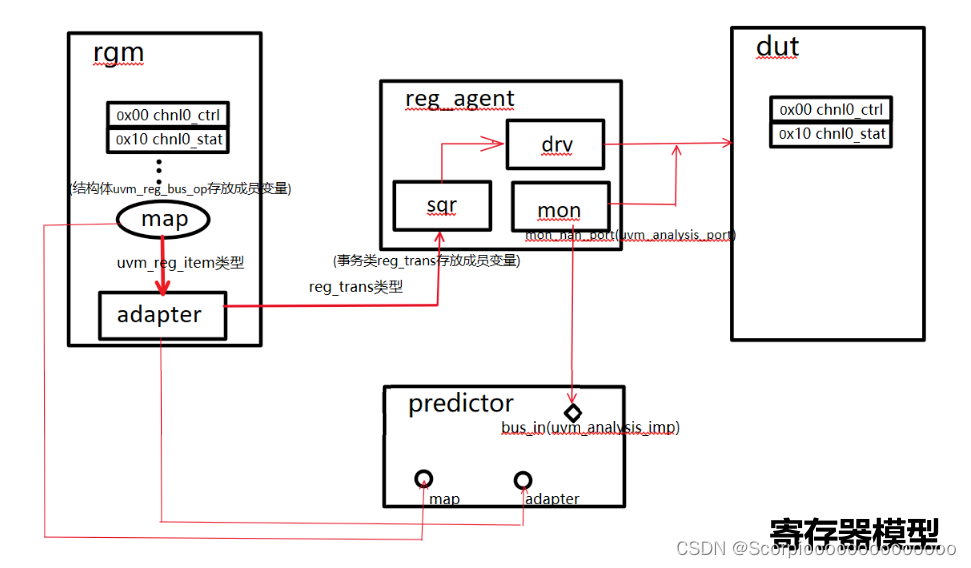

寄存器模型相关组件有rgm、adapter和predictor,需要理清它们之间的关系。

二、寄存器模型的使用

按照以下要求,改造之前的激励序列:

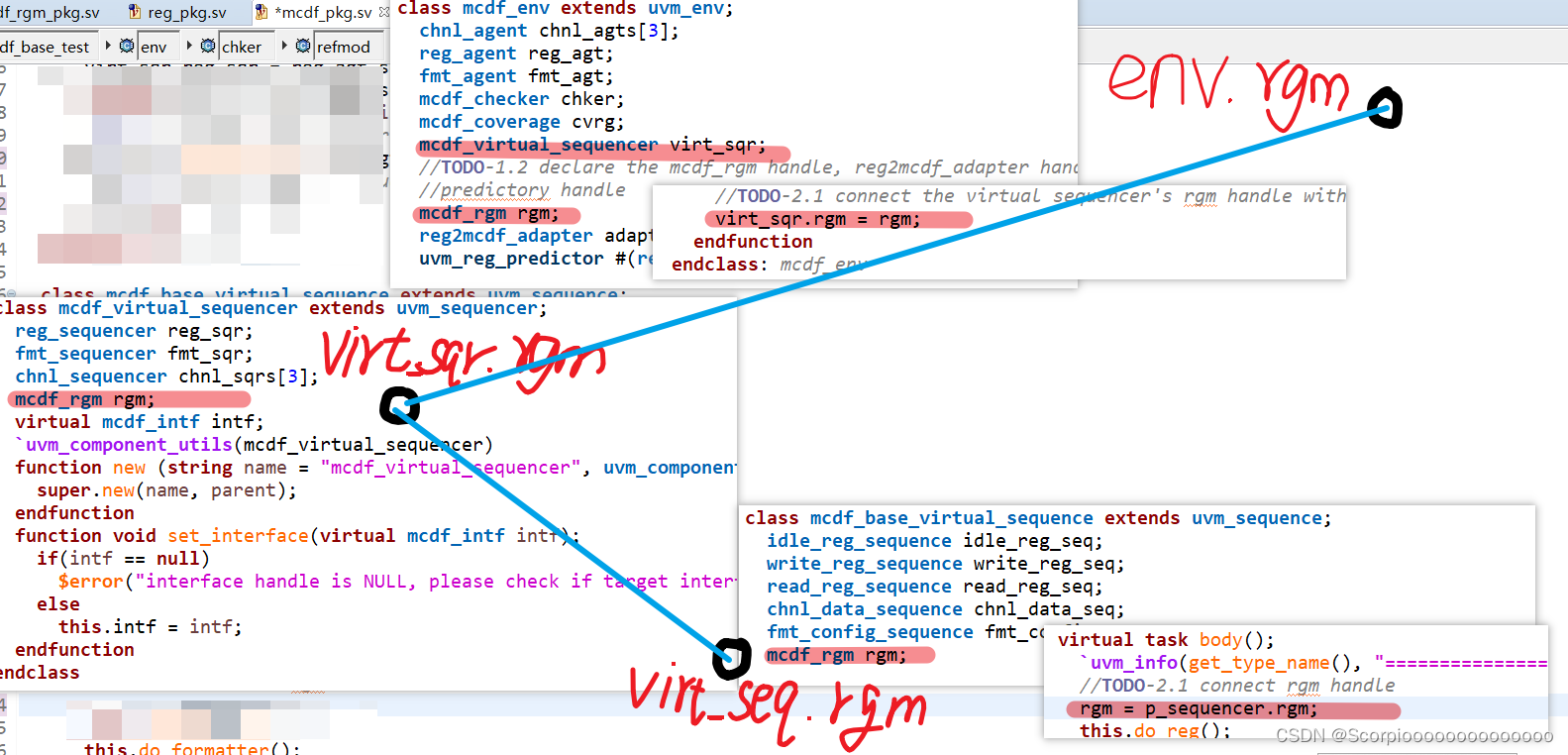

2.1 将环境例化的reg_block与顶层virtual sqr、virtual seq连接

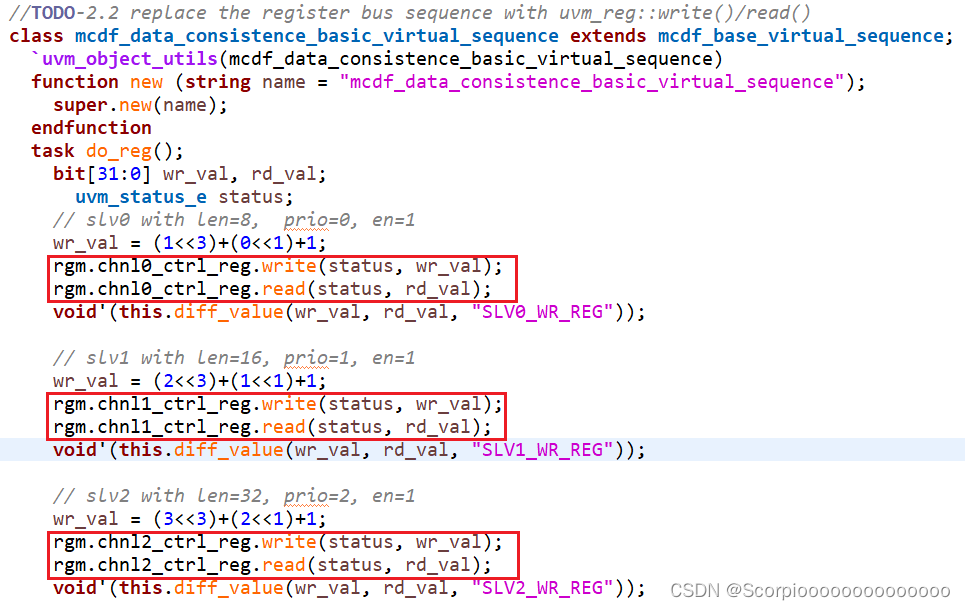

2.2 改写寄存器读写方式1

将mcdf_data_consistence_basic_virtual_sequence原有的由总线sequence实现的寄存器读写,改为由寄存器模型操作的寄存器读写方式。

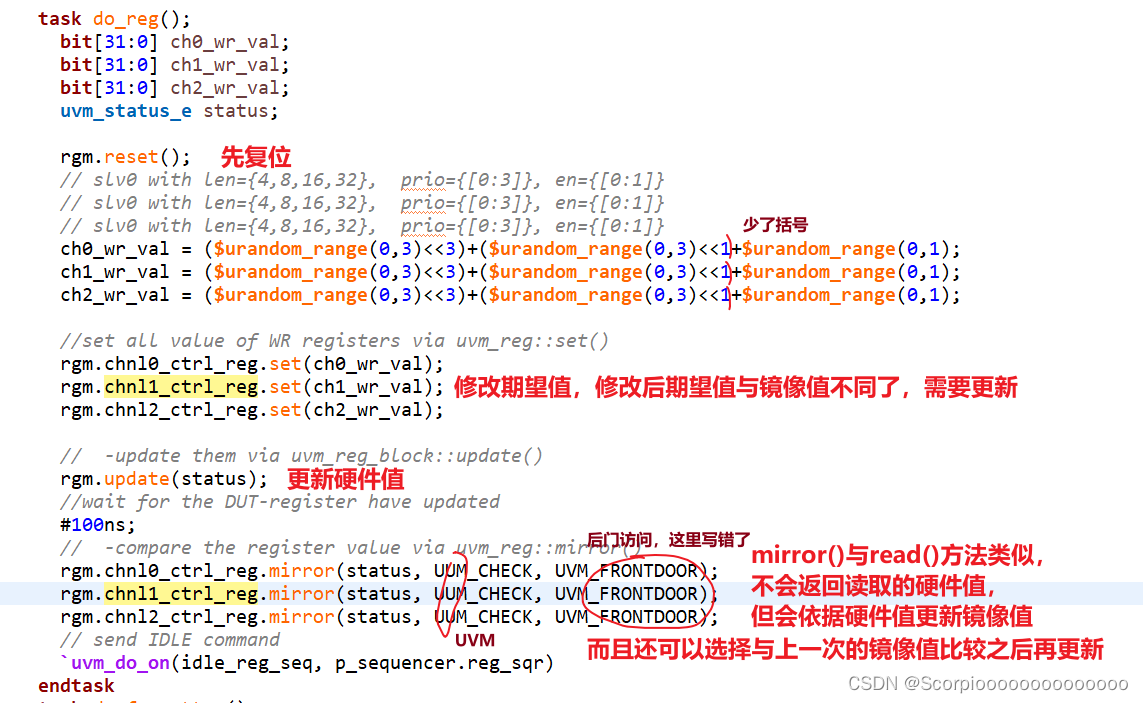

2.3 改写寄存器读写方式2

将mcdf_full_random_virtual_sequence原有的总线sequence实现的寄存器读写,改为由寄存器模型预先设置寄存器值再统一做总线寄存器更新的方式,并且稍后由后门读取的方式取得寄存器值,加以比较。

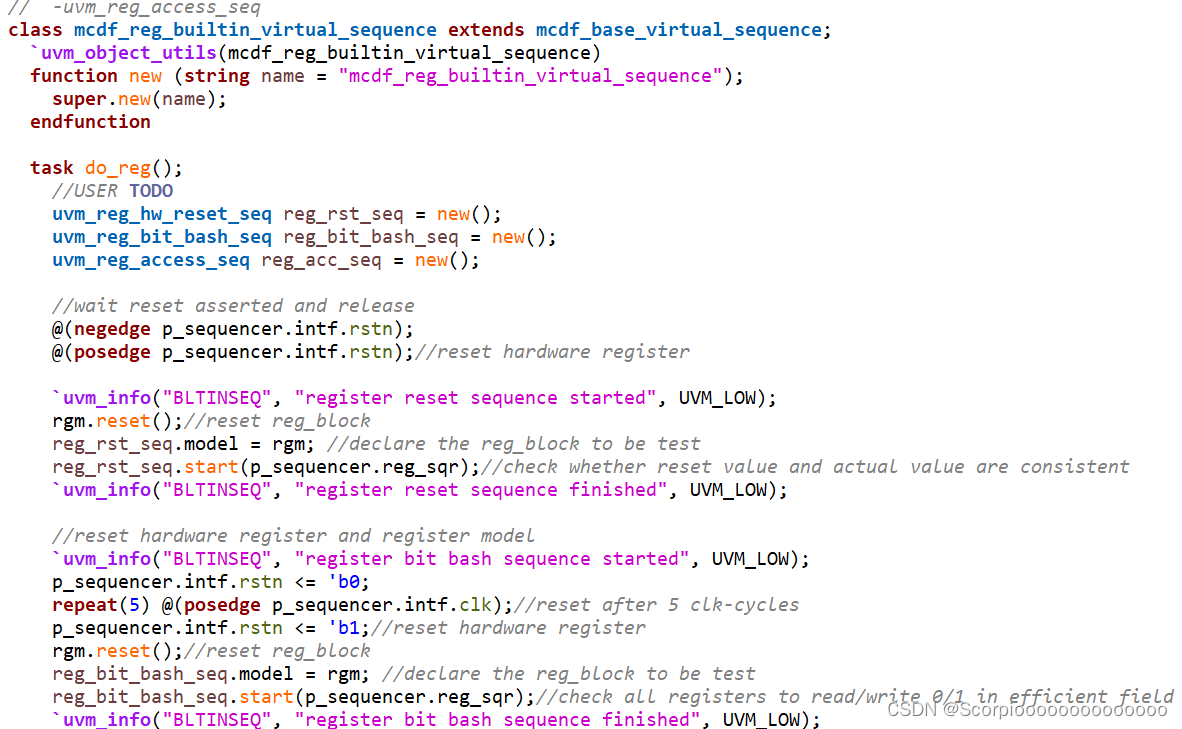

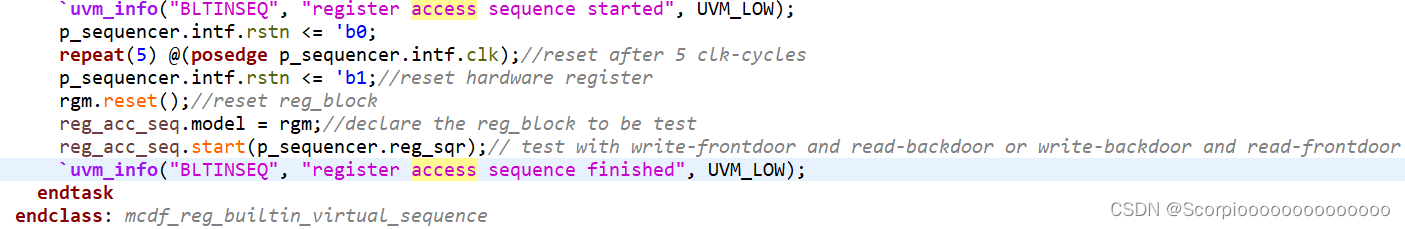

三、寄存器内建序列的应用

UVM已经内建了一些寄存器序列,接下来选择一些序列对寄存器展开测试

在新建的mcdf_reg_builtin_virtual_sequence类中,请使用uvm_reg_hw_reset_seq、uvm_reg_bit_bash_seq和uvm_reg_acess_seq对MCDF寄存器模块展开全面测试。

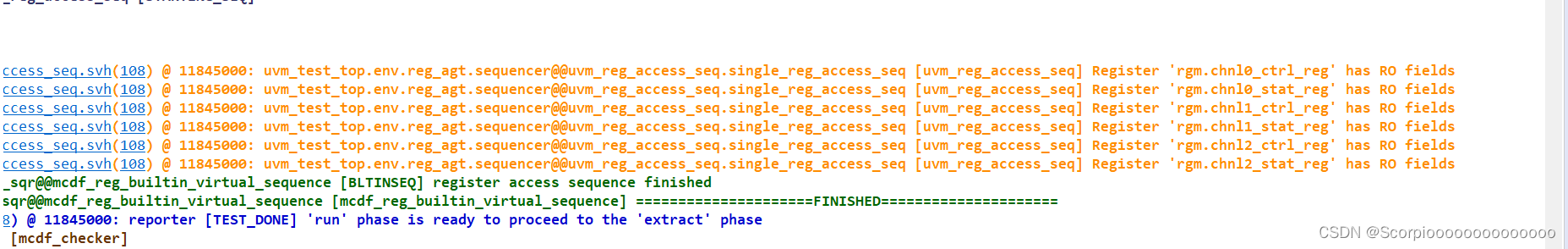

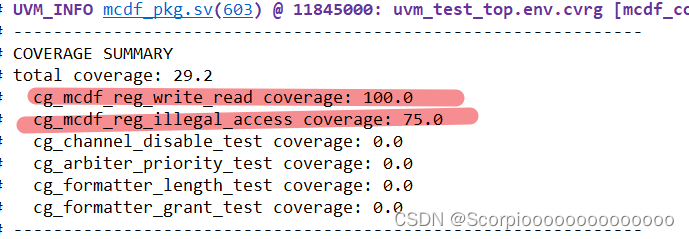

仿真结果:

对于检查寄存器映射的有效性测试,出现wainning信息

MCDF寄存器模型如下图:

361

361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?