ADC 简介

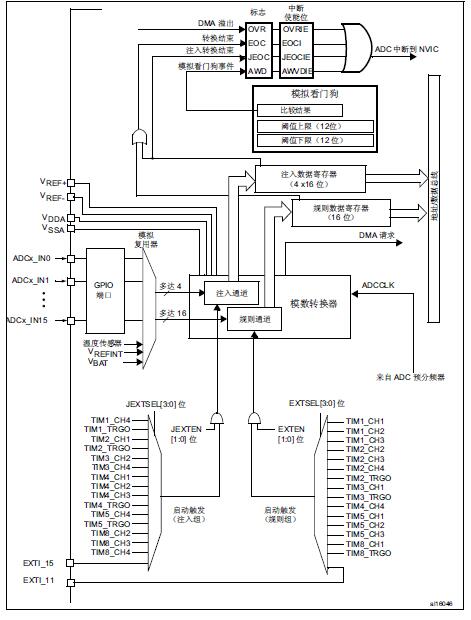

12 位 ADC 是逐次趋近型模数转换器。它具有多达 19 个复用通道,可测量来自 16 个外部 源、两个内部源和 VBAT 通道的信号。这些通道的 A/D 转换可在单次、连续、扫描或不连续 采样模式下进行。ADC 的结果存储在一个左对齐或右对齐的 16 位数据寄存器中。

ADC 具有模拟看门狗特性,允许应用检测输入电压是否超过了用户自定义的阈值上限或下限。

ADC 主要特性

● 可配置 12 位、10 位、8 位或 6 位分辨率

● 在转换结束、注入转换结束以及发生模拟看门狗或溢出事件时产生中断

● 单次和连续转换模式

● 用于自动将通道 0 转换为通道“n”的扫描模式

● 数据对齐以保持内置数据一致性

● 可独立设置各通道采样时间

● 外部触发器选项,可为规则转换和注入转换配置极性

● 不连续采样模式

● 双重/三重模式(具有 2 个或更多 ADC 的器件提供)

● 双重/三重 ADC 模式下可配置的 DMA 数据存储

● 双重/三重交替模式下可配置的转换间延迟

● ADC 转换类型(参见数据手册)

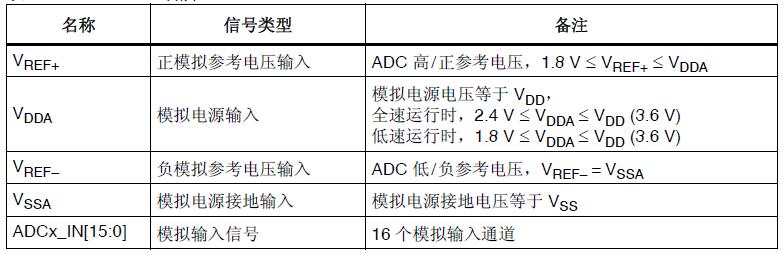

● ADC 电源要求:全速运行时为 2.4 V 到 3.6 V,慢速运行时为 1.8 V

● ADC 输入范围:VREF— VIN VREF+

● 规则通道转换期间可产生 DMA 请求

图 34 显示了 ADC 的框图。

注意:VREF— 如果可用(取决于封装),则必须将其连接到 VSSA

ADC 功能说明

ADC 开关控制

可通过将 ADC_CR2 寄存器中的 ADON 位置 1 来为 ADC 供电。首次将 ADON 位置 1 时, 会将 ADC 从掉电模式中唤醒。

SWSTART 或 JSWSTART 位置 1 时,启动 AD 转换。

可通过将 ADON 位清零来停止转换并使 ADC 进入掉电模式。在此模式下,ADC 几乎不耗电 (只有几 μA)。

ADC 时钟

ADC 具有两个时钟方案:

● 用于模拟电路的时钟:ADCCLK,所有 ADC 共用

此时钟来自于经可编程预分频器分频的 APB2 时钟,该预分频器允许 ADC 在 fPCLK2/2、/4、/6 或 /8 下工作。有关 ADCCLK 的最大值,请参见数据手册。

● 用于数字接口的时钟(用于寄存器读/写访问)

此时钟等效于 APB2 时钟。可以通过 RCC APB2 外设时钟使能寄存器 (RCC_APB2ENR)分别为每个 ADC 使能/禁止数字接口时钟。

通道选择

有 16 条复用通道。可以将转换分为两组:规则转换和注入转换。每个组包含一个转换序列, 该序列可按任意顺序在任意通道上完成。例如,可按以下顺序对序列进行转换:ADC_IN3、ADC_IN8、ADC_IN2、ADC_IN2、ADC_IN0、ADC_IN2、ADC_IN2、ADC_IN15。

● 一个规则转换组最多由 16 个转换构成。必须在 ADC_SQRx 寄存器中选择转换序列的规

则通道及其顺序。规则转换组中的转换总数必须写入 ADC_SQR1 寄存器中的 L[3:0] 位。

● 一个注入转换组最多由 4 个转换构成。必须在 ADC_JSQR 寄存器中选择转换序列的注入

通道及其顺序。注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位。

如果在转换期间修改 ADC_SQRx 或 ADC_JJSQR 寄存器,将复位当前转换并向 ADC 发送一个新的启动脉冲,以转换新选择的组。

本文详细介绍了STM32F4的ADC特性,包括12位分辨率、多种转换模式(单次、连续、扫描、不连续)、模拟看门狗功能、通道选择、采样时间配置、数据对齐方式以及外部触发和DMA使用。内容涵盖了ADC的启动、转换结束标志、中断以及转换序列的管理,是STM32F4 ADC应用的重要参考资料。

本文详细介绍了STM32F4的ADC特性,包括12位分辨率、多种转换模式(单次、连续、扫描、不连续)、模拟看门狗功能、通道选择、采样时间配置、数据对齐方式以及外部触发和DMA使用。内容涵盖了ADC的启动、转换结束标志、中断以及转换序列的管理,是STM32F4 ADC应用的重要参考资料。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9370

9370

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?