1.用计数器实现任意偶数分频

以6分频举例:

module freq6(

input clk,

input rstn,

output clko

);

reg [2:0]cnt;

parameter N = 6;

always@(posedge clk or negedge rstn)

begin

if(!rstn)

begin

cnt = 0;

clko = 0;

end

else if(cnt<N/2-1)begin

cnt++;

else if(cnt==N/2-1)

begin

cnt = 0;

clko=~clko;

end

endmodule思路简单,根据需要改变N值即可得到占空比为50%的不同偶数分频clk。注意判断条件是N/2 - 1而不是N/2,因为cnt是从0开始计数。

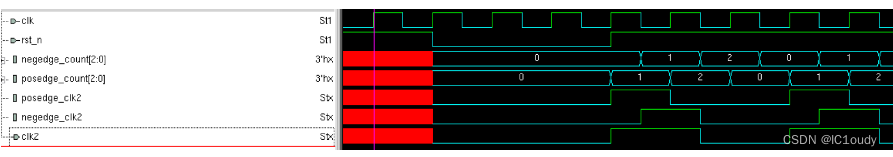

2.实现奇数分频

奇数分频的处理稍微复杂一些,但是观察一下两个clk波形,也很容易找到规律:以3分频为例,慢时钟在上升沿后等两个原时钟下降沿下降;再等两个快时钟沿上升后上升。同理,如果是5分频,则是分别等待3个下降沿和3个上升沿。

具体到3分频,可以采取的方式是将上升沿和下降沿分开来计,形成一个上升沿敏感的2分频和下降沿敏感的2分频时钟,两者相或即可得到3分频时钟。如果是5分频呢?先将其分成两个4分频。

module f3(clk, rst_n,clk2);

input clk;

input rst_n;

output clk2;

reg [2:0] negedge_count;

reg [2:0] posedge_count;

reg posedge_clk2;

reg negedge_clk2;

parameter N = 3;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n || posedge_count == N-1)

posedge_count <= 3'd0;

else

posedge_count <= posedge_count +1'd1;

end

always@(negedge clk or negedge rst_n)

begin

if(!rst_n || negedge_count == N-1)

negedge_count <= 3'd0;

else

negedge_count <= negedge_count +1'd1;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

posedge_clk2 <= 3'd0;

else if (posedge_count == 3'd1 || posedge_count == 3'd0)

posedge_clk2 <= !posedge_clk2;

else

posedge_clk2 <= posedge_clk2;

end

always@(negedge clk or negedge rst_n)

begin

if(!rst_n)

negedge_clk2 <= 3'd0;

else if (negedge_count == 3'd1 || negedge_count == 3'd0)

negedge_clk2 <= !negedge_clk2;

else

negedge_clk2 <= negedge_clk2;

end

assign clk2 = posedge_clk2 || negedge_clk2;

如果不要求占空比,则直接用cnt进行计数,到达5时翻转clk即可。

到这里我们已经可以完成任意整数50%占空比的分频时钟设计,当偶数分频时,采用计数器翻转非常方便;如果是奇数分频,就用双边沿计数器将得到的两个时钟相或。

3.小数分频(分数分频)

在电路设计中比较复杂,因为需要在一段时间内平均达到特定分频比。

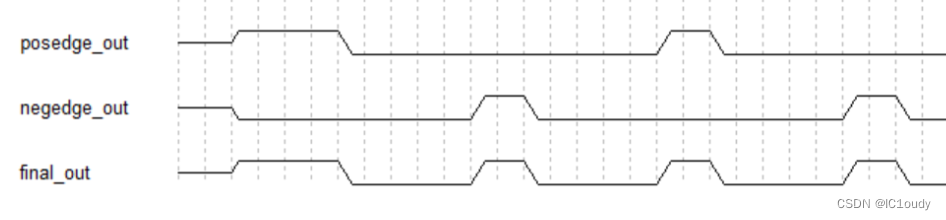

3.1半整数分频

半整数分频电路不再有占空比要求,以3.5分频为例,我们可以参考奇数分频的实现方法,用两个奇数分频的间隔形成半整数分频。用上升沿和下降沿各产生一个7分频的时钟信号,这两个信号的距离是3.5个时钟周期,用逻辑或的形式,产生3.5分频信号。

module half_divide (clk,rst_n,clk_out);

input clk;

input rst_n;

output clk_out;

reg [3:0] p_cnt;

reg [3:0] n_cnt;

wire p_out;

wire n_out;

always@(posedge clk or negedge rst_n)

if(!rst_n)

p_cnt <= 4'd0;

else if(p_cnt < 4'd6)

p_cnt <= p_cnt + 1'b1;

else

p_cnt <= 4'd0;

always@(negedge clk or negedge rst_n)

if(!rst_n)

n_cnt <= 4'd0;

else if(n_cnt < 4'd6)

n_cnt <= n_cnt + 1'b1;

else

n_cnt <= 4'd0;

assign p_out = p_cnt == 4'd0 ? 1 : 0;

assign n_out = n_cnt == 4'd4 ? 1 : 0;

assign clk_out = p_out || n_out;

endmodule

3830

3830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?