除了《FPGA设计实战演练》,还补充了一些小梅哥《FPGA设计与验证》书中的内容

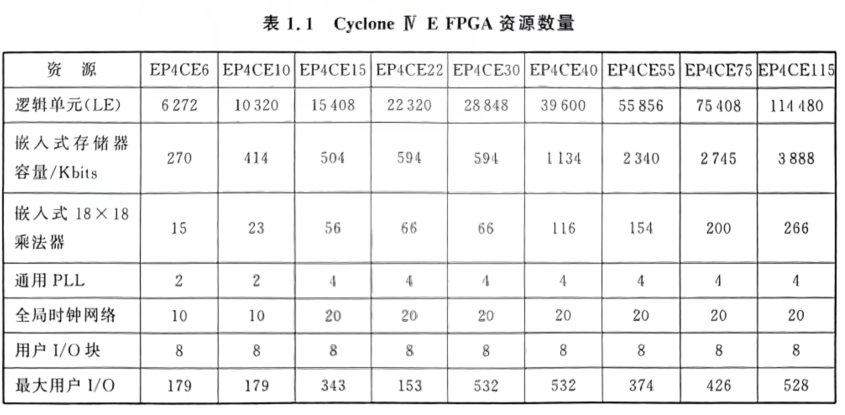

Cyclone IV E资源介绍

每个器件都有多个M9K存储器,每个存储器容量是9Kbit

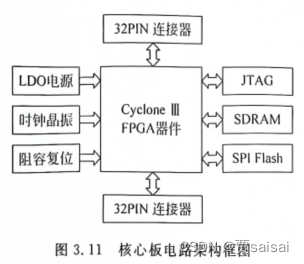

电路设计架构

Cyclone III芯片的电源有三档:3.3v、2.5v、1.2v

3.3V是供给FPGA 的I/O电压,也是系统的其他外设芯片(如SDR SDRAM和SPI Flash)的电源电压;

2.5V是供给JTAG电路和FPGA的PLL电源所需要的;

1.2V则是FPGA 的内核电压(可查看quartus的工具中的PowerPlay Power Analyzer Tool中)。

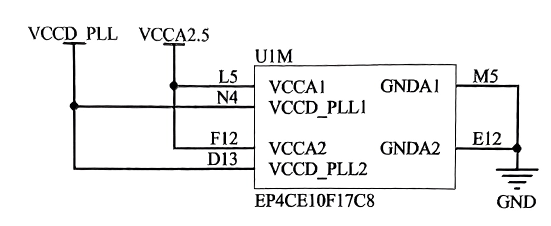

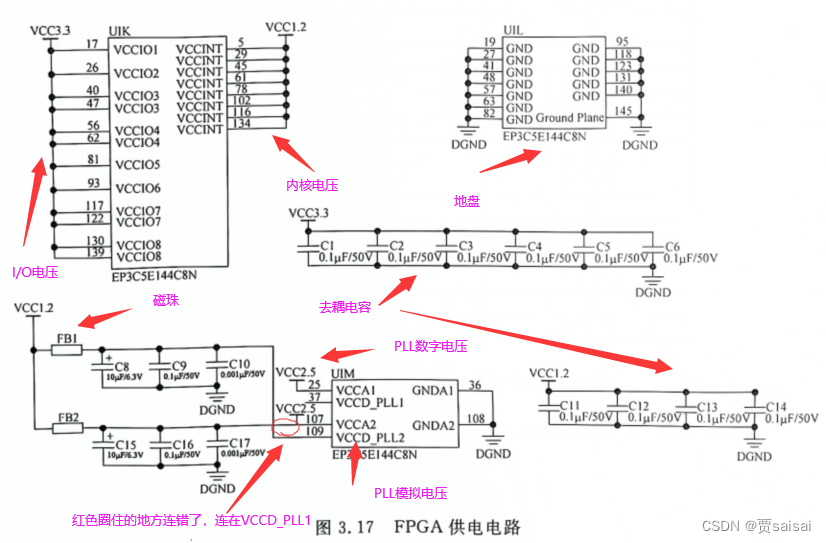

PLL数字部分供电需要1.2v,可以直接由内核电压供电。(VCCD_PLLx)

PLL的模拟部分是2.5v供电,但是模拟电路最好用LDO提供,纹波要小。(VCCAx)

一般在电源输出到接入芯片中间加一个磁珠。电源调试时可以不加磁珠进行测试。

SPI Flash用于FPGA器件的上电配置数据存储,由于FPGA是基于RAM结构的,下电后不能够保存数据,所以需要―颗非易失的Flash,用于存储FPGA 的配置数据。当FPGA上电后,通过专有的SPI接口连接到SPI Flash ,将数据搬运到RAM。

SDR SDRAM是用作扩展的,它既可以作为NIOSⅡ处理器的RAM运行程序﹐也可以作为后续LCD等需要实时大数据量存储的缓存应用。

上下两个32PIN的连接器,分别引出 23个I/О引脚,扩展接口。

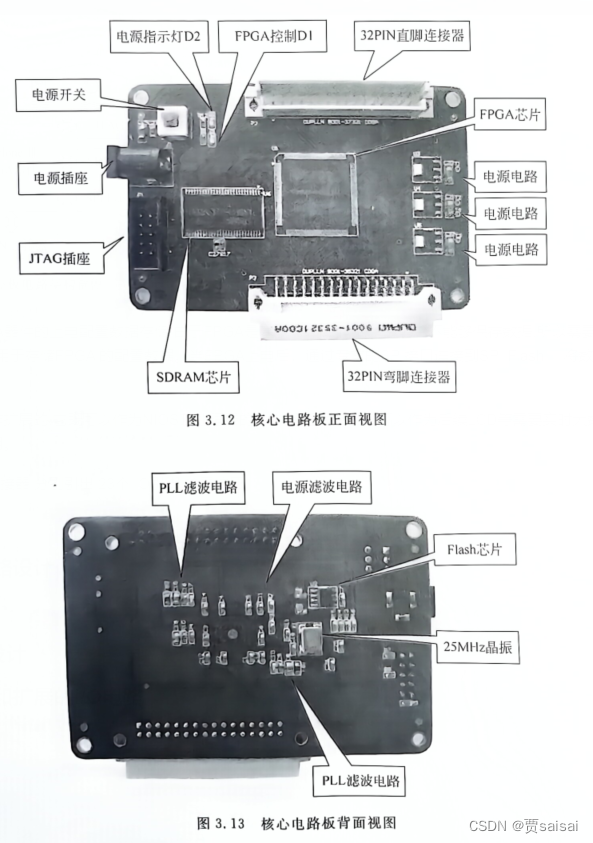

上图是书中作者自己做的板子,下面的关于电路的介绍也是关于这个板子的

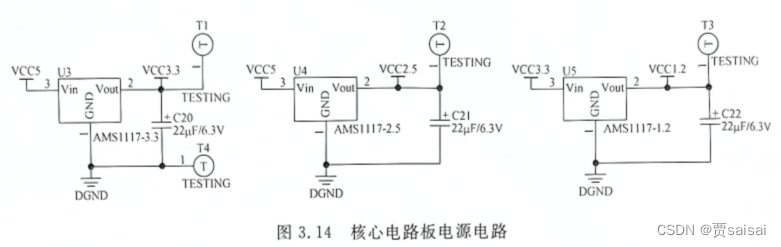

电源电路设计

作者采用的是最便利的LDO芯片设计,其中T1/T2/T3/T4都是测试点,可以学习这种测试点,方便生产和调试以及电路问题的查找,直接万用表戳容易发生短路。

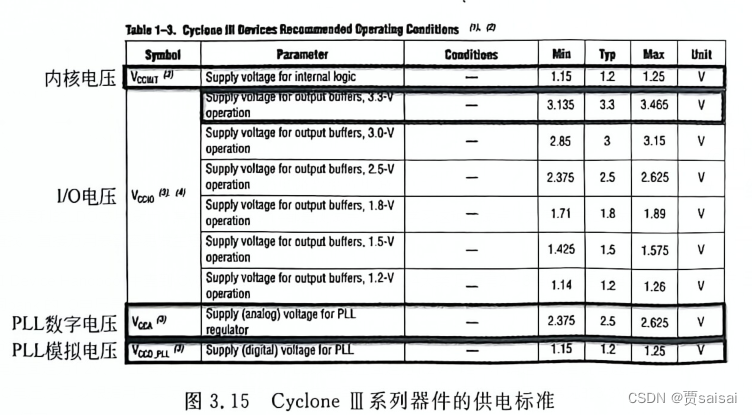

从Cyclone Ⅲ Device Handbook中查到,CycloneⅢ系列器件的供电一般分为4大类,压值有2~3挡(可能更多挡,这主要取决于不同bank 的I/O电压是否有特殊供电需求)。

这四类电源分别是内核电压VCCINT、I/O电压VCCIO、PLL模拟电压VCCA、PLL数字电压VCCD_PLL。

-内核电压固定为1.2V

-PLL模拟电压固定为2.5V,PLL数字电压固定为1.2V

-有选择余地的电源是I/O电压,它可以根据用户实际应用所需要的I/О标准选择不同的电压,此处开发板使用最常见的3.3V,进行所有的I/O bank供电。

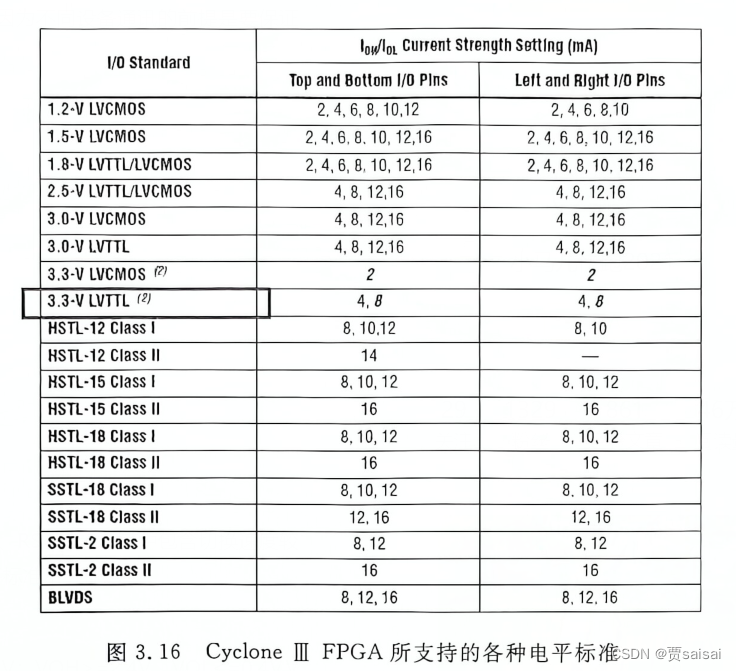

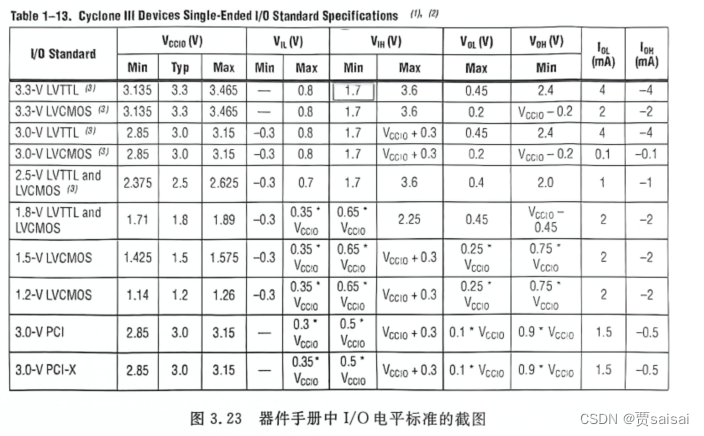

FPGA支持的电平标准也非常多,下图中,左边是电平标准,右边是支持的引脚

在FPGA的供电电路中,每1~2个电源引脚都配有1个去耦电容。在空间允许的情况下,每个电源引脚尽量都就近放置去耦电容(PCB布局的时候)。

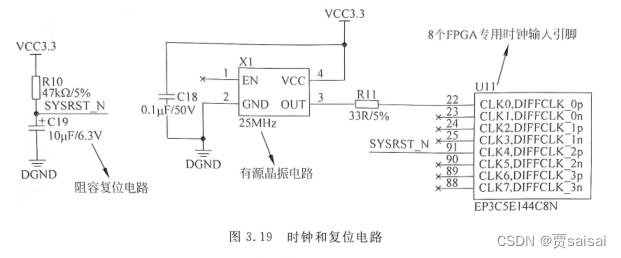

时钟和复位电路设计

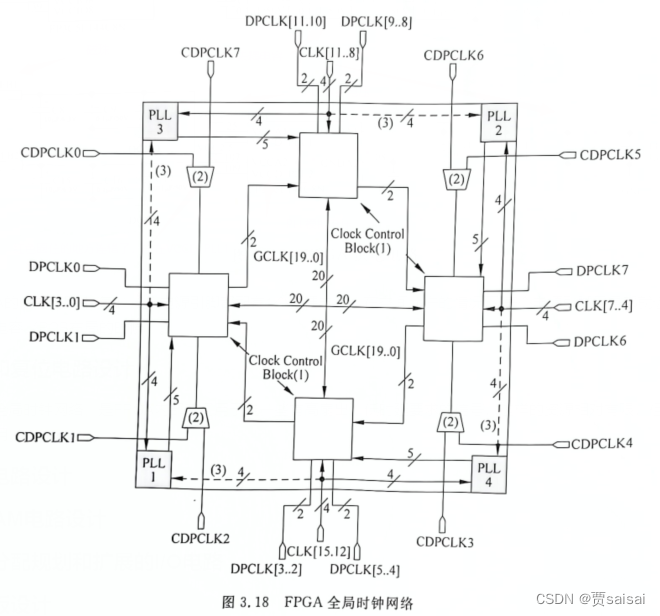

所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。

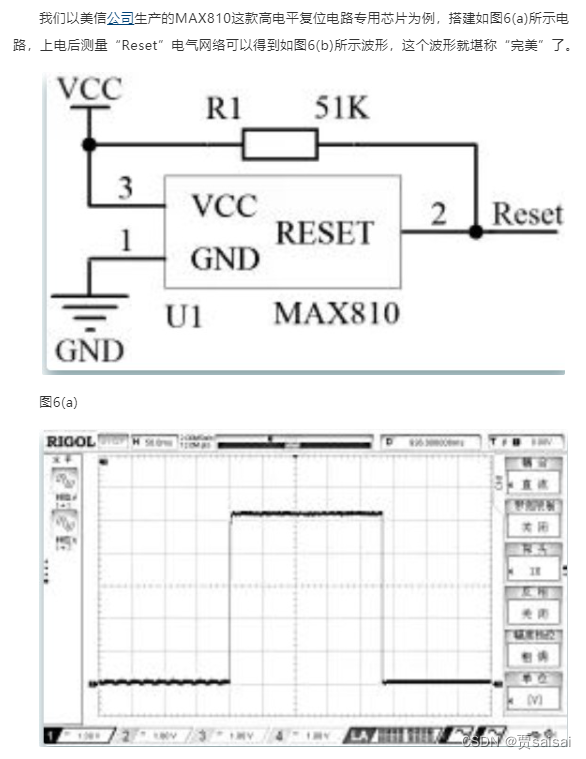

下面先说明复位应该最低多长时间:

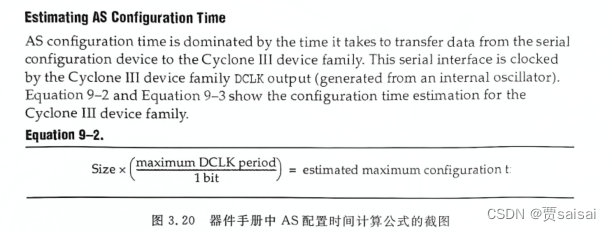

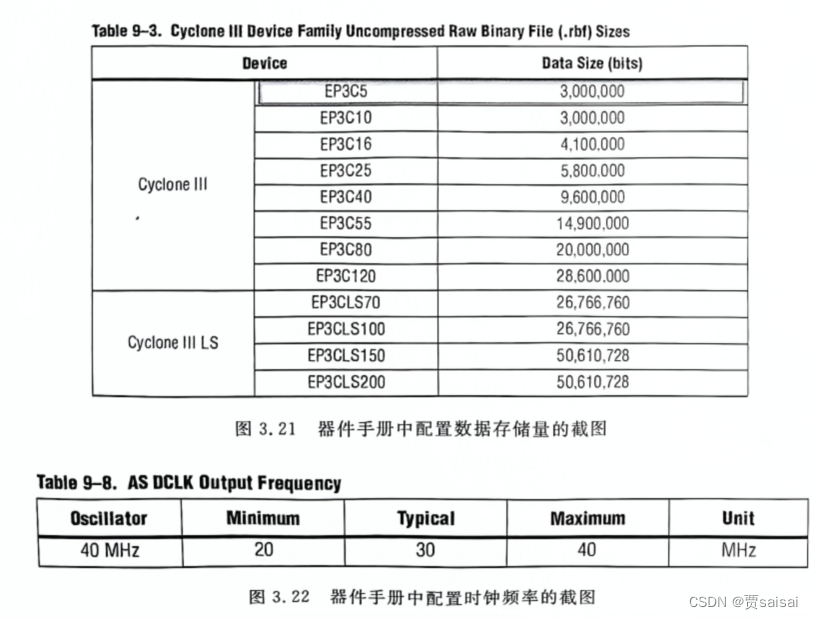

AS配置时间主要是指从串行配置设备向Cyclone III设备系列传输数据所需的时间。该串行接口由Cyclone Ill设备系列的DCLK输出(由内部振荡器产生)提供时钟。下面的那是公式

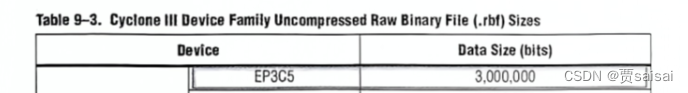

公式中的Size即上图的Data Size,采用的是EP3C5,输出频率是20~40Mhz,对应的DCLK period是50ns ~ 25ns

所以最大的周期是50ns

所以最后的计算周期是:

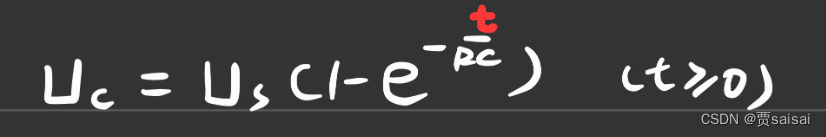

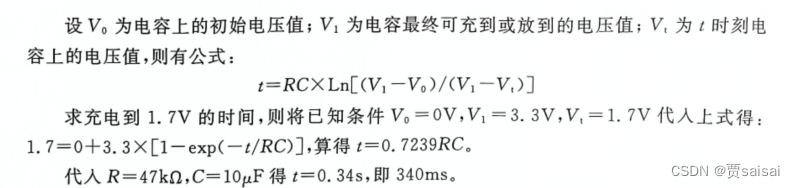

下面开始计算阻容复位电路该如何选择电路的参数:

VIH代表高电平的下限,VIL代表低电平的上限。VOH和VOL应该是输出的

复位输入引脚作为3.3V LVTTL标准电平的时候,最低VOH电压值是1.7V,那么可以由此计算阻容复位电路从0V上升到1.7V所需的时间。(这里我不太明白,我觉得应该是VIH的最大值,即输入电平的最大值0.8,因为我现在还不懂0.8~1.7这一段算什么,也算低电平?)

可以计算

所以和上面的时间相比是比较大的。

常见的复位芯片:

常见的低电平复位电路有MAX705、MAX706、MAX809、MAX811等器件。高电平复位电路有MAX810、MAX812等器件。

而MAX707、MAX708、MAX813L等器件同时有高、低电平复位输出信号和看门狗输出,在实际产品中经常会看到它们,需要注意的是,不同芯片的复位脉冲时间不一样,但是一般都可以达到100至200ms左右,完全满足常见处理器对复位时间的需求。

配置电路设计

这里所说的FPGA配置电路,一方面要完成从PC上把 bit文件下载到FPGA或存储器的任务﹔另一方面则要完成FPGA上电启动时加载配置数据的任务。

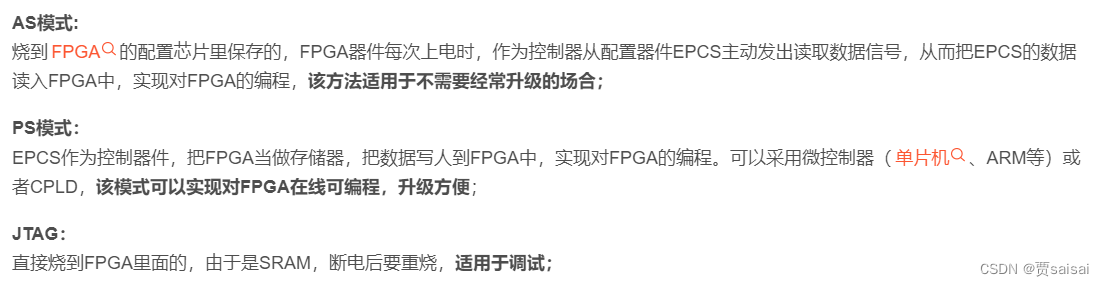

三种启动配置

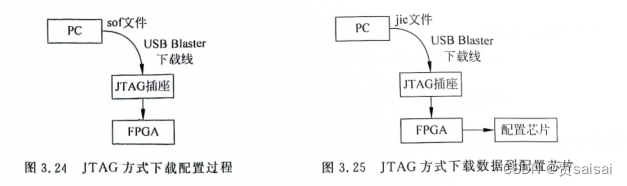

FPGA器件的启动配置主要有JTAG方式,以及AS和PS配置方式。

AS配置方式由FPGA器件引导配置过程,它控制着外部存储器及其初始化过程。EPCS 系列配置芯片,如EPCS1,EPCS4,专供AS模式,目前只支持Cyclone / Cyclone II / CycloncⅢ系列。使用Altera串行配置器件来完成,FPGA器件处于主动地位,配置器件处于从属地位。配置数据通过DATA0引脚送人FPGA。配置数据被同步在 DCLK输人上,1个时钟周期传送1位数据。

PS配置方式则由PC或其他控制器控制配置过程。通过加强型配置器件,如 EPC16,EPC8,EPC4等来完成。在PS配置期间,配置数据从外部储存器件通过DATAO引脚送入FPGA。配置数据在 DCLK上升沿锁存,1个时钟周期传送1位数据。

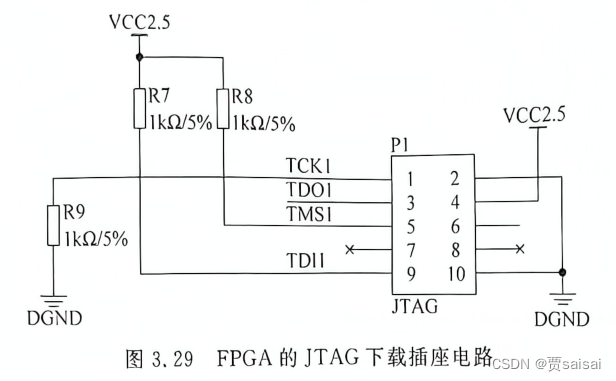

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA是基于RAM模式的,易失存储器书。中作者采用的是JTAG模式:前面那个调试,断电数据丢失。后面PC端的QuartusⅡ软件通过下载线缆将配置数据流(jic文件)下载到配置芯片中。

书中作者的板子采用的是AS(保存程序)+JTAG(下程序、调试)

FPGA加载程序方式

FPGA上电后,内部的控制器首先工作,确认当前的配置模式。如果是外部配置芯片启动,则通过和外部配置芯片的接口(如SPI接口)将配置芯片的数据加载到FPGA 的RAM中,配置完成后开始正式运行。

JTAG在线配置是否和配置芯片加载不冲突,JTAG在线配置的优先级是最高的,无论此时FPGA中在运行什么逻辑,只要JTAG下载启动,FPGA便停下当前的工作,开始运行JTAG下载的新的配置数据。

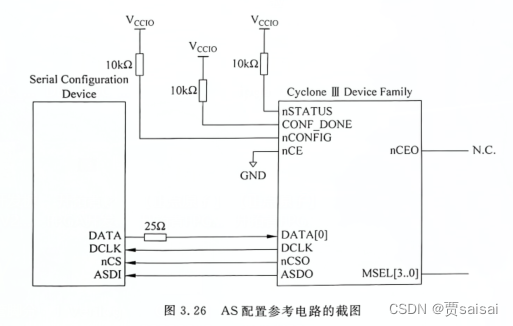

AS启动配置电路

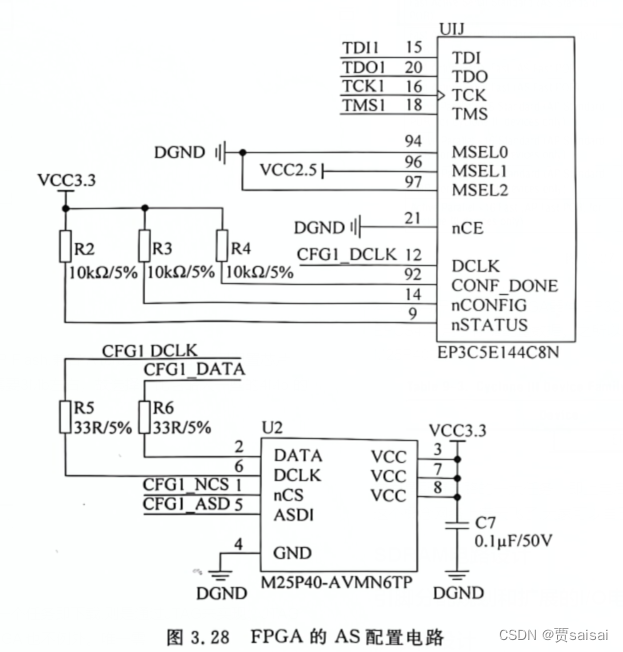

AS配置方式(SPI Flash的接口连接方式),FPGA 的几个主要引脚nSTATUS\CONF_DONE\nCONFIG\nCE的连接,或者上拉,或者接地,主要是为了保证这些信号在上电初始处于一个确定的电平状态,防止错误电平导致误触发。

DATA\DCLK\NCSO\ASDO这四个引脚便是SPI接口,连接到SPI Flash。

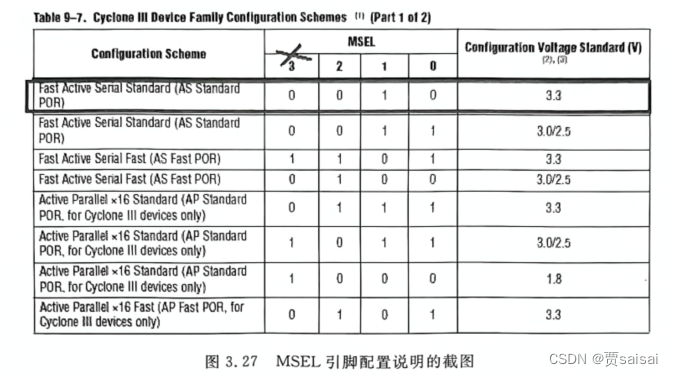

FPGA有一组MSEL引脚用于设置FPGA初上电时的启动模式,本书所用开发板中使用的 EP3C5器件没有bit3,只有 bit2~0,上电使用FastAS模式从SPI Flash加载配置数据。

本书所用开发板中的FPGA器件 EP3C5E144C8N的AS配置电路。M25P40是一颗4Mb 的 SPI Flash,兼容 Altera公司推荐的专用配置芯片EPCS4,可用于存储配置数据。

之所以选择4Mb的SPI Flash,是因为EP3C5器件的配置数据需要3Mb左右,故选择了比它略大一些的4Mb 的M25P40芯片。

前面是配置电路的一大任务,即上电启动配置数据的电路,通过一个SPI Flash来实现。而另一个任务即下载,则是通过JTAG来实现。需要注意的是Cyclone Ⅲ器件的JTAG电压必须是2.5V。另外,即便前面的MSEL设置了FPGA启动模式是FastAS模式,但是JTAG永远是最高优先级的模式,任何时刻,只要JTAG需要进行下载配置,那么配置模式将会转换。

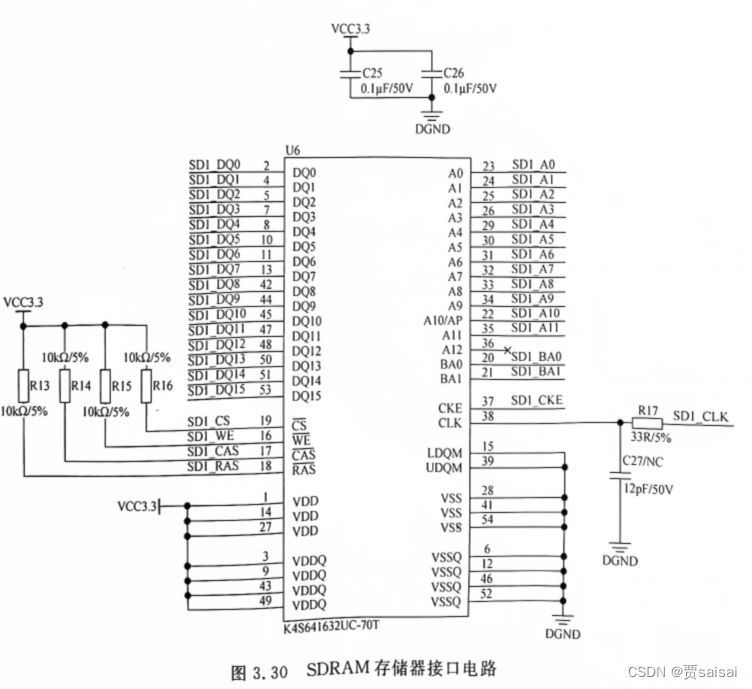

SDRAM电路设计

SDRAM 的电路很简单,只要将地址总线﹑数据总线、控制总线连接到FPGA的I/O口上即可。由于使用的是SDR SDRAM,应用中速率一般在100MHz左右,没有必要做等长处理,只要确保整体的走线长度不要过长,SDRAM的时钟走线干净、可靠即可。

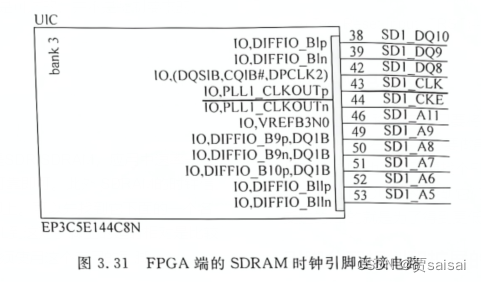

此外,SDRAM的时钟信号SD1_CLK也不能随便找个FPGA引脚就乱接。板子把SD1_CLK专门连接到了PLL1_CLKOUTp这个引脚上。可以先找到它下面的一个名为PLLl_CLKOUTn的引脚,它们是一对,时钟源是来自于FPGA 的 PLL。和前面的全局时钟网络差不多。PLL到这对引脚上的延时相对是比较受控的,目的就是为了得到更低延时,更稳定可靠的时钟信号。SDRAM的时钟高达100MHz以上,所以就必须使用这个专用的引脚。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?