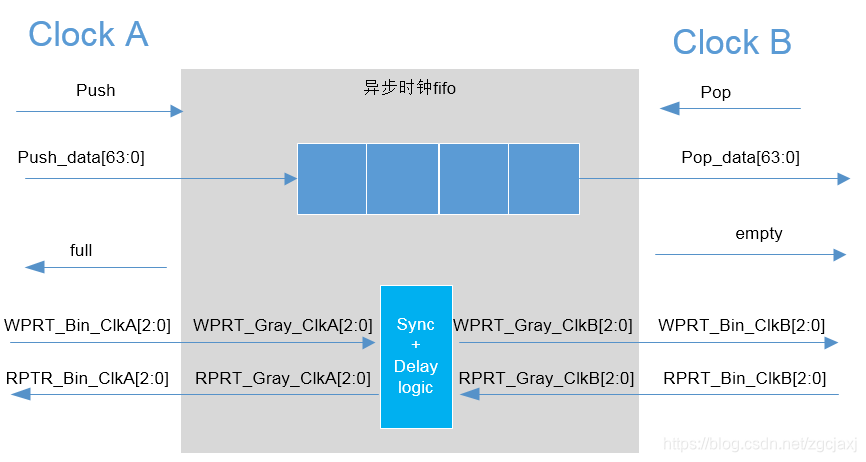

在现代大规模ASIC设计中,经常会遇到跨时钟域的数据传输,此时就需要用到异步时钟FIFO。既然是先进先出的fifo,那就有push端和pop端。假设push端时钟为clcok A,pop端时钟为clock B。clock A和clock B可能前者主频高;也可能后者主频高;还有可能两边主频一样,但存在相位差 (片间互联时用的较多)。

要完成一个异步fifo的功能,至少要有以下信号(假设fifo深度为4,一层可以传输64bit数据)

|

Signal |

功能 |

|

Push |

ClockA,FIFO not full 且前级模块有新data时,push拉高,往某一个entry中push数据 |

|

Push_data[63:0] |

ClockA,新来的data,将要被push到异步fifo中。 |

|

Full |

ClockA,一般根据WPRT_Bin和RPTR_Bin来判断是否为full,当满足(WPRT_Bin[1:0] == RPTR_Bin[1:0]) && (WPRT_Bin[2] != RPTR_Bin[2]) 时,表明full。 |

|

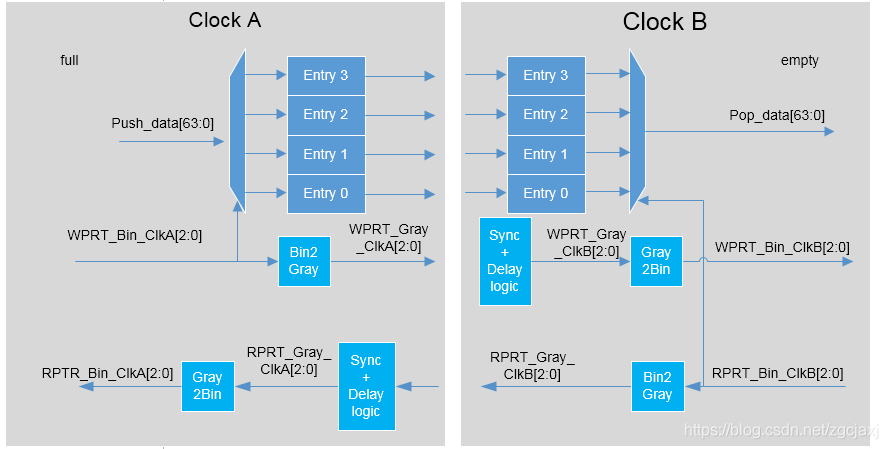

WPRT_Bin_clkA[2:0] |

ClockA,write ptr的二进制表示, 用于指导push 的时候新数据push到哪个entry, 初始为0,成功push到一个entry后,加1。只增不减,循环进行,000 -> 001 -> … -> 111 -> 000 …。 Entry为4层,2bit就可以用来指示4个entry了,但一般为了能方便的得到full和empty信号,会使用多1bit。 |

|

WPRT_Gray_clkA[2:0] |

ClockA,write ptr的格雷码表示,格雷码任意两个相邻的代码只有一位二进制数不同,一般设计异步FIFO时,两个时钟域之间的ptr 都通过格雷码传递。 Write ptr会以格雷码形式送给clockB,最终将用于clockB的empty信号的计算。 在数字系统中,常要求代码按一定顺序变化。例如,按自然数递增计数,若采用8421码,则数0111变到1000时四位均要变化,而在实际电路中,4位的变化不可能绝对同时发生,则计数中可能出现短暂的其它代码(1100、1111等)。在特定情况下可能导致电路状态错误或输入错误。使用格雷码可以避免这种错误。 |

|

RPRT_Gray_clkA[2:0] |

ClockA,read ptr的格雷码表示,read ptr从clock B送来,RPRT_Gray_clkB信号需要先同步到clock A的上升沿,然后再延时一定的拍数(此处延时是为了让信号更加稳定),得到clock A的read ptr格雷码。 |

|

RPRT_Bin_clkA[2:0] |

ClockA,read ptr的二进制表示,主要用于clockA的full信号的计算。 |

|

|

|

|

Pop |

ClockB,FIFO not empty 且后级模块not full情况下,pop拉高,从某一个entry中读取数据 |

|

Pop_data[63:0] |

ClockB,从异步fifo的某一个entry中读取的数据。 |

|

Empty |

ClockB,一般根据WPRT_Bin和RPTR_Bin来判断是否为empty,当满足(WPRT_Bin[1:0] == RPTR_Bin[1:0]) && (WPRT_Bin[2] == RPTR_Bin[2]) 时,表明empty。 |

|

WPRT_Gray_clkB[2:0] |

ClockB,write ptr格雷码 |

|

WPRT_Bin_clkB[2:0] |

ClockB,write ptr二进制码 |

|

RPRT_Bin_clkB[2:0] |

ClockB,read ptr二进制码 |

|

RPRT_Gray_clkB[2:0] |

ClockB,read ptr格雷码 |

一般情况下,两个时钟域的两侧分别对应的是两个不同模块,异步时钟fifo的实现也是一分两半,一部分在clock A,一部分在clockB,两部分之间的信号连接主要有以下。因为push在clockA,pop在clockB, clockA 并不知道clockB pop某一层entry的具体时刻,也就无从控制某一个时刻具体输出哪一层给clockB。故一般做法是,所有entry的数据在clockA和clockB侧都分别进行存储,也就是说clockB可以看到所有entry的具体数据,接口上,clockA的所有entry的数据信号都是output。

|

Signal |

方向 |

|

Entry0[63:0] Entry1[63:0] …. |

Clock A --> clock B |

|

WPTR_Gray |

Clock A --> clock B |

|

RPTR_Gray |

Clock B --> clock A |

本文详细介绍了在大规模ASIC设计中,如何处理跨时钟域数据传输的问题,特别是异步时钟FIFO的设计原理与关键信号作用。包括push与pop操作、数据与控制信号、满空信号计算、格雷码应用及双时钟域间数据同步方法。

本文详细介绍了在大规模ASIC设计中,如何处理跨时钟域数据传输的问题,特别是异步时钟FIFO的设计原理与关键信号作用。包括push与pop操作、数据与控制信号、满空信号计算、格雷码应用及双时钟域间数据同步方法。

377

377

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?