下期预告:fpga工程师快速入门jesd204b协议-CSDN博客![]() https://blog.csdn.net/zh9468y/article/details/147114117?spm=1011.2415.3001.5331将详解如何根据ADC手册计算LMFS参数,并通过Vivado工程演示链路建立全过程。

https://blog.csdn.net/zh9468y/article/details/147114117?spm=1011.2415.3001.5331将详解如何根据ADC手册计算LMFS参数,并通过Vivado工程演示链路建立全过程。

📘本文为JESD204B系列教程首篇,专为FPGA工程师和电子工程专业学生打造。全文采用"先底层后协议"的递进式教学法,帮助读者在接触协议前建立扎实的基础认知。

在学习JESD204B协议前,你需要具备一些高速基础的知识和概念。高数接口的初学者目前可以暂时了解,不需要深入,否则面对庞大的高数接口知识系统,直接劝退。

1️⃣SerDes:高速传输的基石

JESD204B依赖于FPGA内置的高速串行收发器(SerDes),理解其工作原理是实现JESD204B的基础。所谓的GTP/GTX/GTH,其实都是xilinx给SerDes的另一种命名,不同芯片使用的SerDes可能有一些差异,所以有了GTP/GTX/GTH。

1.1 什么是SerDes?

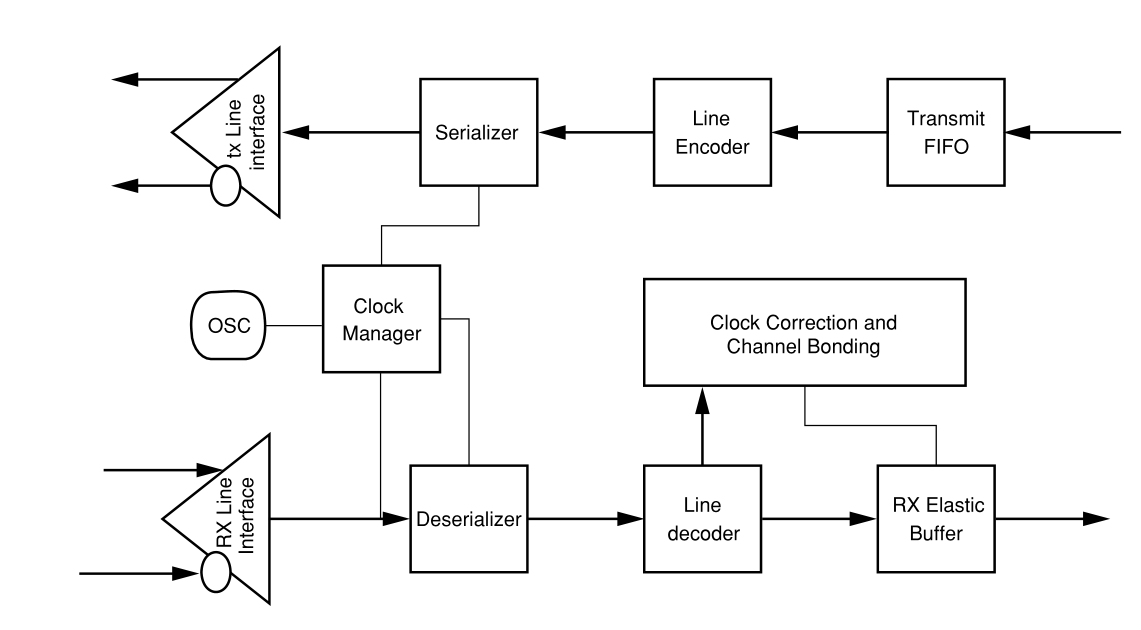

SerDes(Serializer/Deserializer)是高速串行收发器的核心模块,承担着"并行转串行"发送与"串行转并行"接收的关键任务。以Xilinx FPGA为例,不同芯片系列的SerDes命名不同:

| 芯片系列 | SerDes型号 | 典型速率范围 |

|---|---|---|

| Artix-7 | GTP | 0.5-6.6 Gbps |

| Kintex-7 | GTX | 0.5-12.5 Gbps |

| UltraScale | GTH | 0.5-16.3 Gbps |

1.2 发送路径(TX)关键技术

- 并行转串行(PISO):将16位并行数据压缩为串行流。

示例:125MHz时钟下,16位并行数据 → 2Gbps串行速率。 - 8b/10b编码:每8位有效数据插入2位冗余位。8b/10b编码下,数据率为线速率的80%

作用:平衡直流分量(0/1数量均衡)、嵌入时钟信息。 - 预加重技术:提升高频信号幅度,补偿传输损耗,增加眼图开口度,眼图开口度表示信号质量。

1.3 接收路径(RX)关键技术

- 自适应均衡器:自动调整滤波参数,对抗信号失真

常见类型:CTLE(连续时间线性均衡)、DFE(判决反馈均衡) - 时钟数据恢复(CDR):从信号跳变沿提取时钟

精度要求:抖动通常<0.3 UI(Unit Interval) - 通道绑定:多通道数据由于电路走线不同等原因,不一定同时到达,需要相位对齐。相位对其使用对齐标记和缓冲机制实现同步。其中JESD204B协议在此基础上实现更高级别同步

1.4 SerDes的时钟架构

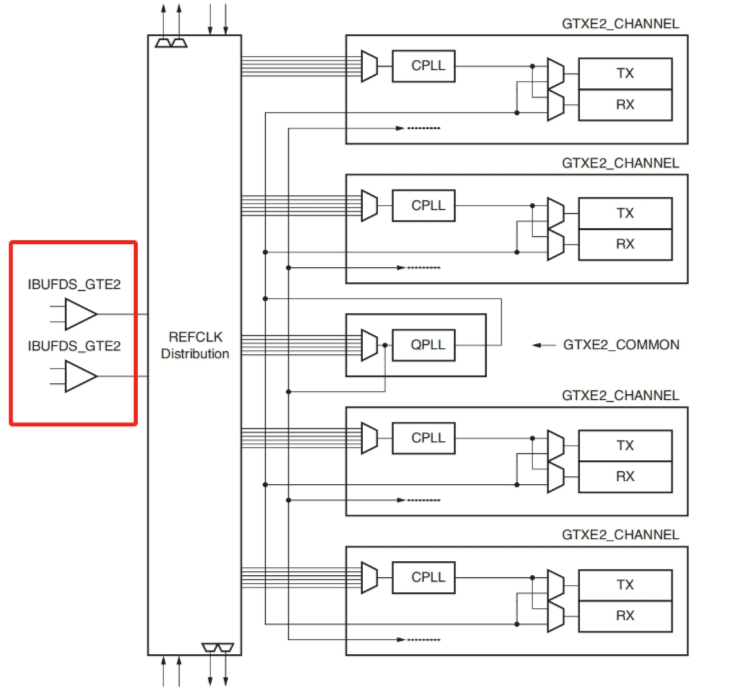

GT的收发器的时钟是非常灵活的,如下图GTX时钟架构:每个GTX的每个BANK有一个QUAD,有4个CHNNEL,也就是4个收发器。每个收发器有一个单独的PLL(锁相环)称为CPLL,这四个CHNNEL也组合为了一个QUAD,一个QUAD里面的4个CHNNEL有一个公共的PLL称为QLL。

每个PLL的参考时钟可以来自用户提供的差分时钟(有两路),但是需要经过IBFDS_GTE2原语(不能使用通用的IOBFDS,区别在于IBUFDS_GTE2用于高速传输的参考时钟输入,IBUFDS用于低速传输的参考时钟输入)转单端,参考时钟也可以来自相邻的其他QUAD (南北各自有两路)。全部就是6个PLL的参考时钟来源可以选择,当然,也可以把本QUAD的时钟共享给相邻的其他QUAD。

这些PLL产生的时钟就是串行化以后的数据的时钟频率,这个频率需要我们在JESD204 PHY 的IP里面配置,这个也就是为什么在第二篇里面会要求计算LMFS计算线速率,就是这个原因。

这5个PLL的控制非常灵活,根据不同的配置和时钟路由组合,可以用于每个收发器(每lane、每差分对,说的都是一个意思) 产生不同线速率,Rx和Tx也可以使用不同的时钟速率。

的通信,一对serdes的Rx和Tx也可以不同的线速率。

QPLL与CPLL核心差异对比:

| 特性 | QPLL | CPLL |

|---|---|---|

| 覆盖范围 | 整个Quad内4个通道共享 | 单个通道专用 |

| 时钟生成能力 | 支持更高线速率(如12.5Gbps)大于6G时选择 | 适合中低速(如3-10Gbps) |

| 相位噪声 | 更低(典型值0.3ps RMS) | 略高(典型值0.5ps RMS) |

| 功耗 | 约200mW(全Quad共享) | 约150mW/通道(4通道共600mW) |

| 时钟同步性 | 保证Quad内各个通道严格同步 | 通道间可能存在微小相位差 |

为什么要高这么灵活?目的是为了适应多种场景。因为有时候4个通道用途和速度不一定相同,有时候还会时候用比如8个同速收发器(如PCIe x8),就需要两个相邻的QUAD的参考时钟都需要同源。

场景1:多通道同速率传输(JESD204B经典场景)

- 案例:4通道ADC@6.25Gbps

- 方案:启用QPLL

- 优势:

- 节省75%的PLL功耗(200mW vs 4×150mW)

- 消除通道间时钟偏移

场景2:混合速率传输(多协议共存)

- 案例:2通道10G以太网 + 1通道PCIe Gen2

- 方案:启用CPLL

- 优势:

- 允许各通道独立设置线速率

- 避免QPLL频率限制冲突

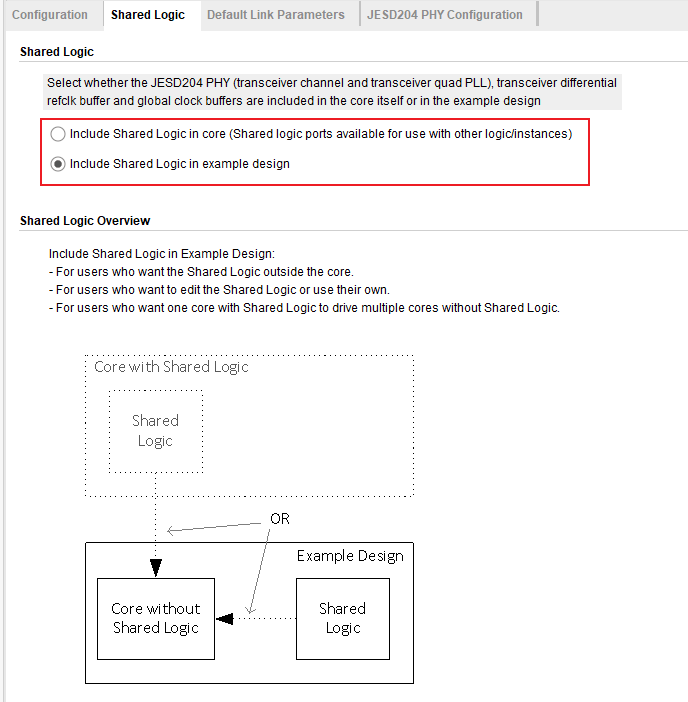

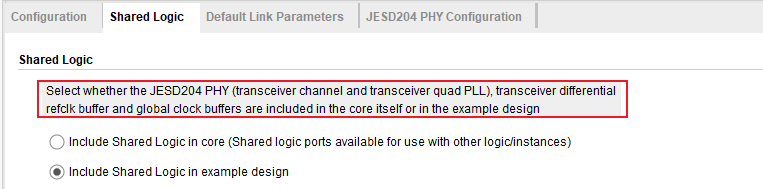

高速接口设计里面,有很多的ip(PCIe/JESD204/以太网等)都有个"Shared Logic"选项:

这两个选项的区别是什么?

| 选项 | 适用场景 | 硬件影响 | 典型应用案例 |

|---|---|---|---|

| Include Shared Logic in core | 单一IP核控制全局资源 | 某些资源内嵌于IP核,但是可能会把资源接口引出,允许其他模块共享。 | 多通道同步系统(如8通道ADC) |

| Include Shared Logic in example design | 多IP核独立工作 | ip内不要这些资源,需要外部资源提供接口给ip,需手动分配。通常是使用其他内嵌了共享资源的ip所引出来的接口。 | 混合速率系统(JESD+以太网) |

配置是可以看到有哪些资源属于共享资源:

这样就明白了,其实就是有些设计需要“混合速率传输(多协议共存)”。

更多使用方法参考:Vivado IP中的Shared Logic到底是干嘛的?_vivado share logic-CSDN博客

DRP技术(了解):

可以看到,这些高速接口虽然都依赖于硬件,但是非常灵活,可以随意的根据需要来设置。但是是不是配置好了就没法变了?

实际上,DRP即动态可重配置处理器,能够动态的调整硬件运算单元的逻辑电路,简单来说就是能够在运行时动态地重新配置部分收发器的设置,而不需要重新编程整个FPGA。这使系统可以灵活地调整收发器的参数以适应不同的通信需求。

2️⃣时钟体系:协议同步的生命线

2.1 三大核心时钟

| 时钟类型 | 作用 | 典型来源 |

|---|---|---|

| Device Clock | 控制ADC/DAC采样以及fpga的时钟,理解为并行数据的时钟,慢。 | 外部时钟芯片 |

| Reference Clock | SerDes 的QPLL/CPLL的参考时钟,用于PLL生成线速率(线速率理解为串化后的数据时钟,快)。 | 板载低抖动晶振 |

| LMFC | 协议层的逻辑同步时钟 | Device Clock分频生成 |

ip的时钟介绍

refclk_n/p:这是CPLL或者QPLL的参考时钟Reference Clock,时钟频率在ip配置时设置。复位,sysref同步信号在该时钟域完成。

axi_aclk:这是ip寄存器配置接口的axi时钟,ip配置时默认100Mhz。

tx_core_clk / rx_core_clk:这是ip输出的时钟,是用户传输(并行L*32bit)数据的时钟。

计算公式为:0.8Lanerate / (32) Lanerate:线速率,0.8:8b/10b编码,32:每次接收每lane的bit数(解码后)。

2.2 同步机制详解

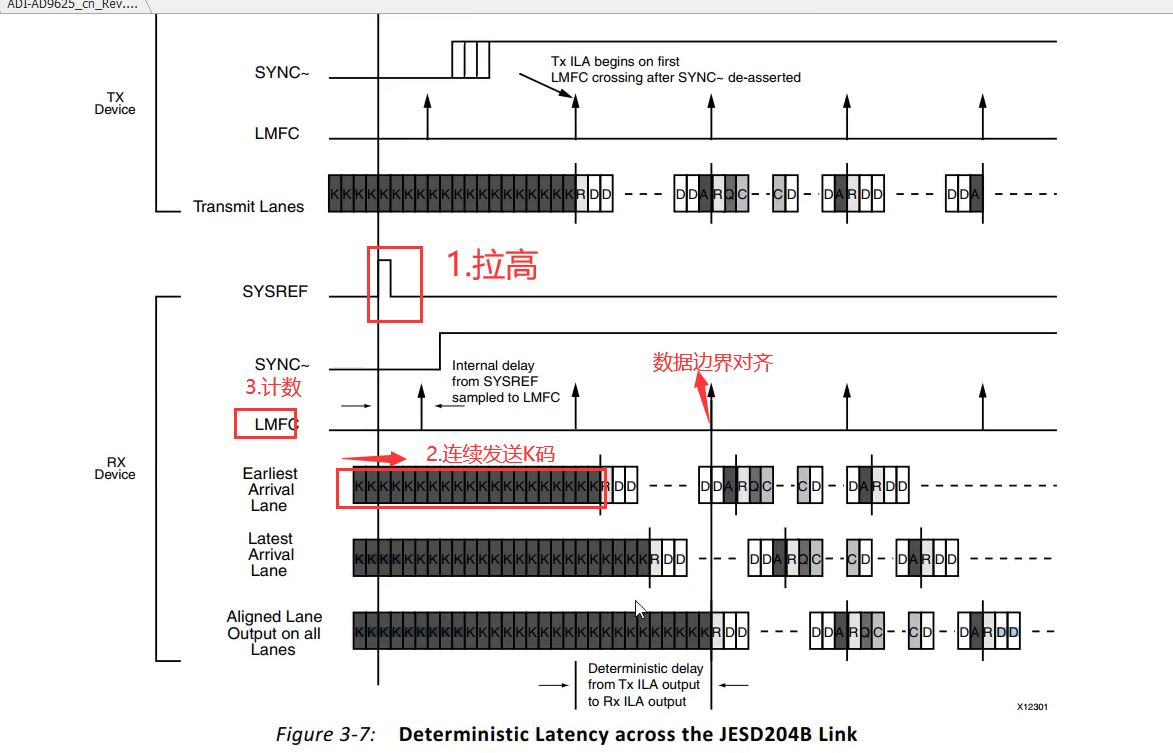

本节内容为ip自动化完成,了解即可。便可理解其完成“确定性延时”的原理。

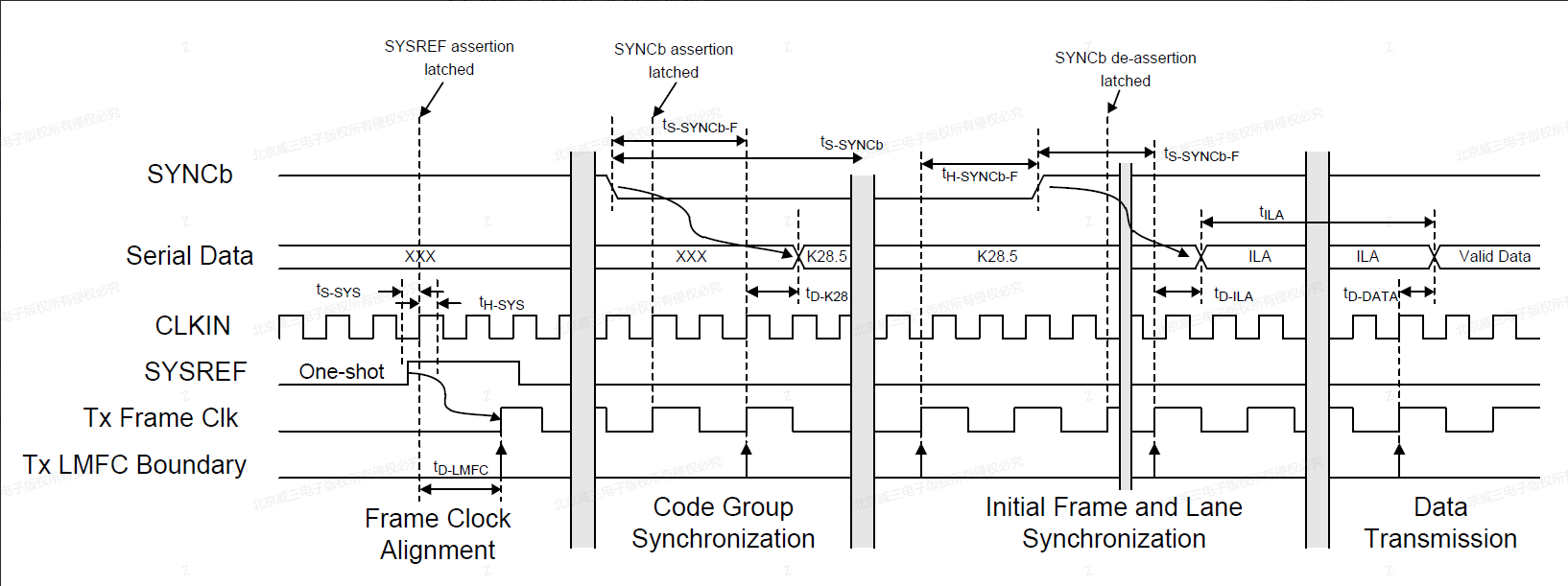

2.2.1 SYSREF触发同步

(该步骤只有子类1才有,子类0和子类2似乎没有。)

在子类1中,SYSREF用于校准Device Clock与LMFC的相位关系,确保确定性延迟。时序要求:

SYSREF信号是芯片时钟提供的,Tx和Rx分别捕获到这个被拉高以后,Tx和Rx各自的帧计数器开始计数(LMFS),计数范围是0~[(K*F)-1],计数到最大值时,LMFS经有一个标志,标志着这一个多帧完成了。

SYSREF需要在tx_aresetn或tx_aresetn拉高以后,才有效,可以是单个脉冲(宽度大于一个deviceclock时钟),也可以是多周期脉冲,但是周期最好是多帧时钟的整数倍。一般配置时钟芯片输出的SYSREF信号为周期信号,大于4倍帧时钟周期。

2.2.2 CGS组码同步

该阶段将完成每条lane串并转换后内部的bit对齐

- Rx端拉低SYNC~信号。

- Tx接收到SYNC~拉低后,移植发送K28.5(0xBC)。

- Rx接收并进行bit对齐,每个lane都连续收到4个K28.5时,说明每个lane分别完成bit对齐。拉高SYNC~。

- 对齐完成后进行ILAS,否者继续等待4个K28.5。

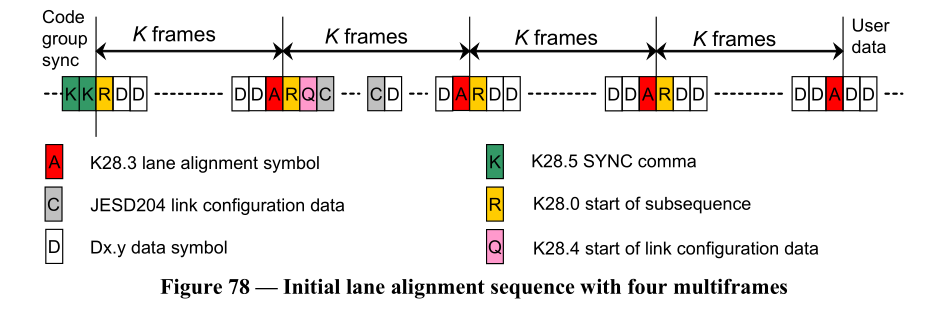

2.2.3 ILAS组码同步

该阶段将完成每条lane之间的同步,Tx通过发送4个多帧来确保Rx对齐所有链路的lanes

-

多帧1:以/R/字符[K28.0]开始,以/A/字符[K28.3]结束。

-

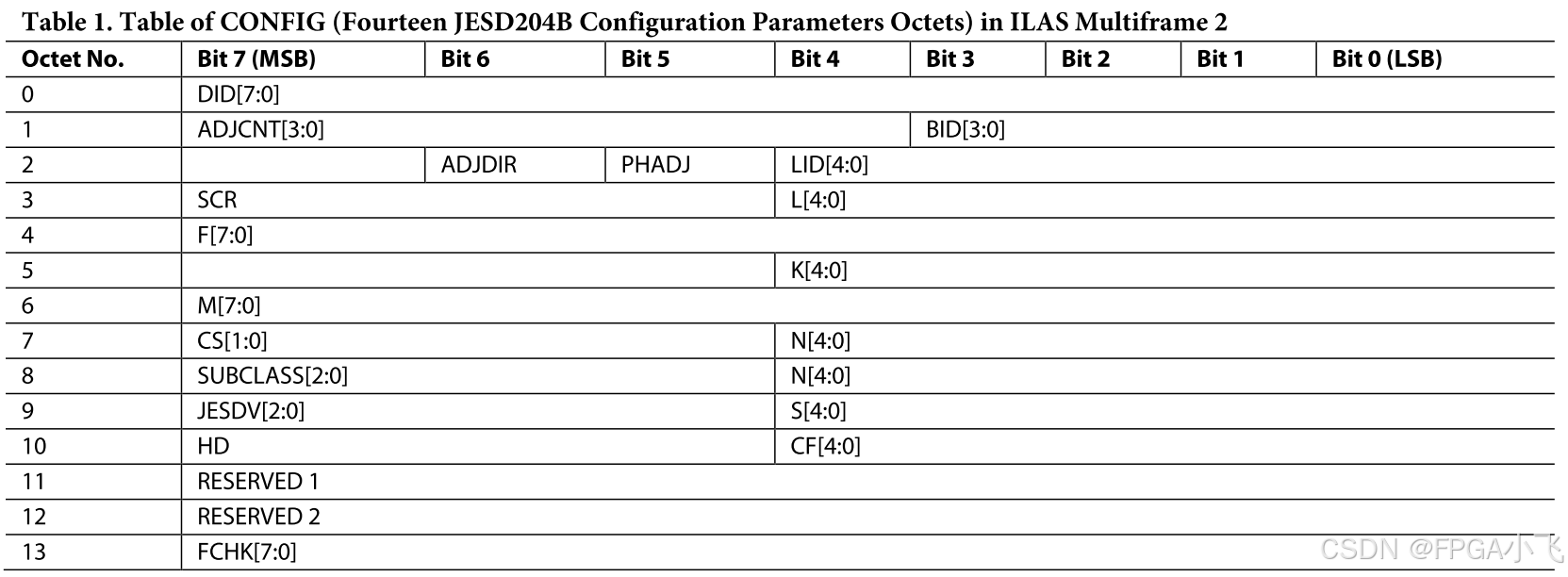

多帧2:以/R/字符开始,紧跟/Q/[K28.4]字符,然后紧跟14个字节的链接配置参数,最后以/A/字符结束。14个字节的链接配置参数可以查器件手册:

-

多帧3:和多帧1结构一致

-

多帧4:和多帧1结构一致

-

Rx确认多通道对齐,进入数据传输状态,就开始传输用户的数据了。

3️⃣8b/10b编码:链路层的守护者

3.1 编码目的

1、将8位数据转换为10位代码,目标是实现直流平衡和足够的比特转换,串行数据中连续出现的1/0达到一个平衡均匀的状态,当高速串行流动逻辑1或逻辑0有多个位没有产生变化时,信号经过交流耦合(高通滤波器)以后就会因为电压位阶段关系而造成信号错误。

2、提供特殊控制字符(K码)用于链路管理

3.2 编码过程拆解

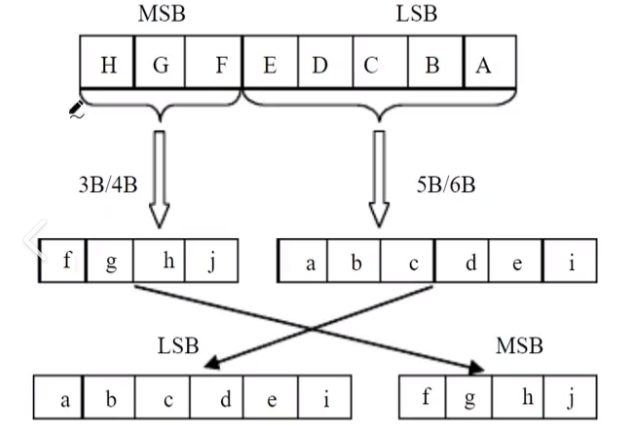

原始数据:8bit → 拆分3b+5b → 分别查表编码为4b+6b →调换顺序为6b+4b→组合为10b

具体的编码可以不用学会,ip已经自动化了,除非你要手搓ip。编码过程可以了解:SERDES关键技术总结-腾讯云开发者社区-腾讯云

3.3 关键控制字符

| K字符 | 编码值 | 用途 |

|---|---|---|

| K:K28.5 | 0xBC | 通道对齐、逗号检测 |

| R:K28.0 | 0x1C | 帧起始/结束标记 |

| A:K28.3 | 0x7C | 多帧边界标识jesd |

| Q:K28.4 | 0x9C |

355

355

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?