📘 JESD204B入门到实战:FPGA工程师必学的高速接口协议

如果你是初学JESD204B的工程师/学生,这篇教程将带你系统掌握:

🔹 协议核心:从并行接口痛点出发,图解JESD204B如何用较少对线替代多对根并行线,深入CML电平、弹性缓冲、确定性延迟等关键技术。

🔹 参数计算:手把手拆解LMFS公式,结合ADC手册实例计算线速率,搞懂8b/10b编码的20%带宽代价。

🔹 Xilinx实战:

1️⃣ IP核配置五步法(TX/RX模式选择、共享逻辑取舍)

2️⃣ PHY层与GT收发器对接技巧

3️⃣ 手把手数据回环工程搭建(附赠仿真调试技巧)

🔹 底层原理:SerDes工作机制、ILAS同步流程、多通道对齐原理,拒绝“黑盒”操作。

本周更新完整工程代码与仿真案例,建议收藏后结合开发板实操!从协议理论到上板调试,打通JESD204B全链路学习路径。 💻🔧

一、快速了解JESD204B

1️⃣jesd204b是什么?

JESD204B 是 JEDEC(联合电子设备工程委员会)发布的一个高速串行数据接口标准,专门用于高带宽数据传输,常见于 FPGA 与高速模拟器件(如模数转换器 ADC、数模转换器 DAC)之间的接口。具体来说,它是一种 串行化协议,将大规模并行数据流转化为串行数据流,以便通过较少的物理信号线进行高效传输。

这个协议在2011年发布,是JESD204和JESD204A的升级版本。

JESD204B的核心思想是用少量高速串行差分对取代传统的大量并行数据线,从而在高速数据传输应用中提供更高的带宽密度、更低的功耗和更简单的PCB布线。

想象一下,如果你需要实现一个16位、8通道的ADC与FPGA的连接,使用传统并行接口需要至少128根数据线(16位 × 8通道),而使用JESD204B可能只需要4对或更少的高速差分线就能完成相同的工作。这不仅简化了PCB设计,还提高了系统可靠性和减少了电磁干扰。

2️⃣为什么用它?

作为FPGA工程师,了解为什么JESD204B越来越成为高速数据转换应用的首选接口非常重要:

想象你家的水管要接32根才能满足用水需求,但水管工说:"我有更牛的技术,用8根粗水管就能搞定,速度更快还不漏水!"这就是JESD204B干的事。

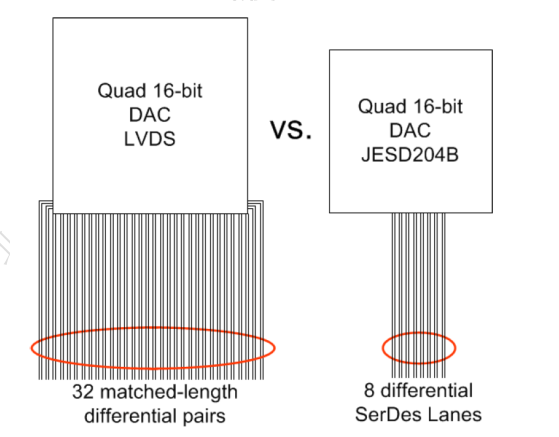

- 传统接口问题:像LVDS接口需要大量IO引脚(比如4通道16bit的DAC要32对等长差分线),布线复杂还容易受干扰。使用jesd204b只需要8个差分对(不要求等长),布线简单还节约IO资源。

3️⃣ 为什么更快?

为什么jesd204b的IO更少,速度反而可以更快?

1. 物理层技术:突破信号完整性瓶颈

LVDS的局限性:

- 电压摆幅低:LVDS采用±350mV的差分电压摆幅,高频信号衰减严重,难以支持长距离传输。

- 速率上限低:传统LVDS的最高速率为3.125Gbps,即使使用SerDes技术,也难以突破物理层对摆幅和噪声的限制。

- 普通SerDes:xilinx的serdes资源有两类,一种是普通 io 的 iserdes oserdes 的 iologic 原语,还有一种是 gtp、gtx、gth…这类高速接口原语。高速接口的serdes当然更快。

JESD204B的改进:

- CML电平技术:采用±800mV的差分电压摆幅,更高的摆幅增强抗干扰能力,支持更远距离和更高频率(如12.5Gbps)。

- 均衡技术:发送端预加重(Pre-emphasis)和接收端均衡(Equalization)补偿高频损耗,确保眼图张开度,避免误码。

- 高速SerDes:集成更先进的串行器/解串器,使用的是FPGA的GT收发器的serdes资源,支持更高线速率(如JESD204C可达32Gbps)

2. 协议层优化:减少冗余开销

LVDS的协议缺陷:

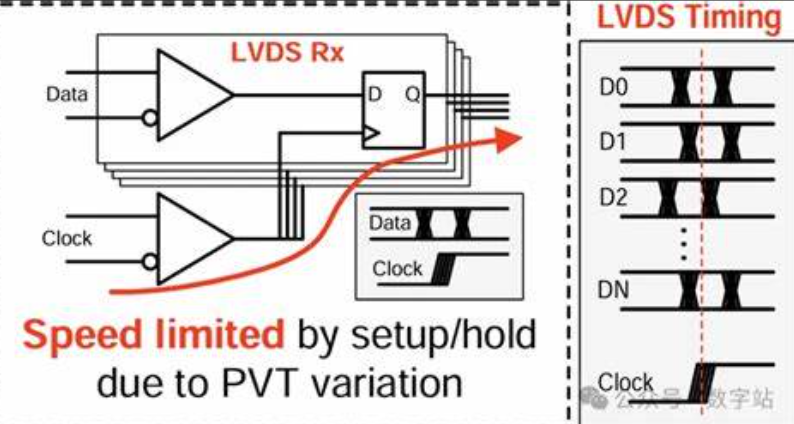

- 同步依赖时钟线:传统LVDS需额外差分时钟线对齐数据,所有差分对的数据采样均在时钟的边沿,但是每个bit(差分对)的数据一般很难同时到达,就会出现bit对不齐,导致接收端的采样错误。为了避免错误,传输速度就不能太高。

- 数据组织低效:并行转串行时需固定拆分规则,灵活性差,无法适应多通道、高分辨率场景。

JESD204B的协议创新:

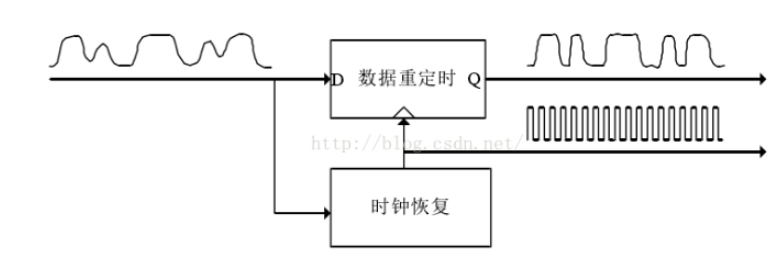

- 嵌入式时钟(CDR技术):通过8B/10B编码嵌入时钟信息,无需独立时钟线,减少干扰源和布线复杂度。也就是说,不需要像LVDS一样所有bit均使用一路同步时钟,jesd204b的所有bit数据里面自带独立的时钟,数据过来的时候,就能从数据里面分离出时钟。并且每个bit(差分对)均分恢复出独立的时钟。这样每bit就能独立采样,保证每次采样的正确性。然后再通过fifo补偿信道偏移,即可。

- 灵活的数据帧结构:通过LMFS参数(Lane数、通道数、帧字节数等)动态调整数据映射,例如:

- 每帧可包含多个采样点(S参数),减少帧头开销;

- 支持多通道数据交织传输,提升带宽利用率。

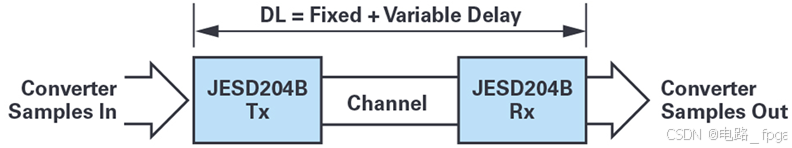

- 确定性延迟:通过SYSREF信号同步多设备,消除传统接口的随机延迟,避免重传造成的速率损失。也就说,从数据被采集开始,经过jesd204b发送、jesd20b接收完成,这整段时间是可以确定的而不是随机的。

3. 系统级设计:解放布线约束

LVDS的布线难题:

- 严格等长要求:LVDS需确保所有数据线与时钟线长度匹配,否则会导致时序偏移(Skew),在高速下难以实现。

- 通道数爆炸:16位ADC需32对LVDS线(16数据+时钟/控制),PCB层数和面积需求剧增。

JESD204B的降维打击:

- 弹性缓冲(Elastic Buffer):接收端使用CDR技术结合FIFO补偿信道偏移,允许不同Lane的布线长度差异,无需手动等长。

- 线数大幅减少:同样16位ADC,JESD204B仅需4条Lane,减少87%的I/O数量,降低串扰风险。

4️⃣有什么缺陷?

jesd204b这么完美?为啥LVDS使用的还是比较多?因为速度不高的情况下,lvds还是比较好用点些。因为jesd204b也有一些缺陷:

- 需要复杂的高速接口支持,IP需要license(收费)。

- 需要特殊的时钟电路,发送和接收端,通常需要同源系统时钟。

- 接口传输延时变大。

二、快速理解关键参数

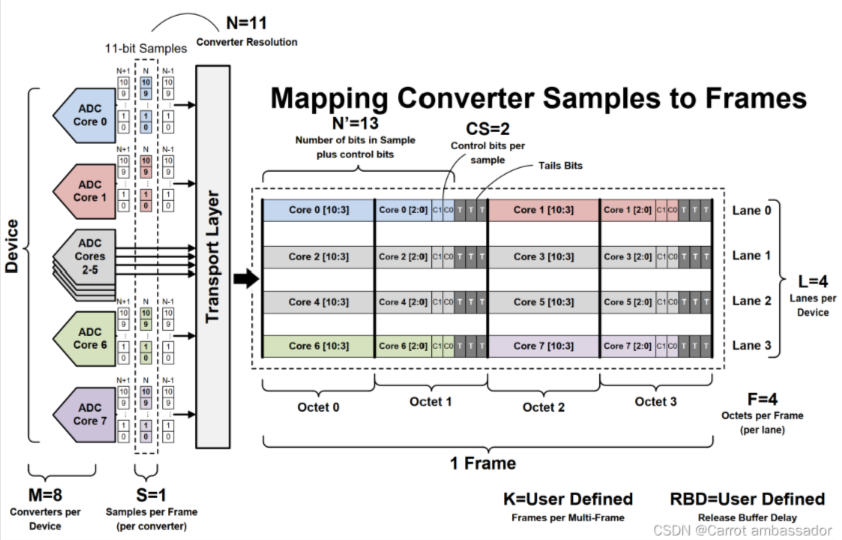

目前,你大致已经了解一些jesd204b,但是还是一头雾水,根本不知道怎么用。你发现许多文章都有介绍L、M、F、S,甚至还有K、N、N’。这些是干嘛的?其实这是用于计算计算线速率的,在建立IP的时候,也需要使用这些参数来配置。这些参数在AD/DA手册可以查到。线速率就是每条差分对(lane)每秒钟传输数据量。

这就像快递小哥的装车规则,记住这个公式:

(最后乘以10/8是因为用了8b/10b编码,把每8bit数据编码成为10bit数据,后面有讲为什么)

- L (Lanes):物理通道数,比如用4条高速线就是L=4

- M (Converters):ADC/DAC的物理通道数,比如8通道ADC就是M=8

- F (Octets per Frame):每帧中,每个Lane包含的字节数。

- S (Samples per Frame):每帧包含的样本数(采样点),通常与M相关。

- Fs(sampling frequency):AD/DA的采样率,也就是每秒钟的样本数。

这个S比较难理解,单独解释一下,AD/DA芯片是每个系统时钟周期就采样、转换一次,而这个系统时钟(device clock)的周期也是每个帧(Frame)的周期,可是一个时钟周期怎么传输这么多数据的?其实这里就是串化了,每个系统时钟的,经过串化以后,都需要将所有通道的数据组成一个帧在一个系统时钟周期内发送出去。所以S既是每个系统时钟含有的样本点数,也是每一帧数据里面包含的样本数。

比如该图片的参数下,若DAC采样率为150Mhz,则线速率是多少?

在高达6Gbps的线速率下,当然得使用FPGA的高速接口GT资源,这部分内容此处不再赘述,建议自行了解。

三、Xilinx IP核操作五步走

学习了这么多,好像还是不清楚怎么使用jesd204b协议开发项目?实际上xilinx提供了JESD204 PHY和JESD204 的ip可以供我们开发使用。

1. JESD204 PHY IP:高速公路的“收费站与路面维护”

作用:

JESD204 PHY(物理层IP)是硬件工程师的“信号搬运工”,负责处理最底层的物理信号,直接对接FPGA的高速收发器(GTX/GTH/GTY),核心任务包括:

- 串行化与反串行化(SerDes):将并行数据转换为高速串行信号(发送端)或反向操作(接收端)。

- 信号完整性保障:通过预加重(Pre-emphasis)、均衡(Equalization)等技术优化信号质量,确保眼图张开。

- 时钟恢复(CDR):从数据流中提取时钟信号,无需额外时钟线。

举个栗子🌰:

想象PHY就像高速公路的收费站和路面维护团队:

- 收费站(SerDes):将多个车道同时(并行)过来的车辆(数据)快速排队通过收费站(串行化),或从高速出口疏散到多个车道(反串行化)。

- 路面维护(信号优化):填补坑洞(补偿信号衰减)、把货物加固(预加重),确保车辆(数据)高速行驶不失控。

作用:

- 直接驱动GT收发器,生成或接收高速差分信号。

- 不关心协议内容,不关心先后,只确保数据“物理上正确传输”。

2. JESD204 Core(Link Layer IP):交通指挥的“智能调度系统”

作用:

JESD204 Core(链路层IP)是协议工程师的“数据管家”,负责管理JESD204B协议的逻辑层,核心任务包括:

- 链路初始化与同步:发送/接收ILAS(初始通道对齐序列),建立稳定通信。

- 数据帧封装与解封装:根据LMFS参数将ADC/DAC数据打包成帧(发送端)或解包还原(接收端)。

- 弹性缓冲(Elastic Buffer):补偿不同Lane的传输延迟差异,确保数据对齐。

- 确定性延迟控制:通过SYSREF信号同步多设备,实现固定延迟传输。

举个栗子🌰:

想象JESD204 Core就像高速公路的智能交通管理系统:

- 调度中心(链路初始化):指挥所有车辆(数据)按指定车道(Lane)和顺序(帧结构)行驶。

- 集装箱打包(帧封装):将散装货物(ADC采样点)按规则装箱(F、S参数),贴上标签(控制字符)。

- 弹性缓冲带(数据对齐):在收费站出口设置临时停车区(FIFO),确保所有车道的车辆同时到达目的地。

作用:

- 解析或生成符合JESD204B协议的数据流。

- 管理多通道数据交织、链路状态监控。

但是为什么有些文章没有使用JESD204 PHY这个ip?

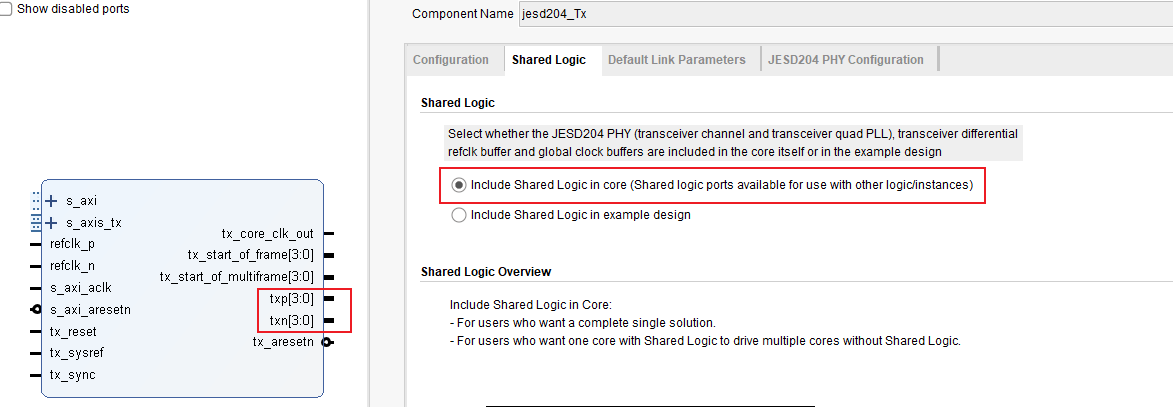

因为他们的代码要么只有发送,要么只有接收,那么就可以在JESD204b ip里面选择在ip内包含共享逻辑(资源)。这样,JESD204b ip里面就直接含有高速接口PHY的资源了,也就不需要JESD204b PHY这个ip了。

而本文是回环设计,收发同时使用,并且还是使用的同一个GT bank(QUAD),收和发的参考时钟是不同的。而JESD204 ip包含链路层,要么只能配置接收、要么只能发送,所以需要把共享的资源(JESD204 PHY)拿出来单独配置,在物理层可以手动配置各种时钟树,可以实现收发不同的参考时钟。因此学会这个回环,单独收、发也就毫无畏惧了。

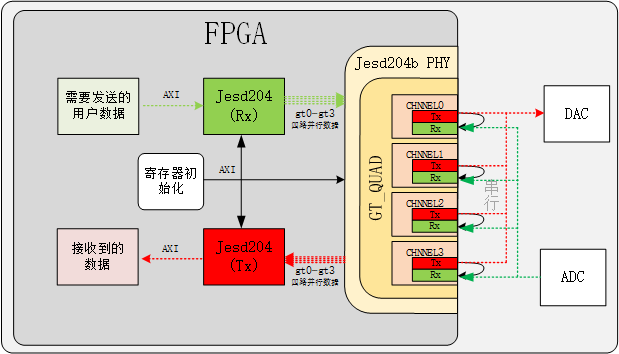

💡相信大家在学习uart协议时,都做过数据回环实验。接下来,本文将使用vivado建立一个基于jesd204b的数据回环仿真工程。如下示意图,仿真时,将Tx直接接回到Rx,实现回环。实际工程开发的话,Tx的硬件引脚是接到DAC等设备,Rx的硬件引脚是接到ADC等设备,当然,根据实际情况可以只发送或者只接收。

本实验,使用了4Lane(4个收发器、4差分对,都是同一个意思),一个QUAD里面是4个CHNNEL,每个CHNNEL有一对收发器。调用JESD204 PHY ip的时候,ip里面就自动会调用这些高速接口了。

发送数据流程(绿色数据链):用户发送的数据使用AXI协议发送到JESD204 IP核(ip配置为Transmit 模式),然后ip经过jesd204b协议封装处理后,将并行的数据传输到JESD204 PHY物理层直接对接到FPGA的高速GT bank串化后发送,该示例使用4lane,正好也是一个QUAD中GT收发器的数量:4。

接收数据流程(红色数据链):GT接收器接收到串行的数据,经过JESD204 PHY物理层解串后,将并行的数据给到JESD204 IP核(ip配置为Receive模式)进行jesd204b协议的解析,然后通过AXI协议被用户读取。

寄存器初始化:由于JESD204 IP的某些功能和模式的配置,需要另外一路AXI总线配置其内部的寄存器来实现初始化,所以这部分是实现IP的初始化。

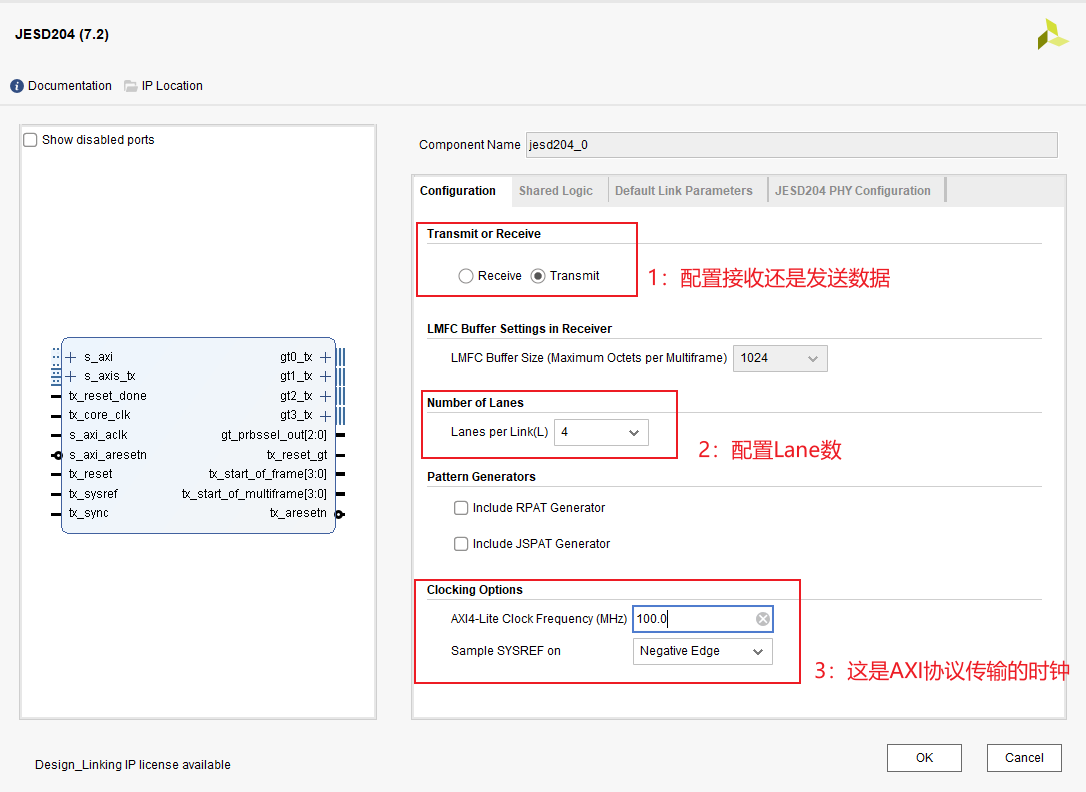

1️⃣ 创建JESD204 IP核

- 以Vivado为例,找到IP Catalog → 搜索"JESD204" → 选择JESD204 IP核

- 配置选项卡(重点参数):

- IP类型:TX(发送端)或RX(接收端),本回环工程需要两个JESD204 ip,一个发送一个接收。

- 通道数:根据硬件选(比如4通道对应一个GTX Quad)

- 共享逻辑:JESD204选择“Include Shared Logic in example design”,这样ip里面就不含有共享资源(PHY)。(这个地方多理解一下,别被“Shared in example design”误导了)。

- LMFS参数:按ADC手册填写,比如L=4,M=16,F=6,S=1,K=32。没有ADC保持默认也可以。

2️⃣ 连接物理层(PHY)

- IP核需要配合JESD204 PHY IP使用(JESD204和JESD204 PHY是两个不同的IP )

- 配置选项卡(重点参数):

- 共享逻辑:JESD204 PHY就选择“Include Shared Logic in core”,让ip里面嵌入共享资源(PLL),否则还需要手动例化一下QPLL/CPLL。

gtx_txdata/gtx_rxdata→ 收发器数据线

sysref→ 同步信号(必须满足与采样时钟的时序关系)core_clk→ 用户侧时钟(通常与收发器USERCLK同源)

3️⃣ 时钟与同步(详细见第一篇)

- 参考时钟:必须用低抖动源(比如Si570时钟芯片)

- SYSREF信号:用于多设备同步(Subclass1必须用)

- 触发时机:IP核复位后发送一次即可

- 注意相位对齐(可用MMCM调整)

- SYNC信号:接收端检测到数据有效后拉高

4️⃣ 数据流对接

- TX端:把FPGA处理好的数据按帧结构打包,通过

tx_data发送 - RX端:从

rx_data接收数据,解析出原始采样值- 重点观察

tx_start_of_frame信号:当F=2时,每16bit数据产生一个脉冲

- 重点观察

5️⃣ 调试技巧

- ILA抓取关键信号:sysref、sync、frame_start

- 眼图测试:用示波器检查收发器信号质量(重点看抖动)

- 误码率测试:发送PRBS码型验证链路稳定性

四、避坑指南

- Scrambling开关:如果ADC不支持加扰,IP核里要关闭Scrambling

- AXI配置接口:大部分参数可在线修改,但初始配置更重要

- 通道绑定:如果多Lane数据错位,检查收发器的RX Slide功能

- 电源噪声:高速信号对电源敏感,建议用LDO单独供电

.......(工程建立在一周内更新完善)

2510

2510

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?