1.概要

随着通讯速度的提升,出现了很多差分传输接口,以提升性能,降低电源功耗和成本。早期的技术,诸如emitter-coupled logic(ECL),使用不变的负电源供电,在当时用以提升噪声抑制。随着正电压供电技术发展,诸如TTL和CMOS技术,原先的技术优点开始消失,因为他们需要一些-5.2V或-4.5V的电平。

在这种背景下,ECL转变为positive/pseduo emitter-coupled logic (PECL),简化了板级布线,摒弃了负电平供电。PECL要求提供800mV的电压摆幅,并且使用5V对地的电压。LVPECL类似于PECL也就是3.3V供电,其在电源功耗上有着优点。

当越来越多的设计采用以CMOS为基础的技术,新的高速驱动电路开始不断涌现,诸如current mode logic(CML),votage mode logic(VML),low-voltage differential signaling(LVDS)。这些不同的接口要求不同的电压摆幅,在一个系统中他们之间的连接也需要不同的电路。

本应用手册主要内容为:TI的不同的SERDES器件,输入输出结构,多种高速驱动器,以及偏置和终端电路。

在不同的接口之间,往往采用交流耦合的方式(ac-coupling),从而可以独立的对驱动器和接收器进行处理。

不同接口之间的转换

不同信号电平的转换

不同地之间的转换

2.各接口电平规范

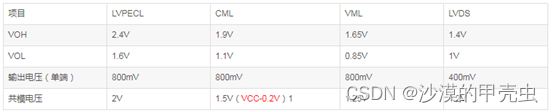

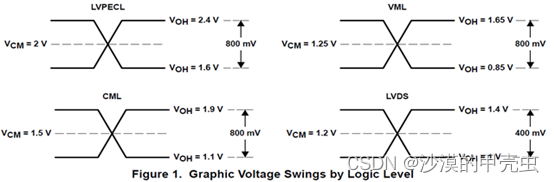

第一步首先是理解各个接口点逻辑电平,主要讨论LVPECL,CML,VML,以及LVDS。 表一为这些接口的输出电平。

2.1LVPECL接口

LVPECL即Low Voltage PosiTIve Emitter-Couple Logic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源。LVPECL的输入阻抗极大,输出阻抗极小,因此驱动能力很强(输出电流大,输入电流小)。想要了解LVPECL电路,我们要首先认知PECL电路。PECL即PosiTIve Emitter-Couple Logic,也就是正发射极耦合逻辑的意思,使用5.0V电源。PECL 是由ECL 演变而来的,ECL 即Emitter-Couple Logic,也就是发射极耦合逻辑。该电路是一种非饱和型的数字逻辑电路,电路内晶体管工作在线性区或截止区,速度不受少数载流子的存储时间的限制,所以它是现有各种逻辑电路中速度快的一种, 能满足高达10Gbps工作速率。ECL 有两个供电电压VCC和VEE。当VEE接地时,VCC接正电压时,这时的逻辑称为PECL;当VCC 接地时,VEE接负电压时,这时的逻辑成为NECL,VEE一般接-5.2V电源;一般狭义的ECL 就是指NECL。由于PECL/LVPECL可以和系统内其他电路共用一个正电源供电,所以PECL/ LVPECL相对于ECL应用更为广泛。起初的PECL器件是将VCC接+5V,后来为了直接利用广泛使用的3.3V和2.5V电压,出现了VCC=3.3V/2.5V的LVPECL(Low Voltage PECL)。

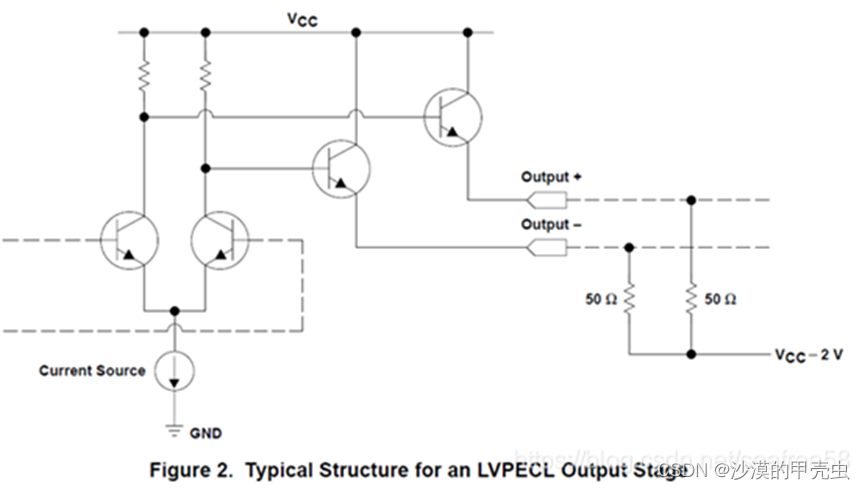

2.1.1.LVPECL 输出结构

LVPECL的典型输出为一对差分信号,他们的射击通过一个电流源接地。这一对差分信号驱动一对射极跟随器,为Output+与Output-提供电流驱动。50欧姆电子一头接输出,一端接VCC-2V。在射级输出级电平为VCC-1.3V。这样50欧姆的电阻两端电势差为0.7V,电流为14mA。(这一部分电路的计算方法我个人理解为,VCC过通过射级跟随器,等效于两个二极管,约为1.3V的电势下降,此时的射级跟随器的基极电压为VCC-1.3V+0.7V。电流源的作用是提高速度。)

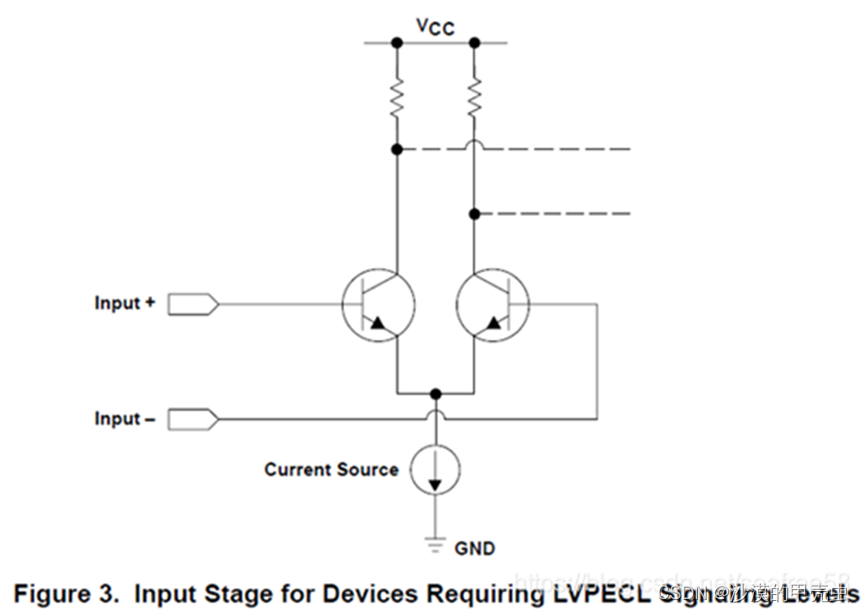

2.1.2.输入结构

输入部分如图三,输入差分对直流偏置电平也需要在VCC-1.3V。在这里要特别注意,关于连接的方式和匹配,在下文详细论述。

2.2CML 接口结构

CML电路驱动器有这样几个特点,包括高速能力,可调整逻辑输出摆幅,电平调整,可调slew rate.

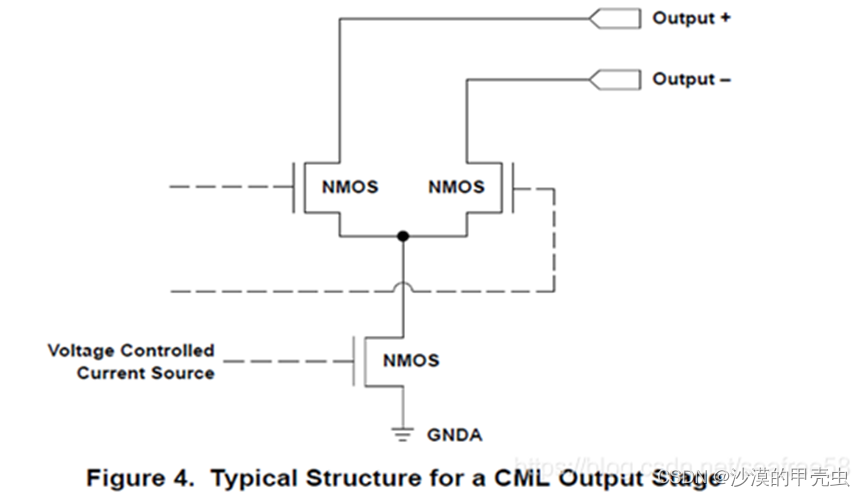

2.2.1.CML输出结构

CML驱动器基于开漏输出和压控电流源使用NMOS晶体管。输出需要通过电阻上拉至VDD,这是因为NMOS只能驱动下降沿。因为输出电压摆幅是由负载决定,压控电流源用于改变电流值从而驱动负载。负载电阻和外部参考电阻可以靠近放置以优化输出电压摆幅。这里说的比较简单,从其他的文献上查得的资料,上拉电阻一般选用50欧姆,电流源的电流为16mA,这样就会有差分800mV的电压摆幅)

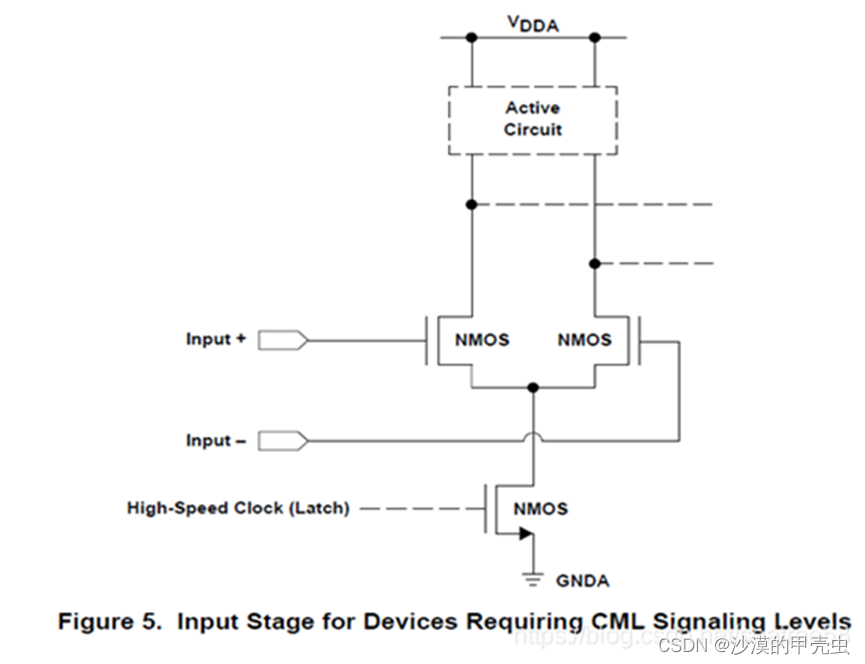

2.2.2.CML输入结构

输入部分需要有上拉电阻将共模电压拉至正常的值。在这里为1.5V当上拉电阻没有包含在芯片中时,就需要特别小心这部分的电路设计。上拉电阻要尽可能的靠近器件。NMOS晶体管在这里作为一个latch(锁存器),配合一个高速时钟,用来锁存数据。(这里好像是针对TI的某个器件来说的,和典型的CML电路有些不同。)

2.3VML 接口结构

德州仪器公司的voltage-mode logic (VML)电平与LVPECL兼容。和CML一样,VML基于CMOS工艺,但VML不需要上拉电阻,以为其内部使用了NMOS与PMOS用以驱动上升沿和下降沿。该电平使用不多,所以不详细论述了。

2.4LVDS接口结构

ANSI TIA/EIA-644和IEEE1596.3-1996定义了LVDS接口标准。LVDS的电压摆幅和速度低于LVPECL,CML和VML,然而LVDS也有其优势,即更低的功耗。许多LVDS驱动器基于恒定电流所以功耗与传输频率并不匹配。(这句话没明白)

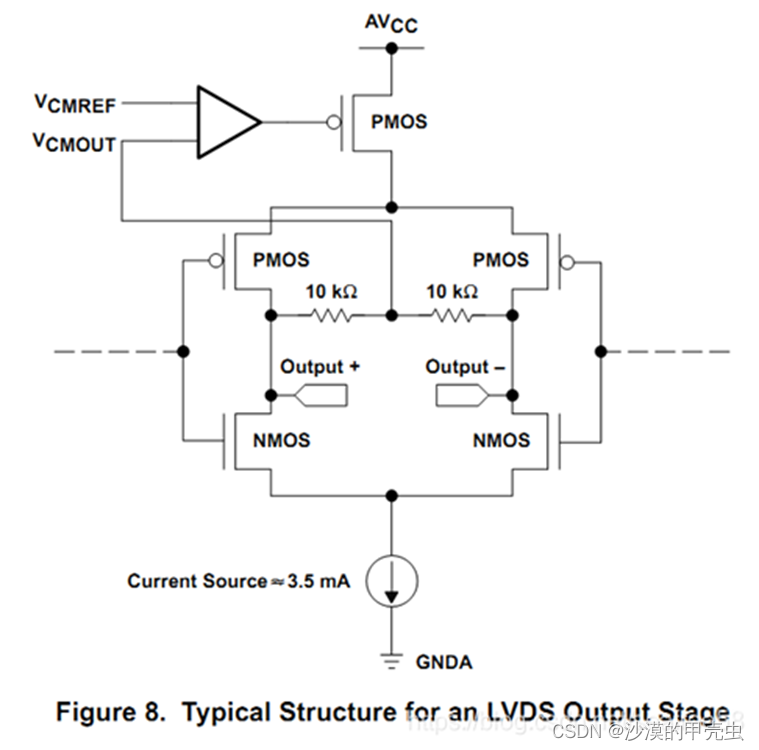

2.4.1.LVDS输出结构

LVDS输出结构与VML类似,只是TI的LVDS SERDES输出结构使用了反馈回路来调整共模电压值。如图8所示,一个电流源与NMOS的漏极链接用来控制输出电流,典型值为3.5mA,通过终端的100欧姆匹配电阻,得到350mV的电压摆幅。

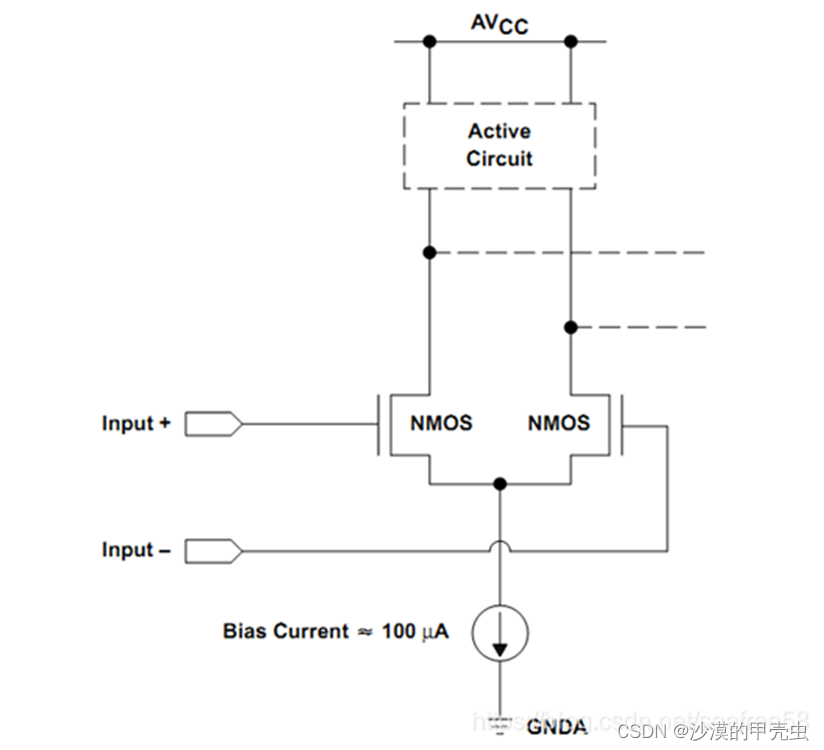

2.4.2.LVDS 输入结构

TI的基于LVDS的SERDES芯片使用差分信号,使用NMOS晶体管,输入必须使用100欧姆的终端电阻跨接于两个差分电平。并且共模电平约为1.2V。匹配电阻必须尽量靠近接收端摆放。电流源用来给差分线提供小电流。

tips:

1、按照标准,CML的共模电压为VCC-0.2V,这个计算是基于电流源电流为16mA,上拉电阻值为50欧姆。为什么Ti这个表格里的这个共模电压是1.5V?这里需要再查阅一些文献看。

2.5HCSL和LPHCSL

2.5.1.介绍

LPHCSL(Low-Power HCSL)是为了降低传统的HCSL驱动器的功耗而开发的。LPHCSL的主要优点包括更好的驱动长线的性能,易于AC耦合,减少PCB板子面积,易于布线,降低材料成本,本文将讨论这些优点,重要的是要注意HCSL驱动器与LPHCSL驱动器对HCSL接收器来说都是一样的。

2.5.2.HCSL与LPHSCL驱动结构

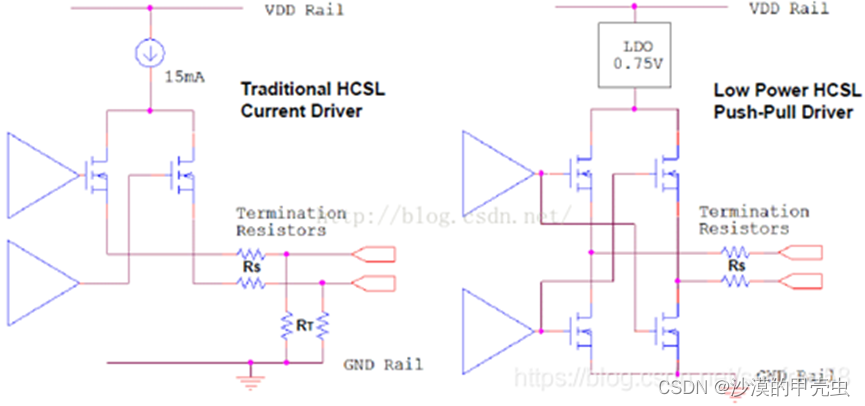

下图为传统的和低功耗的HCSL驱动结构的比较

上图的HCSL和LPHCSL输出结构图,传统的HCSL输出是通过控制正负输出差分对中的15mA电流,显然电源功耗为15mA * 3.3V约50mW。而LPHCSL不是采用传统的HCSL的电流驱动,而是采用推-拉(push-pull)电压驱动,电流消耗大约4到5mA。

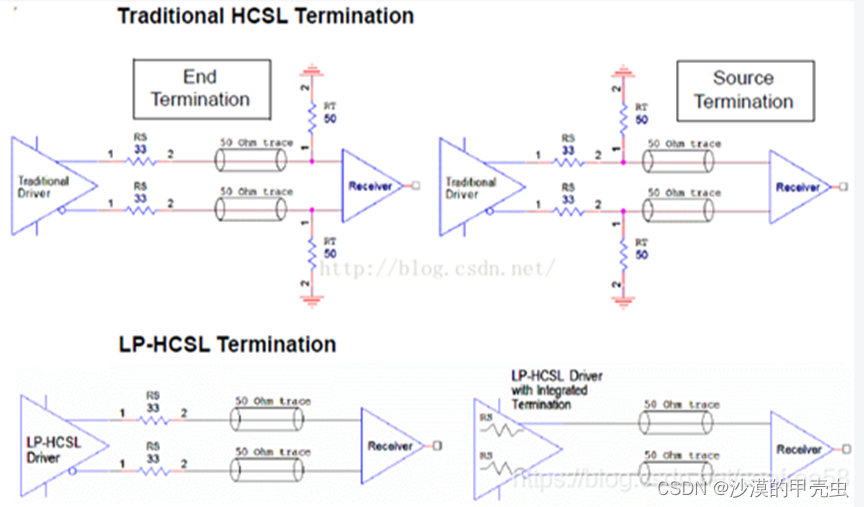

下图显示传统的HCSL与LPHCSL的终端匹配方法:

驱动器本身具有17欧姆的输出阻抗,所以,需要串联一个33欧姆的电阻,以获得与50欧姆传输线的匹配。对于传统的HCSL,为了避免出现过度的振铃,串联电阻RS是必须要的。

某些接收器片内可能有一个100欧姆的差分终端,这样的接收器通常更常见,因为可以处理比较宽范围的幅度和共模电压,以及可能要去AC耦合的时钟信号,LPHCSL驱动器可以稳定驱动双终端(在源和接收处都有终端电阻)。

我们可以看得出LPHCSL并不需要对地的终端电阻。而由于功耗的原因,传统的HCSL驱动器不可能就将终端电阻集成到内部,尤其是芯片有许多输出的时候。很显然,LPHCSL相对于传统HCSL使用了更少的元件,降低了板子面积和材料成本。

从原理上,传统的HCSL要求DC耦合,而LPHCSL并不要求DC耦合。我们可以将AC耦合电容串接到线路上,这样做并不会影响信号的摆幅和终端属性。而传统的HCSL使用AC耦合时,必须仔细考虑对地的DC路径,还可能需要额外增加元件。

PCIe时钟要求的上升速率为0.6V/ns到4.0V/ns,LPHCSL在驱动长线时能提供更高的上升速率。而传统的HCSL驱动取决于外部50欧姆终端来产生时钟的下降沿,这使得上升/下降匹配非常困难,因为仅时钟的上升沿受传统HCSL输出控制,而LPHCSL输出控制时钟的上升沿和下降沿,LPHCSL更快的上升速率对驱动长线时非常重要的。

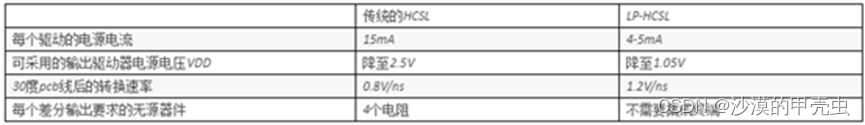

2.5.3.HSCL与LPHSCL对比

LPHCSL不仅显著地降低了功耗,而且能更好地驱动长线,节省板子面积,减少成本,更易于驱动AC耦合传输线,LPHCSL的使用会越来越广泛。

传统的HCSL与低功耗的HCSL比较总结

3.各个端口的连接

直流耦合用于当共模电压不造成问题,且为了避免电容造成的阻抗不连续。

交流耦合用于消除共模电压,主要用于不同的逻辑电平,并假定一个直流平衡的信号模式。

3.1.LVPECL

3.1.1.LVPECL驱动器——直流耦合

直流耦合时,LVPECL需要VCC-2V的终端。当VCC为3.3V时,该电压为1.3V。终端电阻Rt必须和传输阻抗Z0相同。

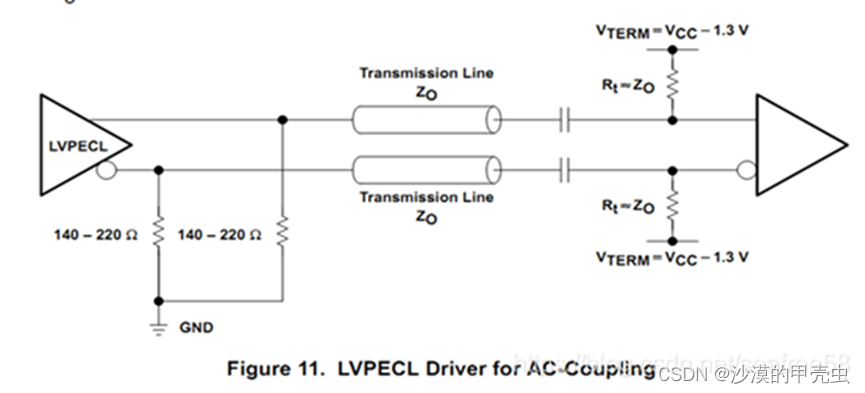

3.1.2.LVPECL驱动器——交流耦合

在交流耦合的情况下,由于没有直流路径供给下降沿信号,所以LVPECL驱动器输出需要通过一个电阻连接至地,这个电阻的大型约在140~220欧姆。在接收端,终端电平必须为VCC-1.3V(5V为3.7V,3.3V为2V)

##3.2.CML

##3.2.CML

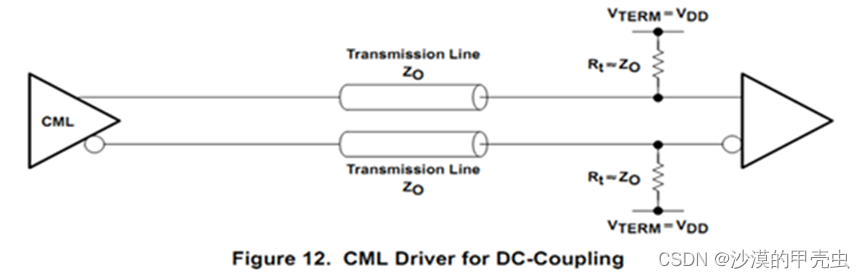

3.2.1.CML的直流耦合

CML的匹配只要加上一个上拉(芯片内未射开漏上拉),上拉电阻等于传输线阻抗Z0。如果芯片内都有上拉,则直接连接即可。

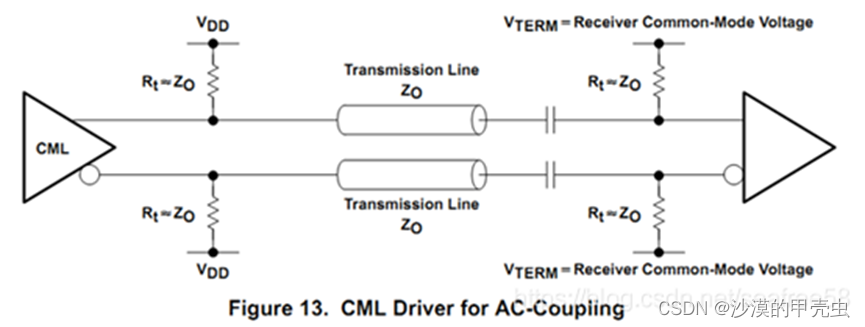

3.2.2.CML的交流耦合

在AC耦合时,需要上拉电阻提供上升沿电平。

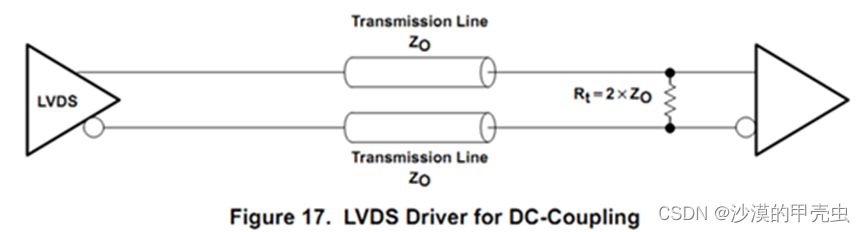

3.3.LVDS

因为LVDS是电流驱动器,所以只能通过DC耦合,电流通过跨接的终端电阻转化为电压信号。典型的来说,差分匹配电阻Rt为100欧姆,但是这个还要根据传输阻抗Z0。(在PCB上Z0一般为50欧姆)

4.偏置和终端电路

4.1.偏置

最简单的偏置电压使用分压电阻网络即可。

举个LVPECL的例子(原文是VML的例子)。3.3V的LVPECL的偏置电压为2V,所以:

3.3*(R2/(R1+R2))=2

可以根据这个算式,算出R1与R2的关系,R1=0.65R2

4.2.终端匹配

对于差分电路,有四种典型的终端和偏置方式,他们有各自的优缺点。

4.2.1.差分匹配

这是最简单的一种,R1和R2用以分压,他们的值在k级别,使得输入共模电平在接收端允许的范围。

该方式的主要的缺点是元器件的数量以及电源的消耗通过分压网络。然而,这种方式可以通过选择更大阻值的R1,R2来降低功耗。

4.2.2.带有去耦电容的差分匹配

第二种方法是和第一种很相似,但终端匹配电阻采用50欧姆,且两个匹配电阻间通过一个去耦电容接地。

这种差分匹配,主要的缺点在于元器件数量和电源消耗;然而,电源消耗可以通过调整R1,R2的值。优点在于,当出现传输线造成的信号歪斜时,比如差分信号并不是同时到达时,该电容可以成为一个对小信号的低阻对地路径。

4.2.3.简化电路

第三种方法如下图22.

理想的配置是使得R1||R2等于Z0。同时满足电阻分压。

可以继续举LVPECL的例子。

算得R1||R2 = 50 又根据上文的关系,可得,R1=82,R2=130

显然,在这个例子里,有更少的R1和R2,但是由于R1和R2的电阻较小,所以功耗比较大。

4.2.4.带一个偏置电阻网络的差分匹配

最后一种方式将偏置网络合并为一个,如图24.

这是一个非常简洁的电路,易于只存在一个分压网络用于两个差分线,减少了电源消耗。去耦电容和匹配电阻消减了电路噪声,和信号歪斜。

当芯片不存在内部的偏置电路时,这种方法是最好的终端和偏置电路之一。

R1和R2在k级的电阻中选,Z0等于传输阻抗。

这种配置时,匹配电阻靠近芯片摆放,偏置电路远离该部分。去耦电容同样必须靠近芯片摆放。

加个补充,来源于网上,提到CML和LVDS的速度问题。

1、CML和§ECL他们的Driver不是工作在开关状态(饱和、截至),而是工作在临界状态,因此他们由low到high的切换过程是很迅速的,同时也正是因为其工作在临界状态,它的静态损耗比LVDS要大,说白了也就是发热大。

2、swing大小的问题,其实这个主要是针对接受器来说,当receiver的容限变大的时候,其允许的传输速度也将会更大。一个很好的例子就是SATA 1.0和PCIE 1.0,其PHY的Driver部分是相类似的,不过PCIE定义的接收电平为85mV(但愿我没记错)而SATA的接收电平为250mV,这样在传输时,PCIE允许的传输速度就大于SATA。

5.参考文献

1、差分晶振LVPECL与LVDS的区别

http://www.ruitairt.com/Article/cfjzlvpecl_1.html

2、LVPECL简介

https://blog.csdn.net/AirCity123/article/details/104146575

3、一文看懂LVPECL终端的设计考虑因素

http://www.elecfans.com/analog/20180514677102.html

4、LVDS,CML,LVPECL,VML之间接口电平转换(来自TI文档)

https://blog.csdn.net/lichao_ustc/article/details/65450803

5、逻辑电平(TTL/CMOS/LVDS/LVPECL/CML)

https://blog.csdn.net/sinat_15677011/article/details/104128903?utm_medium=distribute.pc_relevant.none-task-blog-baidulandingword-11&spm=1001.2101.3001.4242

6、IO接口标准(3):HCSL和LPHCSL

https://blog.csdn.net/shanghaiqianlun/article/details/50553735

————————————————

版权声明:本文为CSDN博主「seafree58」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:LVPECL CML LVDS HSCL LPHSCL电路_seafree58的博客-CSDN博客_cml电路

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?