基于FPGA的FFT算法实现

项目简述

前面的一篇博客我们已经讲解了FFT算法的发展历程,至于FFT的原理感兴趣的同学可以查阅书本数字信号处理,书本上面的知识特别详细,这里我也就不多说了。接下来我们将利用FPGA实现FFT算法,我们本次实验会利用IP核来实现,但是后面的文章会讲解verilog实现FFT过程。

本次实验所用到的软硬件环境如下:

1、VIVADO2019.1软件环境

2、Modelsim10.7c仿真环境

FFT IP的定制及详解

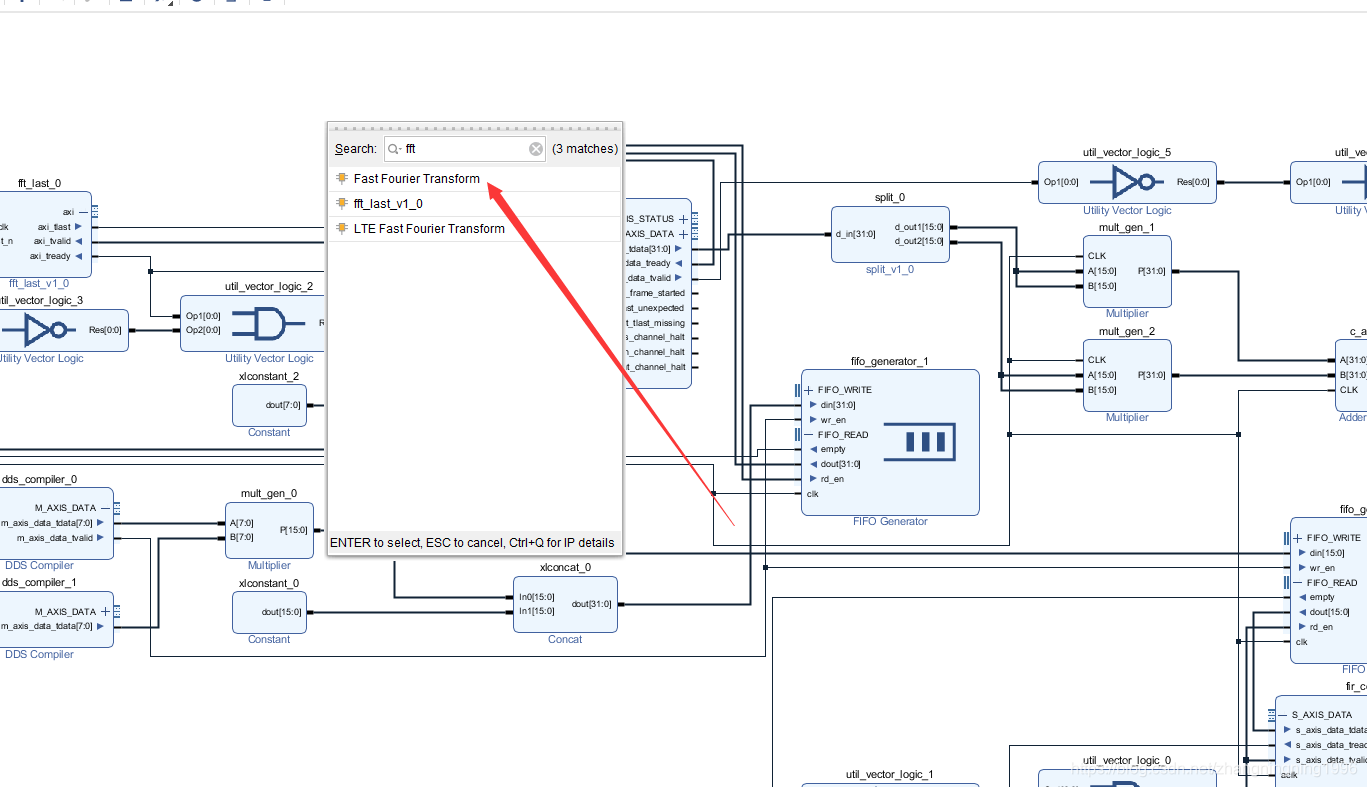

我们找到FFT的IP核如下:

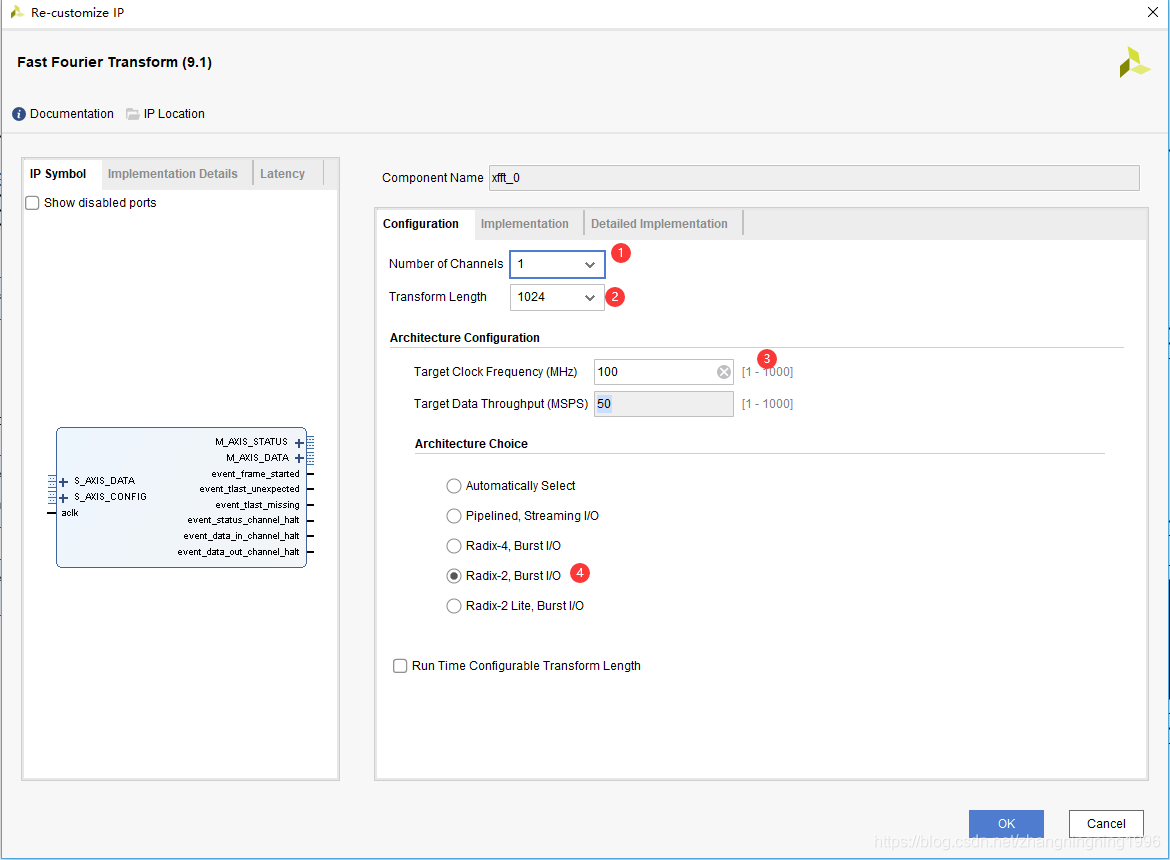

1、这里我们选择1路信号的FFT变换。

2、FFT变换的点数,我们这里是1024点与前面MATLAB中的设置保持一致。

3、模块的参考时钟频率我们选择100MHz。

4、选择实现FFT的算法,我们使用基2算法

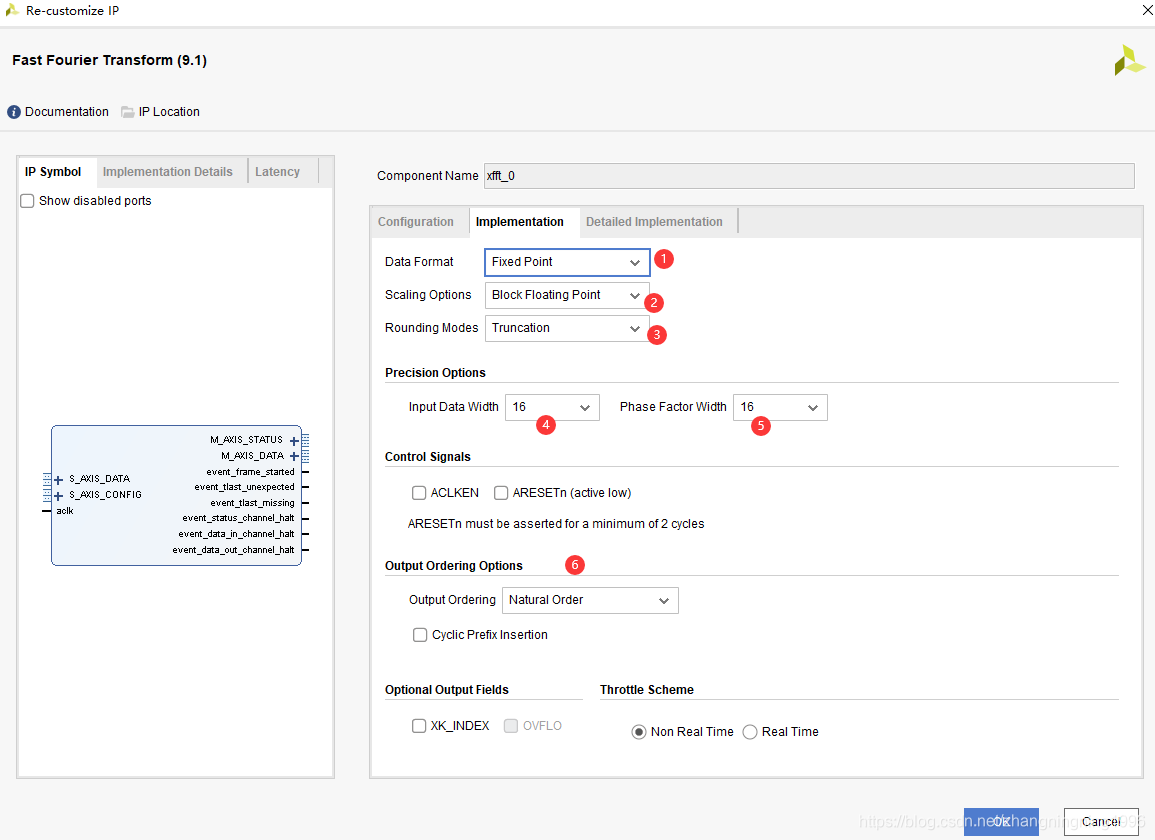

1、我们这里的数据格式选择成定点数即可。

2、缩放比例我们选择成块浮点数,这里是指将FFT每层的运算进行一定缩放,使得最后的结果大小适当。

3、这里选择数据的缩放直接选择截断数据。

4、输入数据的位宽,我们这里选择成16位。

5、相位因子的位宽,这与FFT内部相频的精度有关,这里我们选择默认即可。

6、FFT输出有两种顺序,也就是自然顺序和位反转顺序,我们一般选择自然顺序方便我们之后的处理。

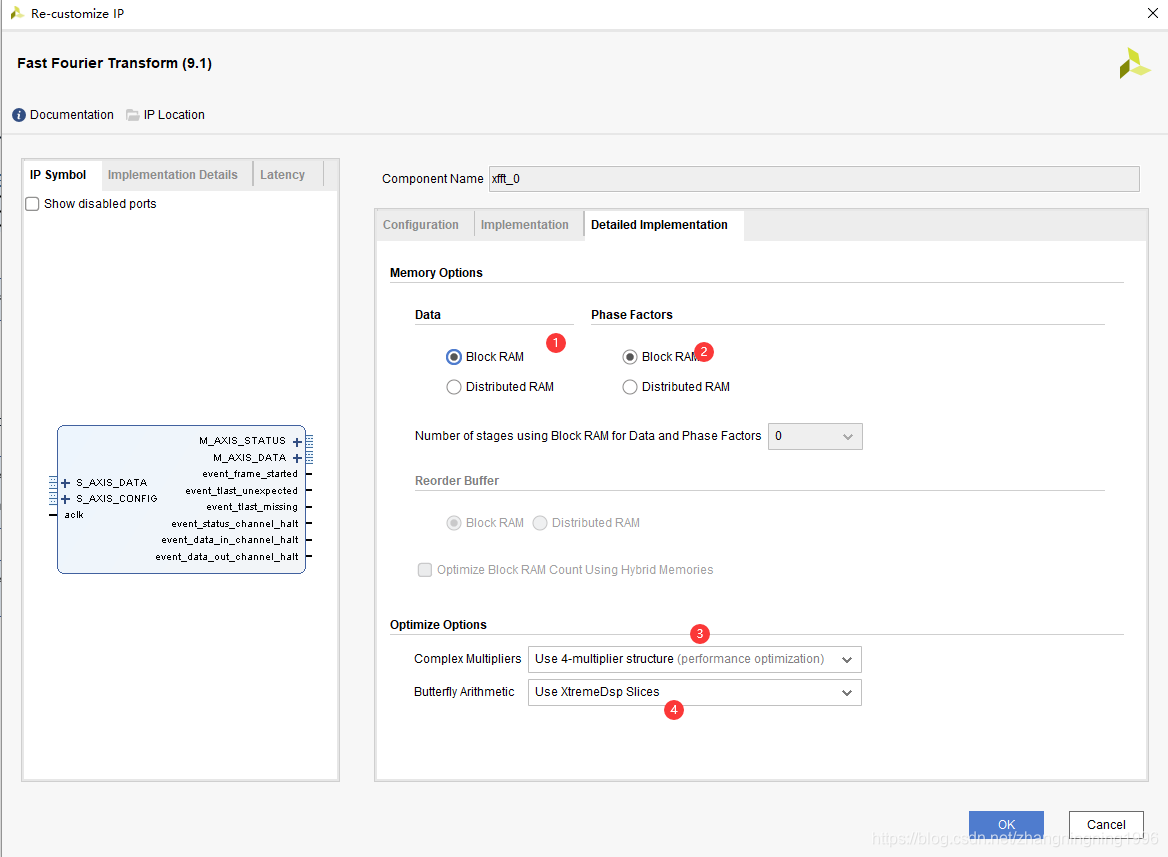

1、数据我们使用块RAM。

2、相位我们也使用块RAM

3、复数乘法我们使用4乘法器结构

4、乘法使用DSP内部的专用乘法器,效果好一点。

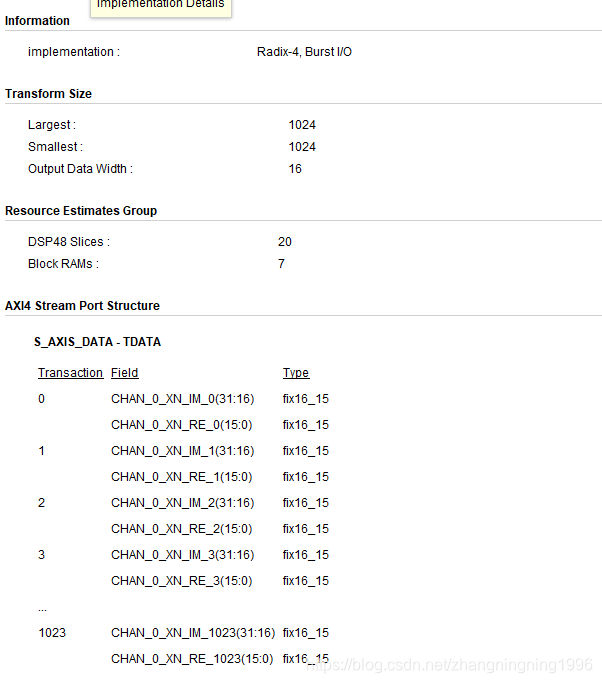

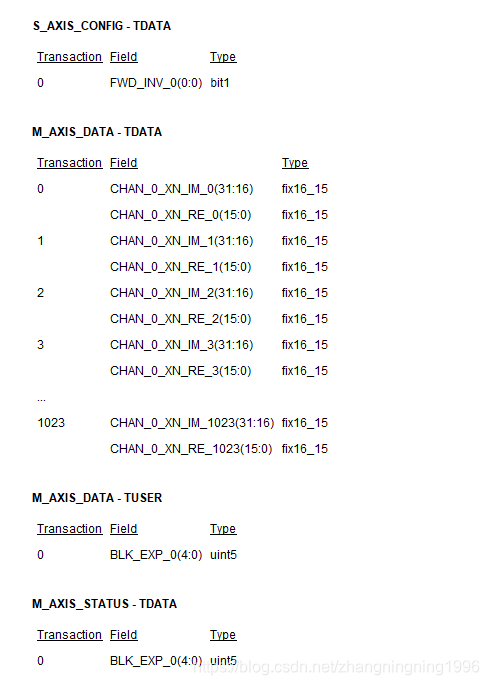

这里我们还要注意IP定制界面的下面信息:

从上面的信息中我们可以看到,输入输出数据的高16位代表复数的虚数位,低16位代表复数的实数位。

S_AXIS_CONFIG输入为1代表傅里叶正变换,0代表傅里叶逆变换。

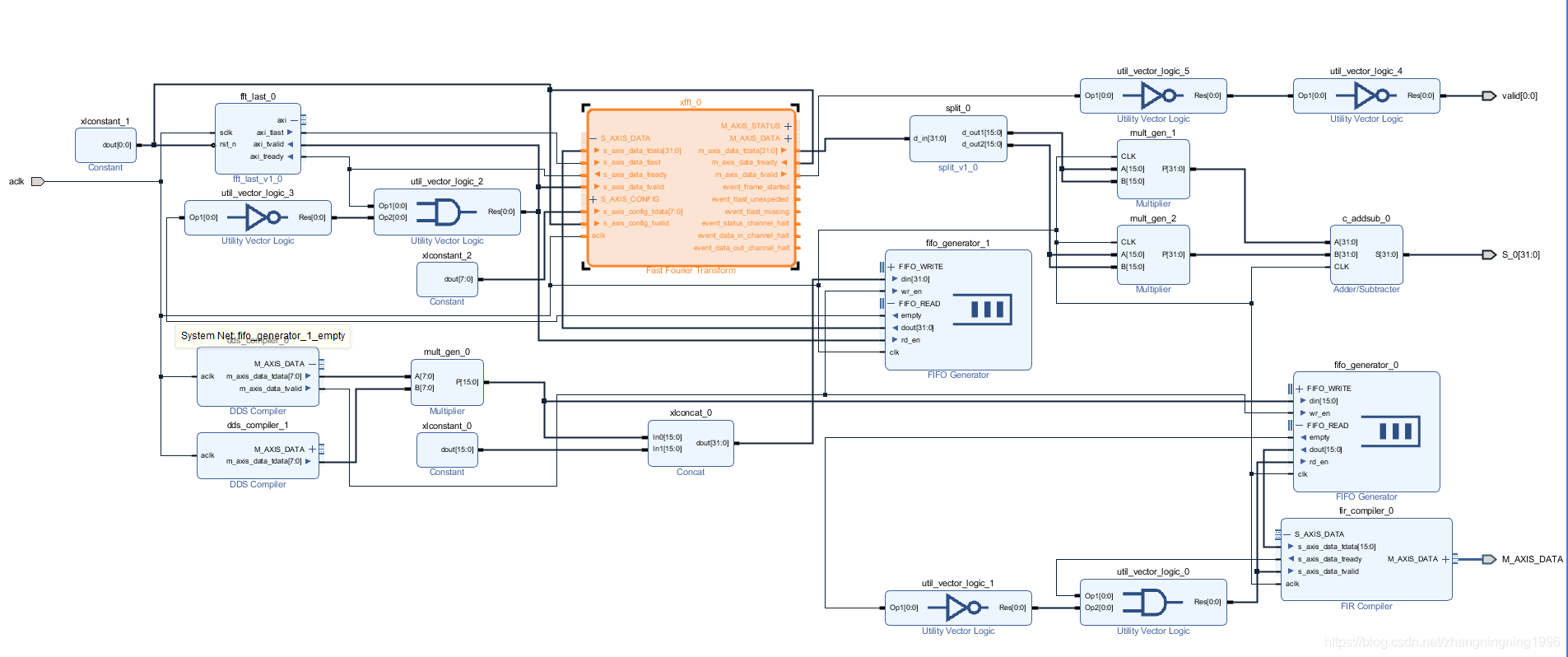

Block Design设计

我们本次实验将继续上次的实验进行讲解。在上一章的block design中加入相应的FFT的IP核,如下:

上面的设计我们严格遵循了AXI-stream的数据协议,当然因为该项目简单AXI中的ready信号一直为高,可以简化设计。同时注意,上面有我们自定义的IP核,代码如下:

fft_last模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : nnzhang1996@foxmail.com

// Website :

// Module Name : fft_last.v

// Create Time : 2020-04-04 22:18:25

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3526

3526

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?