verilog 【控制器-数据通路】建模之Gap_finder

在学习Verilog 的 控制器-数据通路建模,就是把寄存器操作和控制寄存器的信号进行分离,使之形成独立的模块:控制模块Control_Unit,数据通路Datapath_Unit,通过顶层模块进行整合。

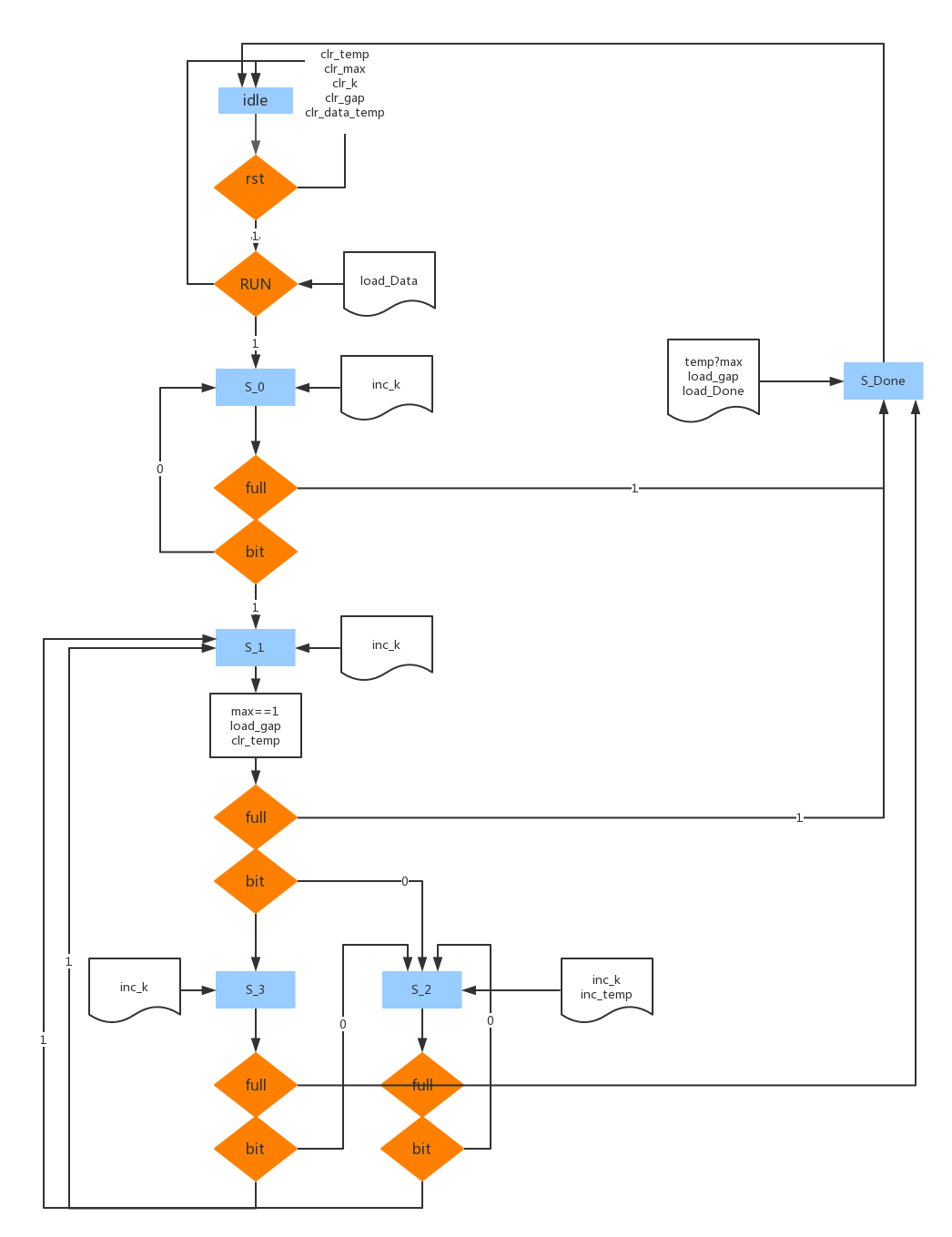

这是对Gap_finder进行的设计,在给定的16bit二进制数据中找到两个1之间0的个数的最大值。即16’b0100_0011_1111_1111中,返回结果应该是4,16’b0100_0010_0010_0101,返回结果是4,而不是3,2,1。

经过流程分析

控制器代码:

module Gap_finder_Controler #(parameter

idle = 8'b0000_0000,

S_0 = 8'b0000_0001,

S_1 = 8'b0000_0010,

S_2 = 8'b0000_0011,

S_3 = 8'b0000_0100,

S_done = 8'b0000_0101

)(

output reg done,

output reg load_data,clr_data,clr_temp,inc_temp,clr_k,inc_k,

output reg load_gap,

input clk,rst,run,full,bit,max);

reg[7:0] next_state,state;

always@(posedge clk)

if(rst==0)

next_state =idle;

else

state <= next_state;

always @(state,run,full,bit,max)

begin

inc_k=0;

clr_k=0;

inc_temp=0;

clr_temp=0;

clr_data=0;

next_state=0;

done=0;

load_gap=0;

case(state)

idle:begin

inc_k=0;

if(run)

begin

load_data= 1;

next_state =S_0;

end

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

883

883

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?