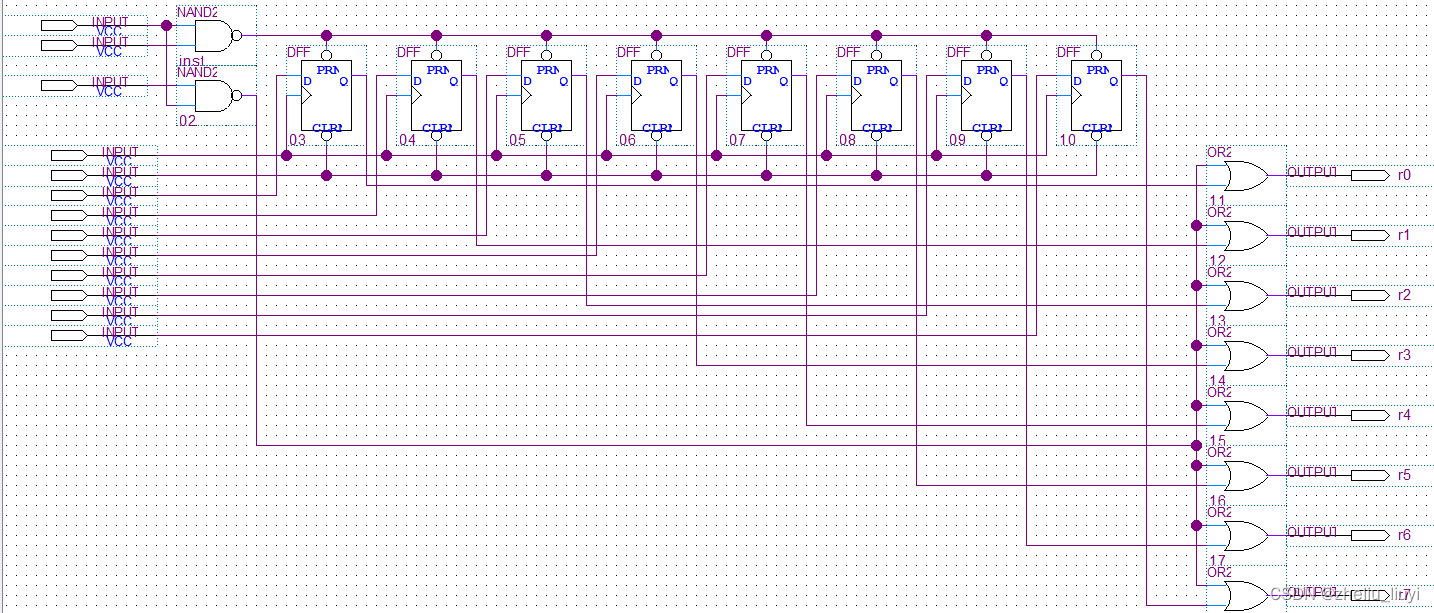

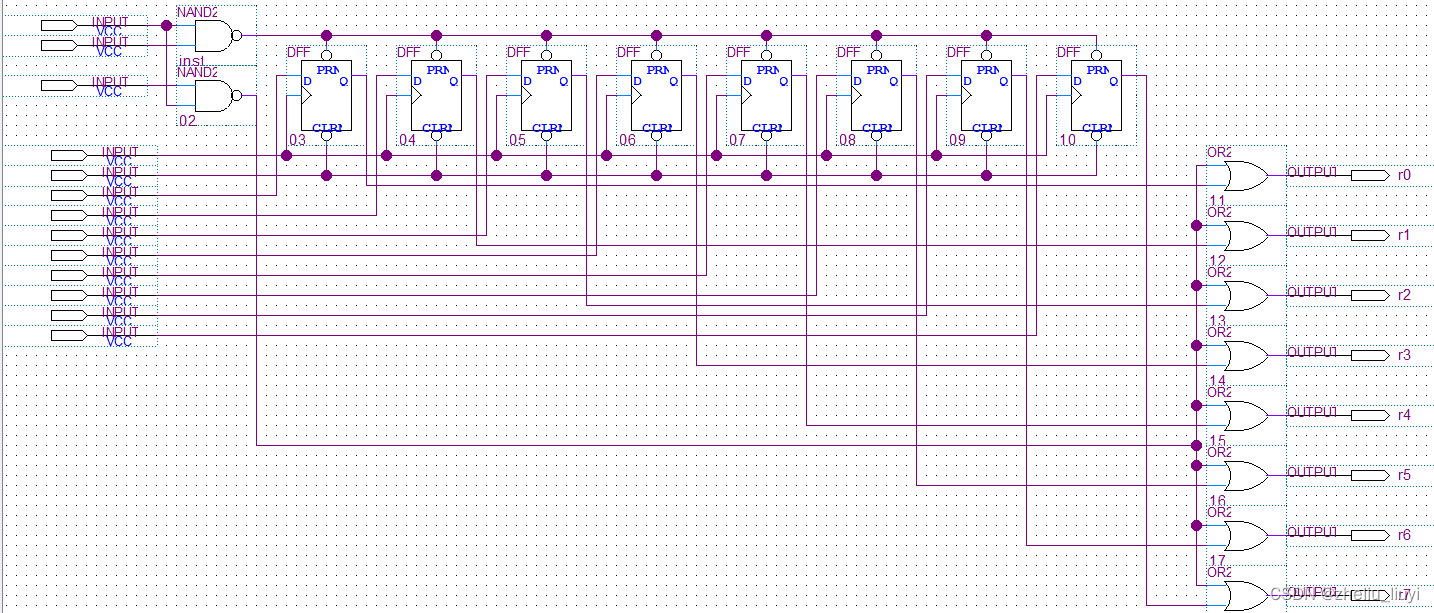

如图先设计8位寄存器,再并联成32位

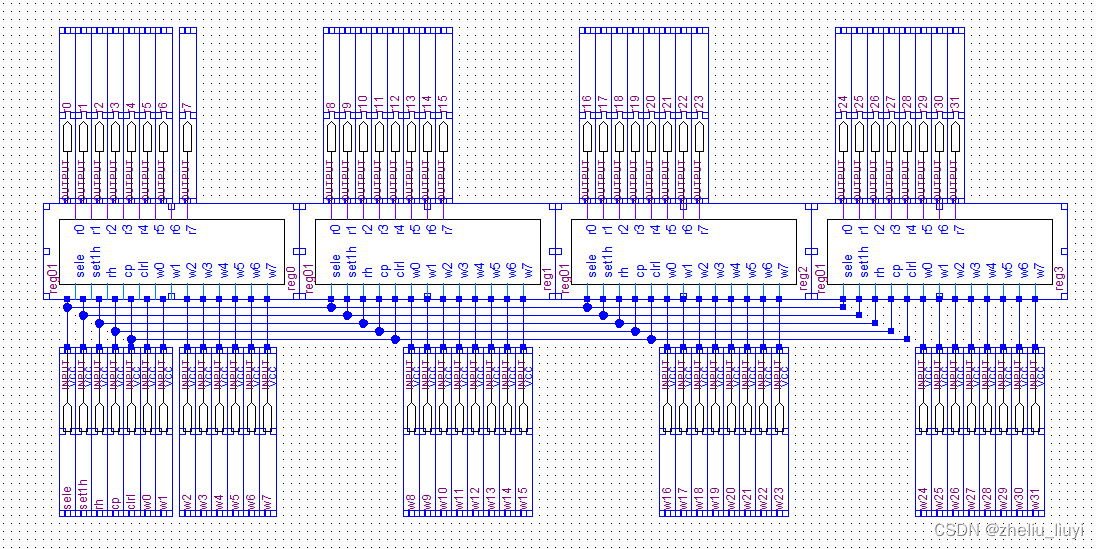

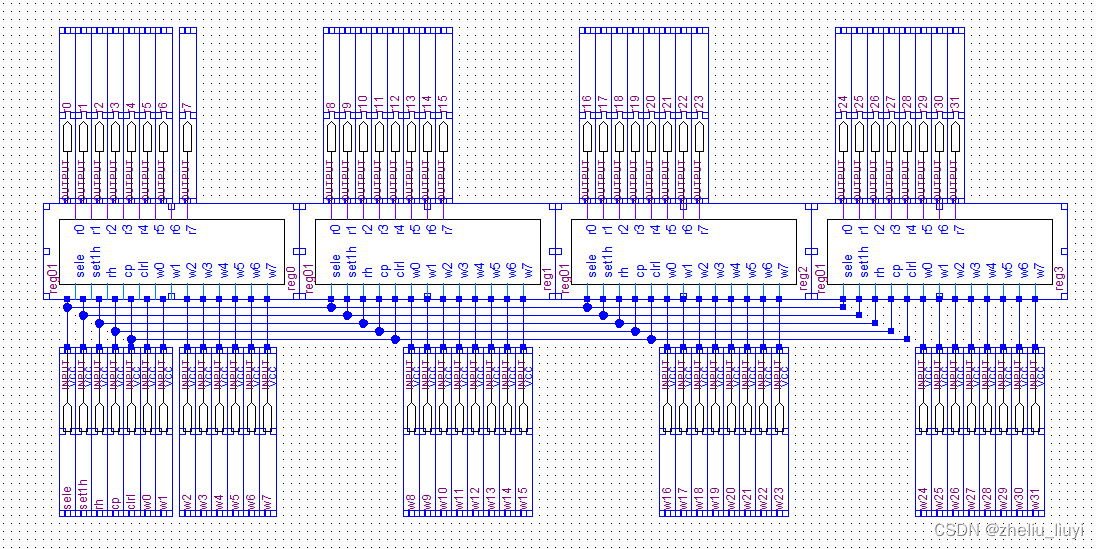

如图先设计8位寄存器,再并联成32位

1731

1731

3575

3575

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?