DEF

现在的综合一般分为logic synthesis和physical synthesis,为了让我们综合出来的netlist和PR做完place& route后的netlist有更强的correlation,目前都会采用physical synthesis

DC TOPO & DC Graphical

这是DC的两种综合模式,DC graphical相比DC Topo mode,有这更强的correlation,并且在综合阶段就考虑到congestion的问题;

我们会在后续的文章中介绍DCG 和DC Topo的区别!

Physical constraints

既然是physical synthesis,那么我们就需要读入physcial constraints,首先通过read_def读入事先准备好的def,然后通过extract_physical_constraints命令抽取DEF中的physical constraints;

下面详细介绍DEF中的相关内容

Macro Location & Orientation

顾名思义,macro location和orientation用于描述design中macro的摆放位置以及方向信息;

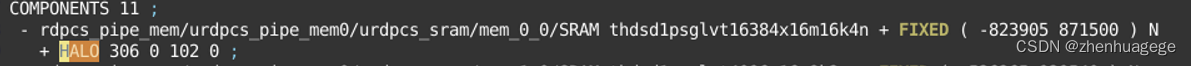

这些信息都在COMPONENTS中描述;

Keepout Margins

在marco和macro执念,有一些区域是不能做place的,我们需要在DEF中描述,通过HALO描述,如下

FIXED

这里的marco用来FIXED来描述,表示这个cell已经出于placed状态了,后续的操作都不能移动他;

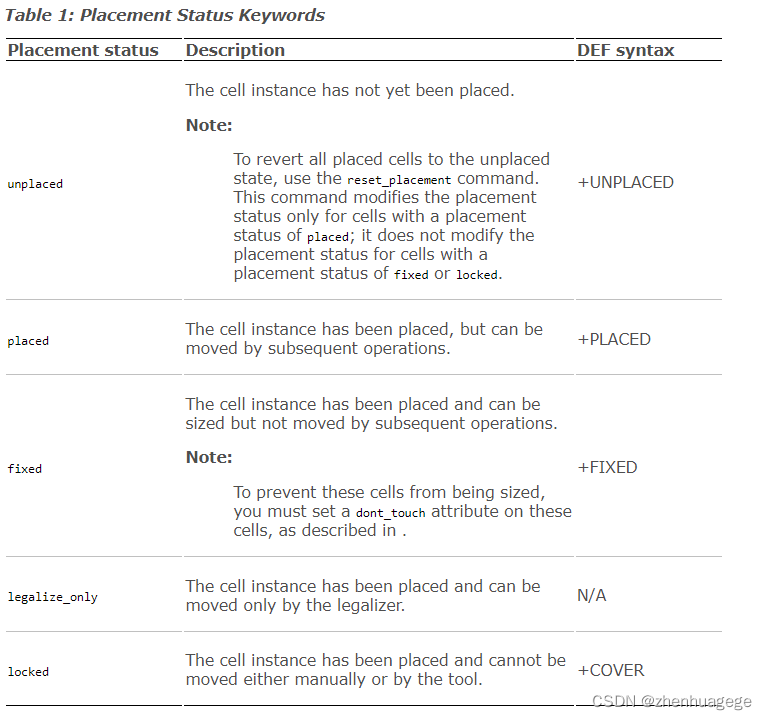

另外,在DEF中,还会有其他的术语来描述cell的place状态,具体如下表

UNITS DISTANCE MICRONS

这个units的值并不是随便定义的,其值应该小于等于Tech lef中指定的值,通常情况下,两者的值应该是相等的,在先进工艺节点下,如果两者的值不相等,会造成VIA 偏移;

下面是DEF中的描述

UNITS DISTANCE MICRONS = 2000;

这里的2000并不是实际的距离,其意义为:

1um = 2000 units;

所以通过这个变量,可以根据DEF中的坐标信息,去计算实际的距离,计算方法为:

实际距离 = 坐标 / 2000;

Placement Bound

placement bound是一个约束,用于控制placement的摆放,通常情况下,在同一个bound区域内的cell,会摆得更近一点;

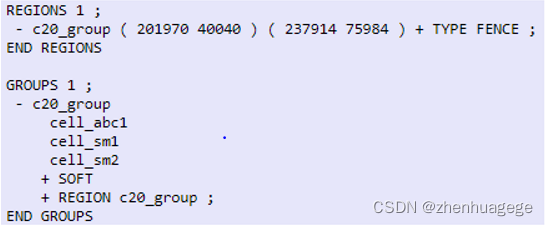

DEF中通过REGIONS来描述bound,并将指定的cell放入该bound中,这些cell通过GROUPS来指定,如下图所示

这里我们创建了c20_group这个placement bound,并指定其type为FENCE,以及相关的坐标;

另外,在GROUPS内指定了三个cell,这些cell关联的placement bound为c20_group,另外,这个bound为SOFT;

Port Location & Orientation

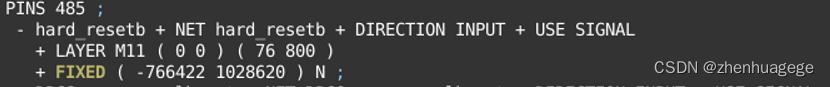

顾名思义,这个变量用于描述design的port的location和orientation信息,使用PINS描述;

例如

这里的port为hard_resetb,其net也是hard_resetb,direction为input,并且还指定了这个net所属的layer为M11;

Site Array Information

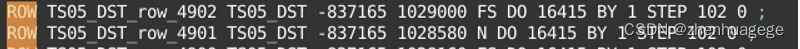

我们知道,site是DEF中最小的单位,用于摆放最小的cell,而ROW则由一行site组成,也可以称为site array,而site arrays就组成placement的area;

上图中的site为TS05_DST;

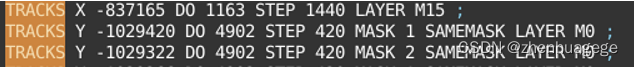

Routing Track

Tracks define the routing grid for standard cell-based designs,也就是tracks用于给standard cell做routing grid;

Tracks是走线的轨道,两条track之间的距离则是pitch;

提供tracks信息,可以更准确得预估congestion,可以让DC和ICC的结果更加接近;

Wiring keepouts

顾名思义,wiring keepouts指的是不能布线的区域

Site name matching

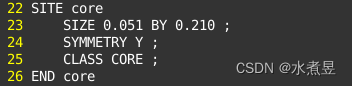

首先是site的定义,如下图

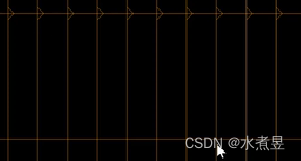

1、这里一行代表Row,而Row内部有很多小矩形,这些小矩形就是Site,也就是说,Row是由Site组成的;

2、工具在横向移动cell时,site最小的移动距离,也就是说,cell移动的距离不能比Site的横向宽度要小,并且移动的距离应该是Site的整数倍距离;

3、Site是最小的standcell的单位;

我们在综合过程中,会读入milkway reference lib,这个lib中也有site unit,DEF中也有site unit,如果两个site unit对应不上的话,需要进行下面的设置

set mw_site_name_mapping {def_site_name mw_ref_lib_site_name}

这里我们设置了三组mapping关系,分别是:

1、CORE & TS05_DST

2、Core & TS05_DST

3、core & TS05_DST

4、unit & TS05_DST

Blockage

Blockage意为阻塞物,在这里就是指防止工具触碰的区域。总的来说blockage可以分为两类:placement blockage和routing blockage。Placement blockage的区域禁止tool摆放cell进来,routing blockage的区域禁止绕线。需要注意routing blockage是要分层的,包括via层也可以上routing blockage。而placement blockage是和cell摆放相关,就不会分层;

Hard & Soft & Partial Blockage

Hard pblk区域是tool不论在任何阶段都不能放cell进来,最终出来的database一定是没有任何cell在hard pblk里的,除非user手动加。Soft pblk指的是tool摆cell的时候不能摆进来,但是之后的legalization和optimization就可以放进来了。Partial pblk就是tool可以摆进来一定数量的cell,其面积不能超过partial pblk所规定的百分比;

Blockage的概念很简单,但确实能帮我们方便地指导tool的工作。比如在很多时候,我们不希望在某些区域出现std cell,我们就会上一些hard pblk。最常见的区域有macro的周围,macro与macro之间的narrow channel,以及macro与core边界围起来的区域,总之,一切可能发生congestion或者IR不好的区域都可以设置blockage;

这里参考了下面的文章:

原文链接:https://blog.csdn.net/weixin_52636726/article/details/122501706

Halo

Halo与Blockage有点类似,也称为或者keep out margin;它不是加在floorplan上的,而是加在特定instance上的。比如我给一个macro加了一个宽度1um的halo,它的作用其实也等效于加宽度1um的pblk;

但是halo是加载instance上的,意思是如果我们移动了instance,其halo也会跟着一起移动,永远保证它周围1um范围不会有cell;而pblk不一样,instance动的话和pblk没关系。

Halo能帮我们方便地处理某些情况,比如我们不希望某一类cell靠在一起,就可以给这类cell左右两边加halo;

OBS

在读取cell或者macro的lef的时候会出现OBS,它是obstruct的简写,其作用就类似于routing blockage。如果这个macro的出pin层就希望直接连via上去,不希望pin层有任何走线,这个macro在设计的时候可能就会把pin之外的所有区域盖上OBS,这样tool在绕线的时候就不会绕到OBS里,所以tool就一定会先打一个via在pin上,再连出来。如果绕线时发生了DRC,经常要检查一下是不是OBS在捣乱

原文链接:https://blog.csdn.net/weixin_52636726/article/details/122501706

Core Area & Die Area

在使用initialize_floorplan创建floorplan时,需要指定-boundary,例如

initialize_floorplan -boundary {{0 0} {800 800}}

这样就创建了一个800800(umum)的floorplan,这里的800*800是指floorplan的Die Area;

而往往Die Area和Core area往往会有一个gap,为什么呢?

答:

因为Core Area和site与row有关,Core area必须是Site宽度和Row高度的整数倍;

而我们在生成Die Area时往往不是Site和Row的整数倍,所以会造成两者之间有gap;

而这个gap我们可以通过**-core_offset**指定,例如

initialize_floorplan -boundary {{0 0} {800 800}} -core_offset {0 0.240}

这就意味着在core和die在Y轴方向上有0.240的偏差;

注意:

横向offset必须是site的宽度的整数倍,纵向offset必须是site高度的整数倍;

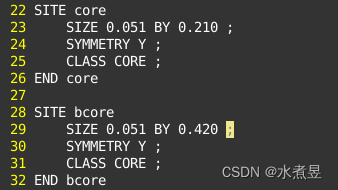

Site在tech lef或者tf文件中有定义;

这里有两种site:core和bcore,其中core的宽度为0.051,高度为0.210;bcore这个site的宽度为0.051,高度则为0.420;

Layers使用方法

在route时,需要用到layer,例如M0到M11,有12层layer,每层layer都有不同的使用方法!

M0 layer

通常来说,M0 layer往往用于做power rail,也就是VDD和VSS;

M1 layer

Legalize

在做place时,摆放cell时,需要判断该该cell是否legalized,那么判断cell是否legalized的条件是啥?

答:

1、首先要判断cell是否在Row上;

2、cell要和site对齐,在横向移动cell时,需要移动的距离应该是Site的整数倍;

3、cell的宽度必须是site横向宽度的整数倍;

4、cell的高度必须是Site高度的整数倍;

5、不能和其他的std cell有overlap;

6、不能有spacing规则的违反;

7、cell orientation必须与Site规定的一致;

Cell orientation

Orientation也就是朝向,这里我们指的是std cell的朝向,cell的朝向会影响其pin的位置以及对应的连接关系;

对于已经摆放好的cell,可以通过orientation这个属性获取其朝向;

目前orientation允许的值包括:

1、R0

2、R90

3、R180

4、R270

5、MX

6、MXR90

7、MY

8、MYR90

其中,R0,R180,MX,MY用的比较多;

那么这些值代表的实际意义是什么呢?

答:

R所代表的的意义就是Rotate,也就是转,后面的数字就是代表这个Cell转多少度;

M则是Mirror的意思,就是镜像,MX也就是以X轴做镜像,MY则是以Y轴做镜像;

为什么做cell orientation会失败?

Site & Row是有legal orientation的,也就是当前Site所允许的orientation是有限制的,比如说这个site的legal orientation只允许R0这个orientation,那么我们对这个cell做其他类型的orientation就会失败;

那么能不能添加site的legal orientation呢?

答:

可以,在tech lef中我们可以查询site的信息,如下图

这里可以看到core这个 SITE的SYMMETRY为Y,也就是说这个SITE是支持Y轴镜像的,如果是X则支持X轴镜像;如果是X和Y,那么是X轴镜像和Y轴镜像都支持;

再通过set_attribute设置其symmetry为Y,这个site支持的legal orientation变为:RO和MY了!

1524

1524

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?