Generated clock

在创建generated clock时,需要指定两个选项,分别是:

1、-mater_clock,用于指定该generated clock的master clock;

2、-source,这个选项用于指定generated clock的waveform的参考点;

原文如下:

Specifies the master clock pin, which is either a master clock source pin or a pin in the fanout of the master clock and driving the generated clock definition pin. The clock waveform at the master pin is used for deriving the generated clock waveform.

这里要注意就是-source这个选项,通常情况下,我们往往会把-source选项中指定位master clock定义的点;但是这不是必须的,我们也可以指定-source为其他pin;

这里需要注意的是,我们一旦通过-source指定的参考点,那么generated clock的waveform就是以这个参考点的waveform作为参考的;

如果是-divide_by 2,那么分频后的波形是以-source中指定的pin去做divide,而不是以master clock的waveform去做divide,特别是master clock pin的waveform和-source中指定的pin的waveform不一致时;

最后产生的波形会发生很大的变化,在做GCA时,会去checkgenerated clock与master clock之间的波形是否与constraint中约束的一致!

怎么定义generated clock?

在定义clock时,是很有技巧的一件事,下面来举个例子说明

这里出现了design中常见的电路,包括分频电路以及mux,那么怎么定义clock是我们最想要的结果呢?

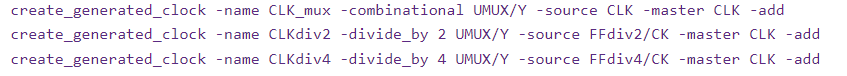

第一种:

1、create_clock -period 10 CLK

2、create_generated_clock -name CLKdiv2 -divide_by 2 UMUX/Y -source FFdiv2/CK -master CLK -add

3、create_generated_clock -name CLKdiv4 -divide_by 4 UMUX/Y -source FFdiv4/CK -master CLK -add

4、set_clock_groups -physically_exclusive -group {CLK} -group {CLKdiv2} -group {CLKdiv4}

这样定义完clock后,会不会有问题呢?当然有,下面一一列举

1、missing clock issue

在mux的输出Y端定义了两个generated clock,由于这是一个新的clock的起始点,除了在这个店上定义的generated clock外,其他clock就无法穿过这个mux的Y pin了,所以CLK无法正确传递到FF1和FF2上;

When a generated clock is created at a pin, all other clocks arriving at that pin are blocked unless they too have generated clock versions created at that pin.

为了在mux的Y端也有CLK通过,我们在mux的Y端定义新的generated clock,如下

1、create_clock -period 10 CLK

2、create_generated_clock -name CLK_mux -combinational UMUX/Y -source CLK -master CLK -add

3、create_generated_clock -name CLKdiv2 -divide_by 2 UMUX/Y -source FFdiv2/CK -master CLK -add

4、create_generated_clock -name CLKdiv4 -divide_by 4 UMUX/Y -source FFdiv4/CK -master CLK -add

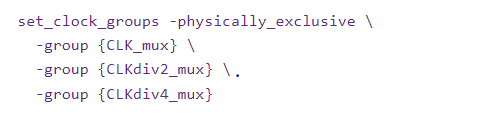

5、set_clock_groups -physically_exclusive -group {CLK_mux} -group {CLKdiv2} -group {CLKdiv4}

我们在mux的Y端定义了3个generated clock,这样CLK也可以传递到FF1和FF2了;

2、The Clock Source Latency Path Issue

在我们report_timing时,在计算clock latency时,也会出现问题,具体的timing report如下

以CLKdiv2这个clock的timing path为例

可以发现,在计算launch path时,clock实际走的是mux的C端,实际路径穿过了FFdiv4,这样得到的launch path delay更大;同时在计算capture path时,走的是mux的A端,这样计算出来的capture path的delay更小;导致这个问题的原因是pt在计算timing时,是尽可能找出最悲观的path;

也就是master clock和generated clock之间的path无法确定为具体的哪一条所导致的;

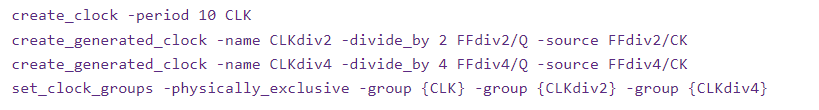

再看generated clock的定义,如下

这里我们虽然通过**-source选项**指定了div clock的source点,分别是FFdiv2/CK和FFdiv4/CK,为什么工具在计算latency时还会选择错误的路径呢?解释如下

The -source option of the create_generated_clock command determines the identity of the master clock, and the sense (non-inverted or inverted) of that master clock. It does not steer the source latency path. Once the master clock’s identity and sense are determined, all possible paths back to that clock’s source are considered for the source latency path.

也就是说-source并不能指定工具如何计算clock latency!

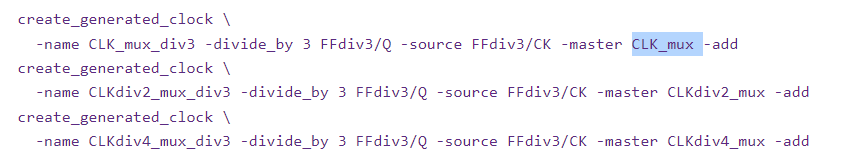

为了解决这个问题,我们需要更改clock的定义方法,我们在FFdiv的Q pin添加generated clock,并将这些clock作为mux/Y端clock的master clock,如下

在创建generated clock时,缺少了-master_clock选项,这里 补充为-master_clock CLK;

这样我们就不在mux的Y端定义clock了,在report timing时,也可以得到正确的timing path;

因为master clock和generated clock之间的path是唯一的了;

3、 MUXs, Physical Exclusivity, and Crosstalk

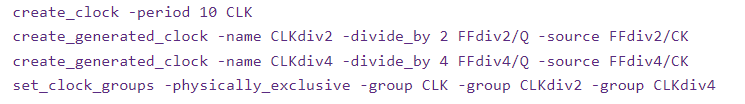

那么按下面的定义就没有问题吗?

我们知道,在mux的Y端,任何时刻只能存在一个clock,所以在mux的Y端的clock应该是physical exclusive的关系;

但是我们在上面设置的是CLK、CLKdiv2、CLKdiv4之间为physical exclusive的关系,可以在mux/Y之前的逻辑,这些clock是同时存在的,而且之间还有crosstalk,如果直接这么设置的话,那么在mux/Y pin之前的crosstalk就被忽略了,所以要调整clock的定义;

对于mux后的电路,任何时刻只能存在一个clock,所以我们可以在mux/A、B、C端定义generated clock,这些generated clock之间的关系是physical exclusive,如下

并设置如下关系

另外,CLK、CLKdiv2以及CLKdiv4之间是有cross talk的,我们只需保持他们的同步关系;

如果这三个clock之间确定没有timing path的话,那么就可以设置这些clock的关系为logical exclusive,这样PT就不会去report这些clock之间的path了,但是在计算crosstalk时,还是会正常计算;

Note that no clock group relationships exist between the clocks upstream of the MUX (CLK, CLKdiv2, and CLKdiv4) because no timing paths exist between these clocks.

If there were additional flip-flops that were clocked off these pre-MUX clocks, then any cross-clock paths would likely be valid.

If they are not valid for functional reasons, an additional logically exclusive relationship would be needed between these pre-MUX clocks.

Others

The correct way to specify the clocks in an SI analysis is to create generated clocks at:

1、any point where the clock waveform is transformed (such as at the divider outputs), PLUS

2、any point where multiple clocks converge and become statically switched, such as at a MUX output

这是solvnet上给出的定义generated clock的两个条件;

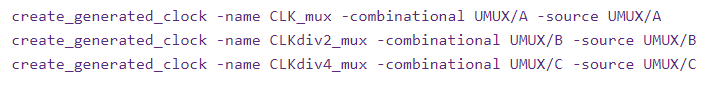

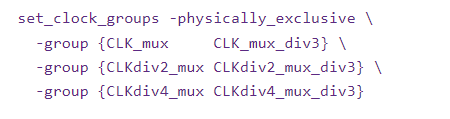

Handling Cascaded Generated Clocks

对于级联的generated clock,应该怎么处理呢?

首先按下面的情况

定义clock如下

这些clock在任意时刻都只能出现一个,所以需要设置下面的关系

完整的clock定义如下

solvnet上的文章如下

https://solvnetplus.synopsys.com/s/article/Specifying-MUXed-Clocks-in-PrimeTime-1576002495523

3566

3566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?