一、ICG消除毛刺原理

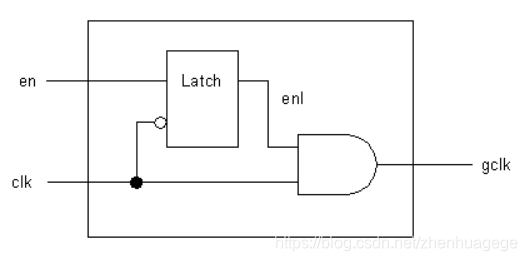

Clock gating cell 可以由与门或者或门构成,但是使用这两者会产生Glitch,因此目前都采用ICG(Integrated clock gating cell),其结构如下

ICG由一个latch(低电平有效)和一个与门(gating cell,也可以是或门)组成。ICG 可以过滤掉en信号中的毛刺信号,其原理如下:

对于毛刺信号Glitch,大概可以分为两种情况:

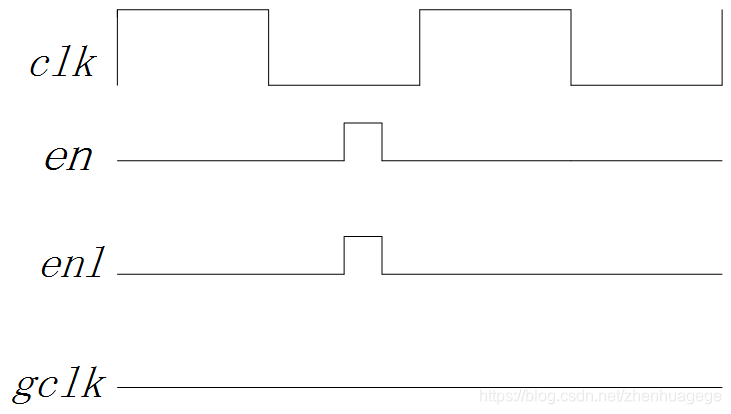

1.en信号中的毛刺出现在clk低电平期间,如下图所示

由上图可以发现,en信号在clk低电平期间产生了毛刺,并且该latch是低电平有效,所以会采集到该毛刺信号,如信号enl中所示,但是由于该ICG的gating cell采用的是与门,此时clk为低电平,即使enl有毛刺信号,也不能通过与门,因此该毛刺信号被过滤。

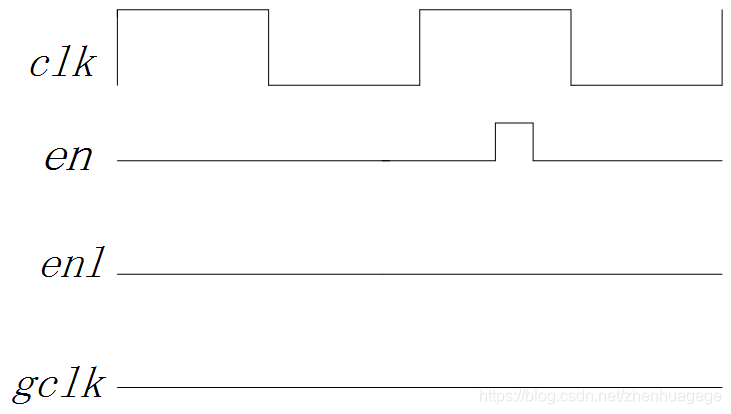

**2.en信号出现在clk高电平期间,如下图所示

由于ICG中的latch是低电平有效,所以在clk高电平期间,latch采集不到en中的毛刺信号,因此该毛刺信号被过滤掉了。

综合以上,可以发现,无论en中的毛刺信号出现在clk低电平或者是高电平期间,ICG可以有效过滤掉en信号中的毛刺,得到好的clk波形!具体的ICG电路及其波形图如下所示

这里也需要注意最重要的一点:

Clock gate不能对clock的信号波形做任何改变,只能对clock做开关处理!

二、Clock-Gating Timing

Gating cell 可以采用与门或者或门,下面分别就两种情况的Timing进行分析!

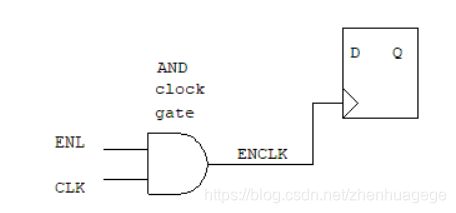

1.AND Gating cell

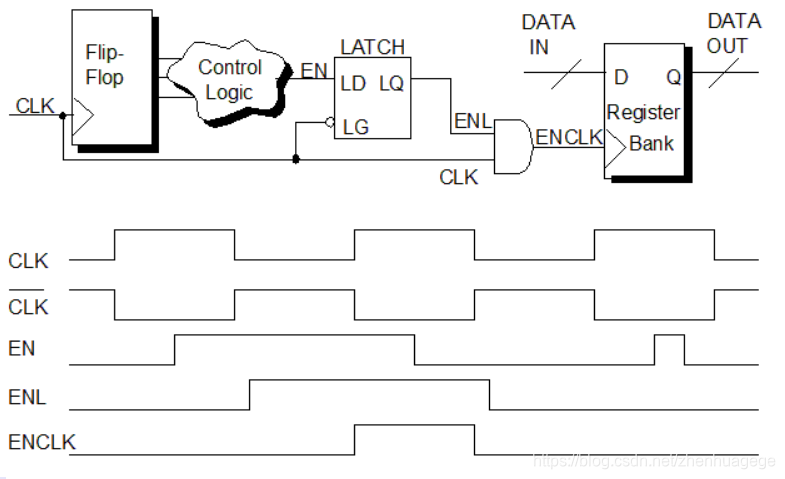

采用与门作为gating cell的结构如下图所示

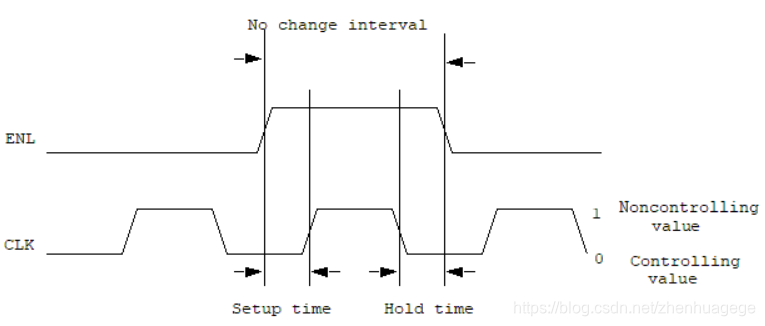

为了保证得到的clock信号是稳定的,必须对gating cell 的input端做setup 和hold check!

首先是对uncontrolling value 和controlling value的解释。

图中CLK 的 uncontrolling value为1,对于一个gating cell,我们的目标是让ENL信号来控制clock的开关, 当CLK为1时,此时该gating cell的输出端 ENCLK 则由ENL控制。ENL为0时ENCLK为0,ENL为1时ENCLK为1;而CLK为0时,由于gating cell是与门,无论ENL信号取高取低,其输出都是0,实际上是由CLK信号控制,与我们最初的让ENL信号控制不一致,所以称为controlling value.

而setup check指的是ENL信号要在clock信号变为uncontrolling value前一段时间就保持稳定值不变,hold check指的则是让ENL信号在CLK信号变回controlling value后仍要保持一段时间稳定值不变!

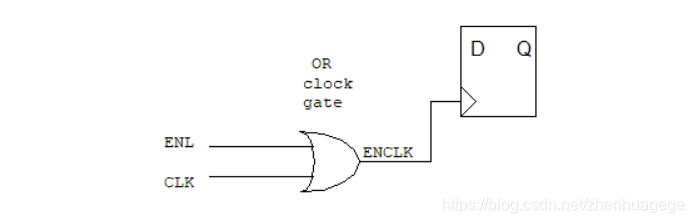

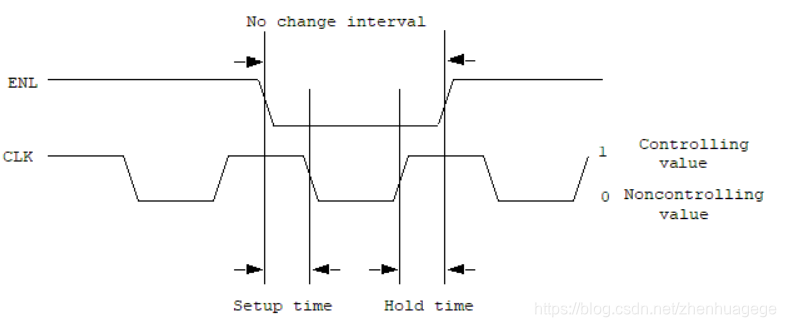

或门的情况类似,就是CLK的uncontrolling value和controlling value与与门相反,如下图所示,不再做过多解释!

3094

3094

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?