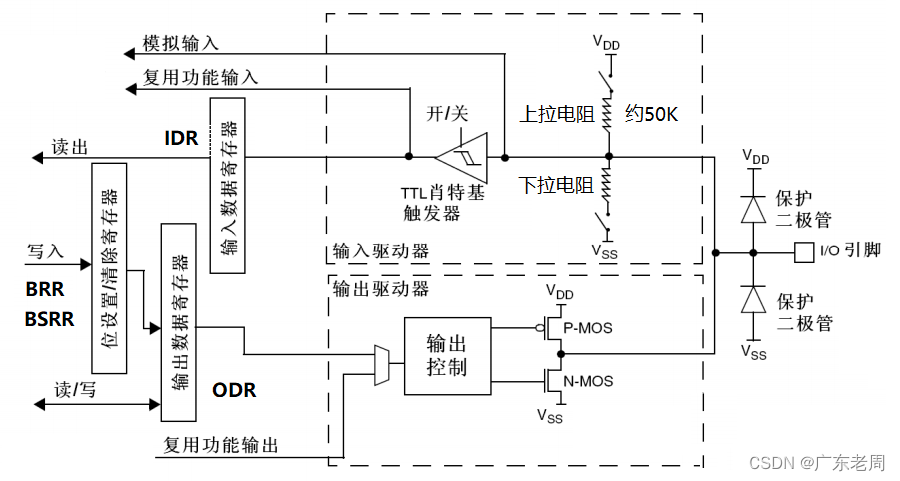

输入重点:

- 配置为输入状态后,mos管被禁用,BRR、BSRR、ODR寄存器的值均无效;

- 模拟输入:输入范围0~3.3V;

- 浮空输入:上、下拉电阻关闭,引脚悬空时电平不确定;

- 上拉输入:上拉电阻打开, 引脚悬空时输入端保持高电平;

- 下拉输入:下拉电阻打开, 引脚悬空时输入端保持低电平;

输出重点:

- 配置为输出状态后,上、下拉电阻虽被禁用,但肖特基触发器有效,IDR有效!

- BRR、BSRR、ODR,控制mos管的栅极电平,栅极,栅极,栅极;

一、配置时,寄存器参数与标准库的对照关系

1: 寄存器中, 输入模式有3种, 输出模式有4种, 如下图:

2: 标准库中, 输入模式4种, 输出模式4种:

3: 小结:

为了使用方便, 标准库把寄存器上的3种输入模式, 封装成4种输入模式了, 但本质上是一样的.

二. 使用标准库配置时---8种模式细解

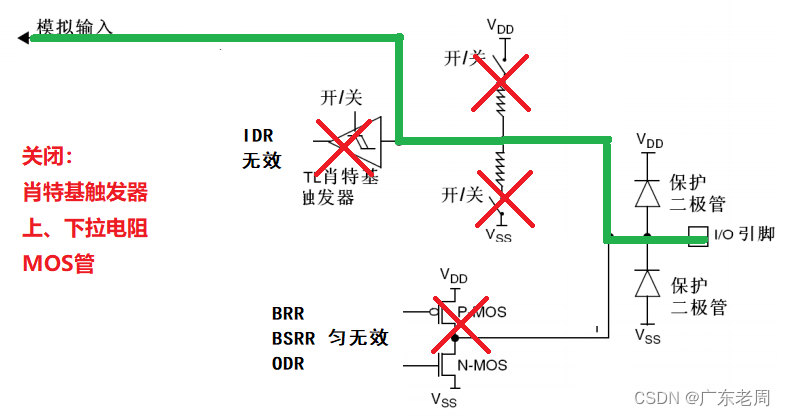

1:模拟输入 GPIO_Mode_AIN

- 路线: 1-信号从引脚进入, 2-直接进入片上外设ADC中;

- IDR: 断开无效,常为0,无法读取准确引脚电平状态;

- BRR、BSRR、ODR:无效,因为mos管被禁用;

- 重点: 引脚模拟电压输入范围:0~3.3V;

2:浮空输入 GPIO_Mode_IN_FLOATING

- 路线: 信号从引脚进入;经施密特触发器转换为0、1;存入输入数据寄存器随时可读取;

- IDR: 可用, 读取数据(经施密特;

- ODR:无效,上下拉电阻无法影响电平状态;

- 理解: 电平由外部电路决定;当引脚悬空时,IDR读取的电平状态是不确定的。

3:下拉输入 GPIO_Mode_IPD

- 路线: 1-信号从引脚进入; 2-被下拉电阻钳位; 3-施密特触发器转换为0、1; 4-存至输入数据寄存器随时读取;

- IDR: 可用, 可实时读取引脚真实电平;

- ODR:置1,开启弱上拉,引脚悬空时, IDR为1; 非悬空时, 由外部电路决定;

- ODR:置0,开启弱下拉,引脚悬空时, IDR为0; 非悬空时, 由外部电路决定;

- 理解: 相当于浮空输入外加下拉电阻, 省了外部下拉

4: 上拉输入 GPIO_Mode_IPU

- 路线:1-信号从引脚进入; 2-被下拉电阻钳位; 3-施密特触发器转换为0、1; 4-存至输入数据寄存器随时读取;

- IDR: 有效, 可实时读取引脚电平(外部电平);

- ODR: 置1,开启弱上拉,引脚悬空时, IDR为1; 非悬空时, 由外部电路决定;

- ODR:置0,开启弱下拉,引脚悬空时, IDR为0; 非悬空时, 由外部电路决定;

- 理解: 相当于浮空输入外加上拉电阻, 省了外部上拉

5:开漏输出 GPIO_Mode_Out_OD

- 路线:1-输出控制信号; 2-控制MOS管开合; 3-最终信号输出;

- IDR: 可实时读取引脚电平(外部电平);ODR

- ODR:置0,N-MOS 导通,P-MOS 不被激活, 引脚钳死至低电平,并使外部整个开漏线路均为0;

- ODR:置1,N-MOS 高阻,P-MOS 不被激活,此时引脚电平完全由外部电路决定;不能开启弱上拉(重要),

- 理解: 引脚为悬空时,ODR-置1,并不能使引脚置1, IDR亦为0;

- 理解: 此模式可以把端口作为双向IO使用。

6:推挽输出 GPIO_Mode_Out_PP

- 路线: 1-输出控制信号; 2-控制MOS管开合; 3-最终信号输出;

- IDR: 可实时读取引脚电平(外部电平);

- ODR:置0,开启弱下拉,引脚悬空时, IDR为0; 引脚非悬空时, 由外部电路决定;

- ODR:置1,开启弱上拉,引脚悬空时, IDR为1; 引脚非悬空时, 由外部电路决定;

7:复用开漏输出 GPIO_Mode_AF_OD

- 路线: 1-由复用功能输出信号; 2-控制MOS管开合; 3-最终信号输出;

- IDR: 可实时读取引脚电平(外部电平);

- ODR:无效;引脚悬空时,ODR置0、1, 都不能改变引脚电平;

8:复用推挽输出 GPIO_Mode_AF_PP

- 路线: 1-由复用功能输出信号; 2-控制MOS管开合; 3-最终信号输出;

- IDR: 可实时读取引脚电平(外部电平);

- ODR:断开;引脚悬空时,ODR置0、1, 都不能改变引脚电平;

三、引脚的工作电流

1:输出模式

单引脚最大电流:< 25mA

所有引脚总电流:< 150mA

2:输入模式

单引脚最大电流:< ±5mA

所有引脚总电流:< ±25mA

3:数据手册原描述

1470

1470

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?