AXI 总线协议根据不同的场景,又更加的细分为了三种类型:

AXI

AXI-Lite

AXI-Stream (也叫AXIS)

完整的 AXI 总线协议涉及的内容较多,适合高速内部互联(通过 AXI Interconnet),独立的读写数据总线和独立的读写地址总线,加上 burst based 传输,使得其吞吐可以达到很高水准;之所以将 AXI 总线协议标准分为了 3 类,主要是为了针对不同的场景;

AXI4:完整AXI4传输总线适合高速内部互联,结构复杂,消耗的资源多;

AXI4-Lite:精简版的 AXI4 协议,是一个简单地吞吐量地址映射性通信总线,目的是为了与控制寄存器风格的接口组件进行通信并允许建立简单的组件接口,可以理解为,可以接低速外设的总线;

AXI4-Stream:跟 AXI4 的相比去除了地址线,只有简单的发送与接收和发送;

AXI 总线协议参考:AMBA 系列之 AXI 总线协议初探

AXI4-Lite 的接口的主要特点是:

- 1) 所有传输都是猝发长度为1

- 2)所有数据访问宽度和数据总线的宽度大小相同

- 3)支持数据总线宽度为32字节或64字节

AXI4 总线和 AXI4-Lite 总线具有相同的组成部分:

- 1)读地址通道,包含 ARVALID, ARADDR, ARREADY信号;

- 2)读数据通道,包含 RVALID, RDATA, RREADY, RRESP信号;

- 3)写地址通道,包含 AWVALID,AWADDR, AWREADY信号;

- 4)写数据通道,包含 WVALID, WDATA,WSTRB, WREADY信号;

- 5)写应答通道,包含 BVALID, BRESP, BREADY信号;

- 6)系统通道 ,包含 ACLK,ARESETN信号。

AXI4 总线和 AXI4-Lite 总线的信号也有他的命名特点:

- 1)读地址信号都是以AR开头(A:address;R:read)

- 2)写地址信号都是以AW开头(A:address;W:write)

- 3)读数据信号都是以R开头(R:read)

- 4)写数据信号都是以W开头(W:write)

- 5)应答型号都是以B开头(B:back(answer back))

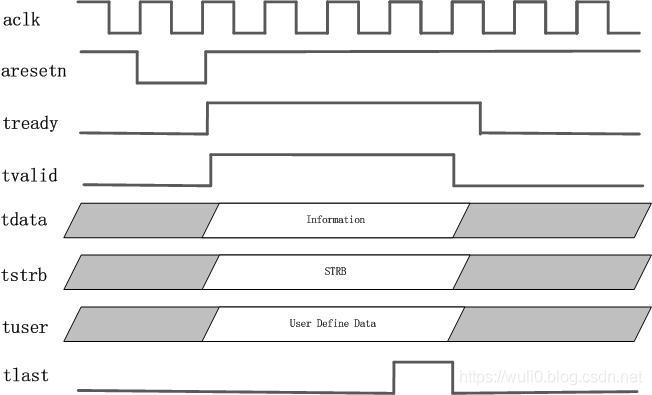

AXI4-Stream 总线的组成有:

- 1)ACLK信号:总线时钟,上升沿有效;

- 2)ARESETN信号:总线复位,低电平有效;

- 3)TREADY信号:从机告诉主机做好传输准备;

- 4)TDATA信号:数据,可选宽度 32,64,128,256bit;

- 5)TSTRB信号:每一bit对应TDATA的一个有效字节,宽度为 TDATA/8;

- 6)TLAST信号:主机告诉从机该次传输为突发传输的结尾;

- 7)TVALID信号:主机告诉从机数据本次传输有效;

- 8)TUSER信号 :用户定义信号,宽度为128bit;

对于 AXI4-Stream 总线命名而言,除了总线时钟和总线复位,其他的信号线都是以T字母开头,后面跟上一个有意义的单词

AXI 和 AXI-Lite 可以通过 Inerconnect IP 进行互联;

https://www.xilinx.com/support/documentation/ip_documentation/ug761_axi_reference_guide.pdf

本文深入探讨了AXI总线协议的三种类型:AXI、AXI-Lite和AXI-Stream,详细解析了它们的特点及应用场景。AXI适用于高速内部互联,AXI-Lite用于低速外设通信,而AXI-Stream则简化了数据传输过程。

本文深入探讨了AXI总线协议的三种类型:AXI、AXI-Lite和AXI-Stream,详细解析了它们的特点及应用场景。AXI适用于高速内部互联,AXI-Lite用于低速外设通信,而AXI-Stream则简化了数据传输过程。

6591

6591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?