一、故事前传

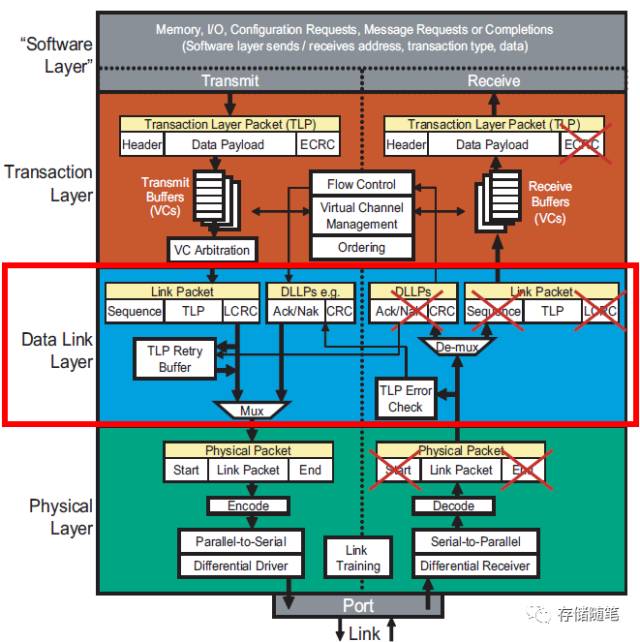

之前我们讲了对PCIe的一些基础概念作了一个宏观的介绍,了解了PCIe是一种封装分层协议(packet-based layered protocol),主要包括事务层(Transaction layer), 数据链路层(Data link layer)和物理层(Physical layer)。

较为详细解释请见之前的文章:

1. PCIe技术概述;

2.0~2.8 PCIe Transaction layer事务层详细解析;

二、数据链路层概述

之前的文章中,我们提到"在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。"

从上图中,我们也可以明显的看到,Data Link Layer在PCIe总线中处于承上启下的作用,保证来自事务层的TLPs在PCIe总线中正常的传递。

在发送端,当Transaction Layer事务层的TLPs传进来时,Data Link Layer会在TLP前后两端分别加上Sequence以及LCRC部分。

在接收端,数据链路层接收到TLP报文之后进行拆解,剥离Sequence和LCRC部分,再传送至事务层。

此外,数据链路层使用了Retry与监控机制(Ack/Nak)来保证数据传输的一致性和完整性。

来自事务层的TLPs,再加上前缀Sequence和后缀LCRC之后,会首先暂存在数据链路层的TLP Retry Buffer,然后再发送至接收端。发送端会根据接收端传到的Ack/Nak DLLP决定是否需要重新发送TLP。如果不需要重新发送,则将其从TLP Retry Buffer里清除。

注意: DLLP不同于TLP,是产生与数据链路层,中止与数据链路层。DLLP并不是有TLP加上Sequence和LCRC组成的,具有单独的格式。

后续会对数据链路层的DLLP结构以及Ack/Nak进行详细的介绍,敬请期待!谢谢!

6593

6593

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?