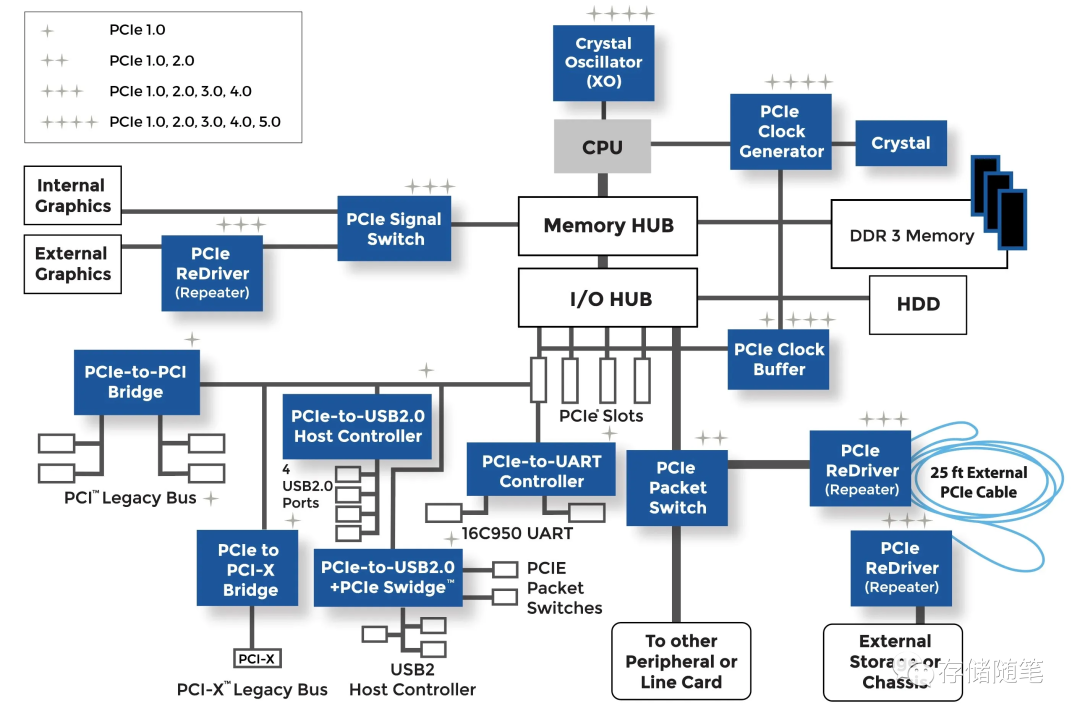

在PCIe系统中,多个设备通过PCIe链路连接在一起,形成一个复杂的互连网络。这些设备可能包括CPU、GPU、网卡、存储控制器等。由于PCIe是一种高速、低延迟的总线标准,任何设备故障或错误都可能迅速传播到整个系统,导致数据损坏、系统崩溃等问题。

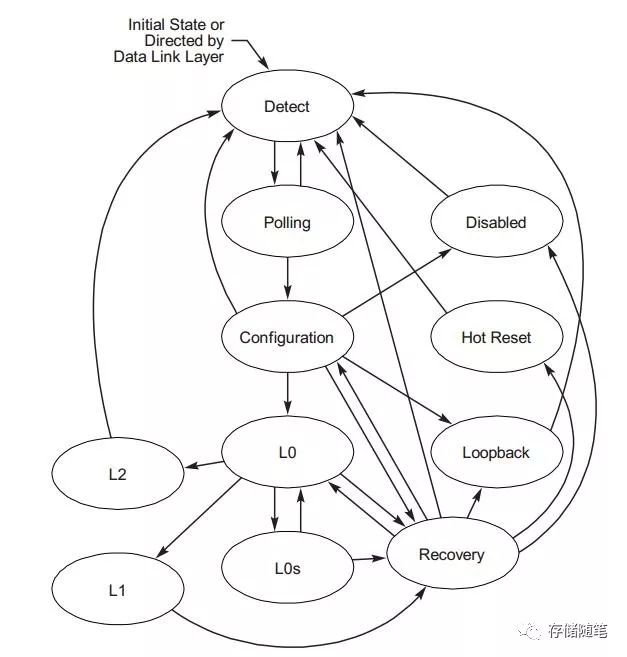

为了应对这种风险,PCIe协议引入了多种错误检测和报告机制,如Advanced Error Reporting (AER)和Link Training and Status State Machine (LTSSM)等。然而,这些机制主要集中在单个设备或链路上的错误处理,对于跨多个设备或端口的错误传播控制相对较弱。

扩展阅读:浅析PCIe链路LTSSM状态机

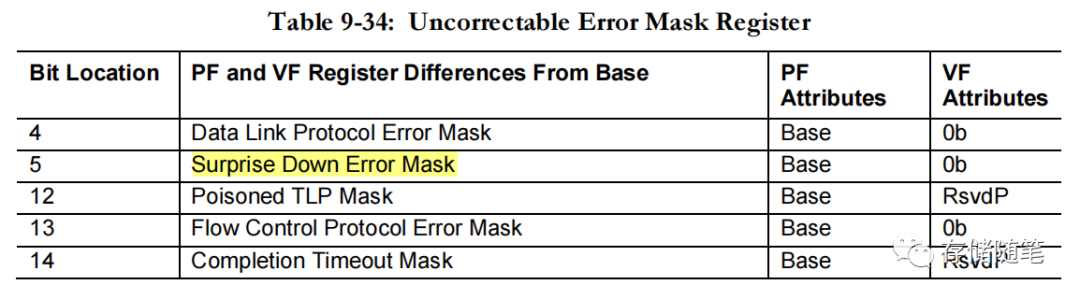

PCIe Surprise Down和DPC(Downstream Port Containment)是PCIe协议中两个相关的错误处理机制,它们在系统中相互配合以提高系统的稳定性和数据完整性。

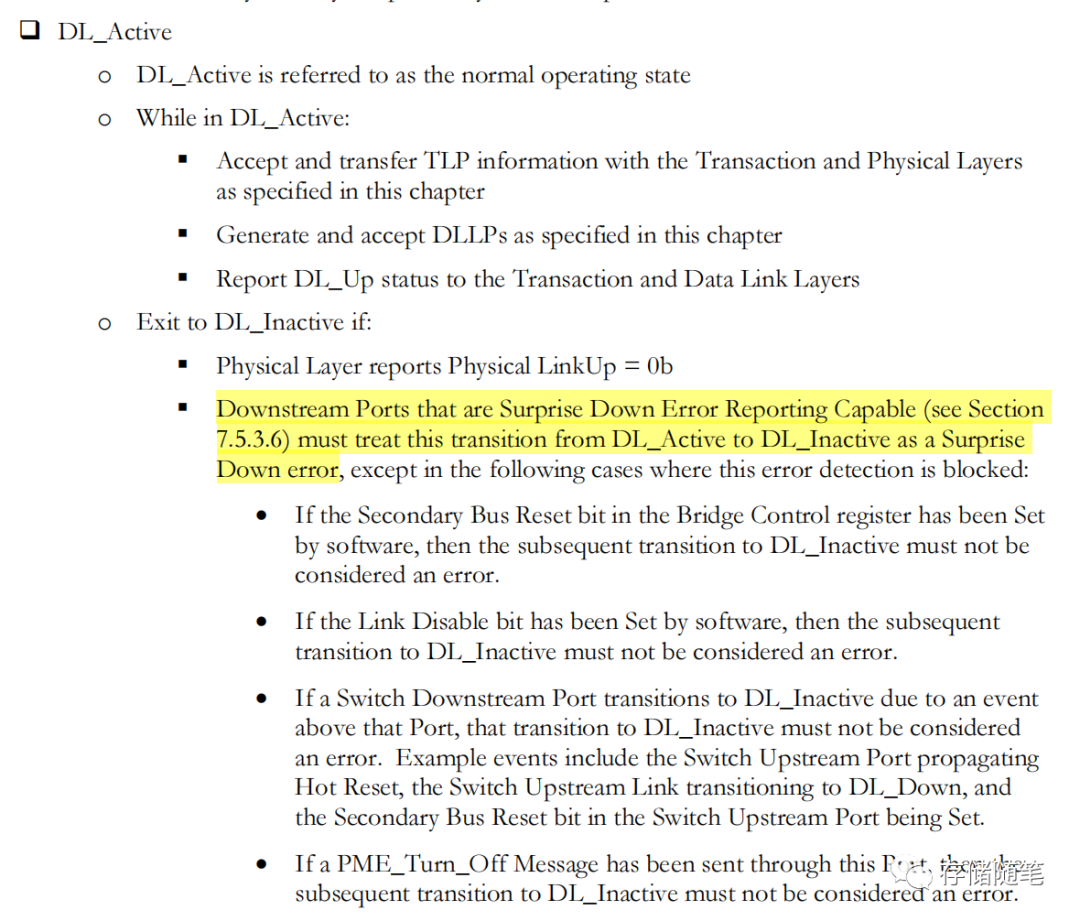

PCIe Surprise Down是指PCIe设备在操作系统不知情的情况下突然停止响应或被移除的情况。这可能是由于硬件故障、电源问题、热插拔事件或其他不可预见的原因引起的。当发生Surprise Down时,设备可能会立即停止通信,导致正在进行的事务中断,并可能引发各种错误条件。

-

-

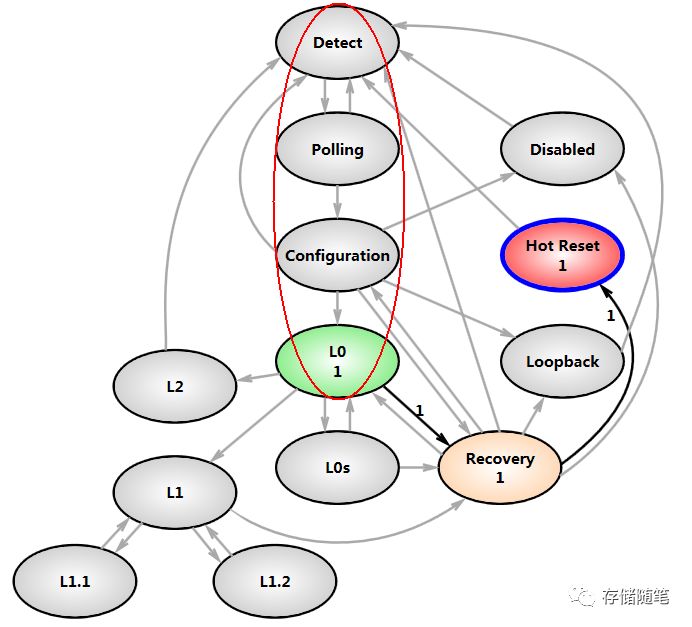

当PCIe设备发生故障、电源问题或热插拔事件导致"Surprise Down"时,硬件会触发一个异常。

-

在"Surprise Down"情况下,LTSSM的状态可能从正常操作状态(如"L0"或"L0s")转换到错误状态,如"Hot Reset"、"Electrical Idle"或"Link Down"状态。

-

PCIe控制器(通常集成在CPU或主板上)检测到异常后,更新其内部的状态寄存器以反映设备的状态变化。

-

-

-

PCIe驱动调用相应的错误处理函数,如

pci_error_detected()或自定义的错误处理函数。 -

在这些函数中,驱动可能尝试恢复设备、禁用设备或标记设备为失效状态。

-

错误信息通过调用

dev_err()、printk()等函数被记录到内核日志(dmesg)中。

-

文章探讨了PCIe系统中设备间高速互连的风险,重点介绍了PCIeSurpriseDown和DPC错误处理机制如何在单个设备故障时防止错误传播,以及它们在保持系统稳定性和数据完整性的角色。

文章探讨了PCIe系统中设备间高速互连的风险,重点介绍了PCIeSurpriseDown和DPC错误处理机制如何在单个设备故障时防止错误传播,以及它们在保持系统稳定性和数据完整性的角色。

1099

1099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?