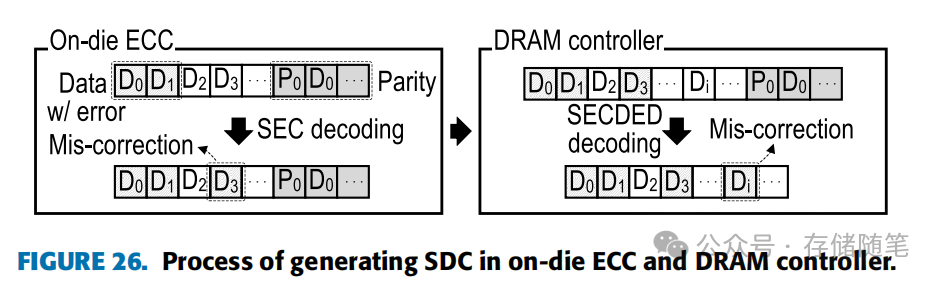

在最近的研究观察到的比特错误率表明,在集成了片上(136,128)SEC和系统SECDED(72,64)的单DRAM芯片系统中,大约每30万个SECDED解码周期会发生一次静默数据损坏(SDC)。SDC发生时,两个数据比特同时被损坏但被当作单个错误处理。

图26描绘了SDC在片上ECC和DRAM控制器中产生的过程,当D0和D1被错误地识别为单个错误数据,且在片上ECC中D3被错误修正时,DRAM控制器也会误解并错误修改了第i个数据Di,从而导致SDC。

高带宽内存(HBM2E)如图27所示,同时在片上ECC和系统ECC中应用了SECDED。图27(a)中,系统ECC1无法解决的双重错误可以通过OD-ECC1,2防止。但是,如果两个错误都位于OD-ECC 0区域内,且这些错误又落入了System ECC1区域,如图27(b)所示,则会被视为UE。HBM3中的SSCDSD技术可以缓解这一问题,但与SECDED类似,当遇到双重符号错误时,无论是在系统ECC还是片上ECC都无法进行纠正。

因此,研究重点应放在如何通过现有ECC技术或在片上ECC中应用先进技术来最小化UE。虽然使用SECDED的片上ECC在延迟方面较SSCDSD有优势,但在多比特错误纠正方面可能存在劣势。结合适合多错误纠正的ECC技术和恰当的ECS技术,可以显著增强内存系统的RAS,强调了未来内存技术发展中相关研究的重要性。未来的趋势可能是探索如何将不同ECC技术有效结合,以平衡延迟、纠错能力和成本,从而达到最优的系统性能和可靠性。

内存RAS技术的发展对于提升数据中心的稳定性和经济性至关重要。随着硬件架构的不断演进和工作负载的多样化,先进的ECC、创新的CRC应用以及片上ECC技术的应用,为降低内存错误带来的风险提供了更多可能性。未来,随着技术的持续进步,我们期待看到更加高效、智能的内存错误管理方案,进一步减少数据中心的停机时间和维护成本,支撑大数据和云计算时代的数据密集型应用。

完整分析解读参考:数据中心内存RAS技术全景剖析

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?