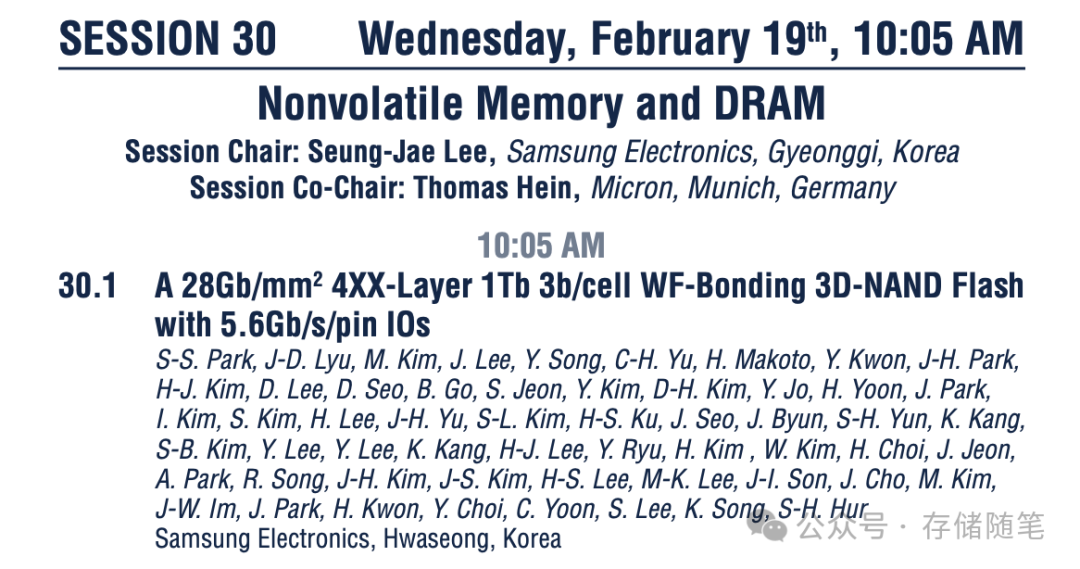

近期,2025年IEEE国际固态电路会议(ISSCC)的日程中透露出,三星正在研发400L第十代V-NAND技术,并将在ISSCC会议上发布。据有关消息分析,该NAND也将采用WF-Bonding键合技术,从第九代的286层提升到了超过400层,实现了28 Gb/mm²的存储密度。

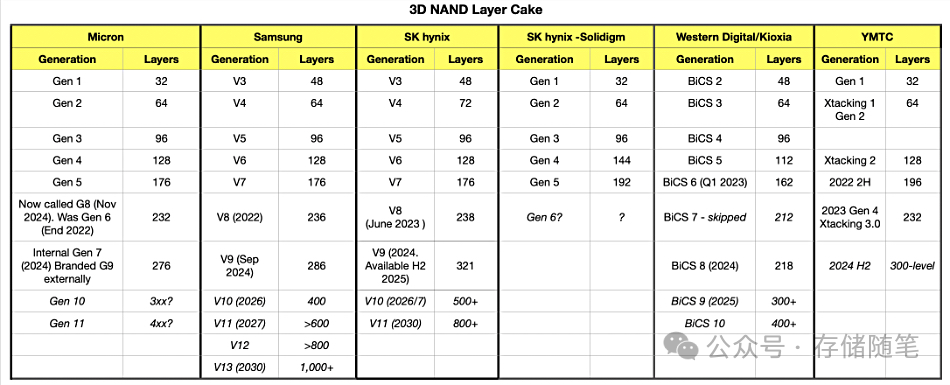

当前量产中 NAND 层数最高的是 SK 海力士,达到 321 层;其次是三星的 286 层;美光为 276 层;西部数据和铠侠的 BiCS 工艺有 218 层,且正在研发 300 多层的 BiCS 9 代技术;SK 海力士旗下的 Solidigm 子公司目前采用 192 层的 QLC 技术,相对而言在层数方面处于较落后状态,不过其刚宣布了使用该 3D NAND 的大容量 122TB SSD。

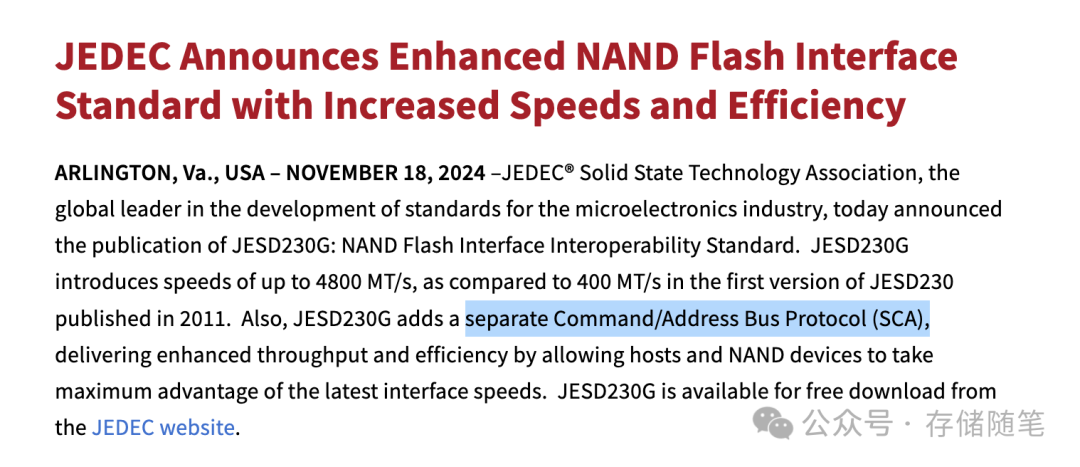

固态技术协会JEDEC新发布了JESD230G规范,预计NAND厂商会在下一代NAND(300L以上),支持新的NAND接口特性SCA。

NAND接口从ONFI 1.0版本到ONFI 5.1版本,接口速度有了快速提升,但命令、地址和数据的传输形式基本保持不变。随着总线传输速度的增加,主要改进在于减少了数据传输的延迟,然而命令和地址的传输延迟并未得到改善。

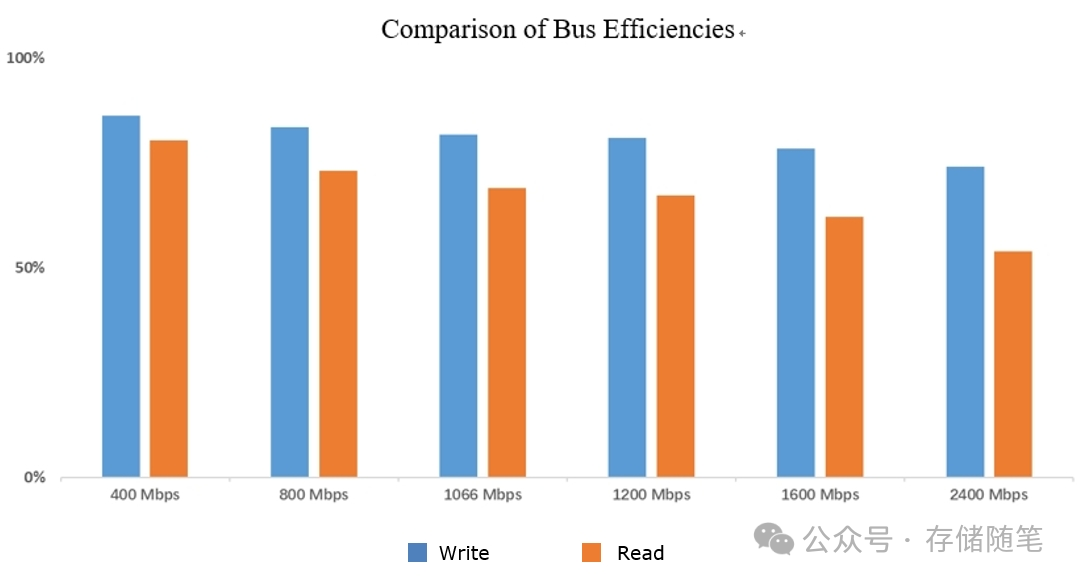

在系统层面,随着总线速度提高,由于命令和地址传输效率未见显著提升,导致整个总线使用效率逐渐下降。如上图,在理想写入/读取场景下总线效率的对比情况,可以看出无论是读取还是写入场景,总线效率都在逐步下滑,特别是在读取场景下,当总线效率降至约50%时,这无疑给系统设计带来了更大的挑战。

尽管NAND闪存接口速度不断提升,但由于命令和地址传输机制的局限性,实际应用中总线资源的利用率并未随速度提升而同步增长,反而出现了效率降低的问题,这对未来系统优化设计提出了新的难题。

当前,面对这一挑战,除了继续提高接口速度外,还将优化命令和地址的传输模式(这也是SCA解决的事情),这无疑将给主控芯片的设计带来新的考验。

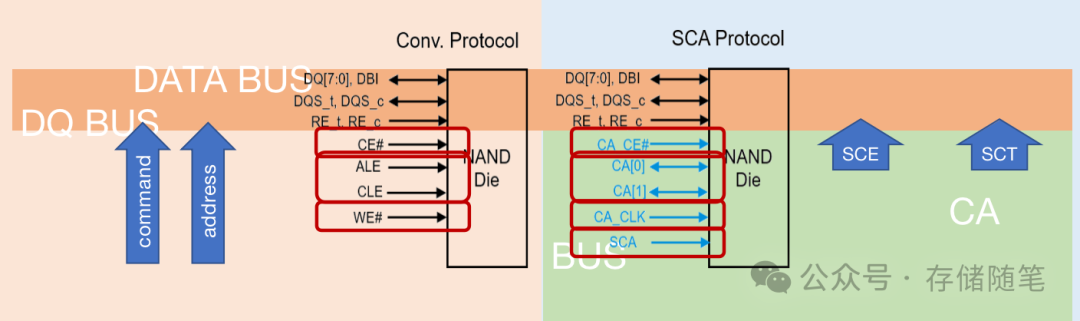

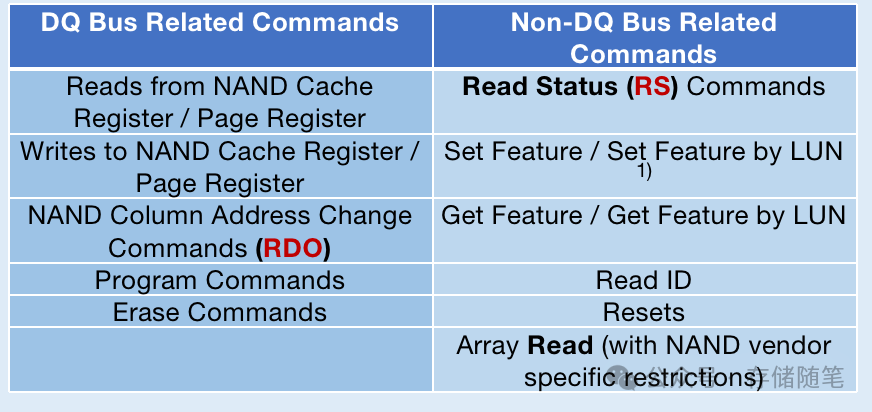

在传统接口中,CE#是NAND闪存的一个关键引脚,用来激活或选择特定的NAND闪存芯片,以便控制器与其进行通信。包括ALE/CLE/WE#等信号。

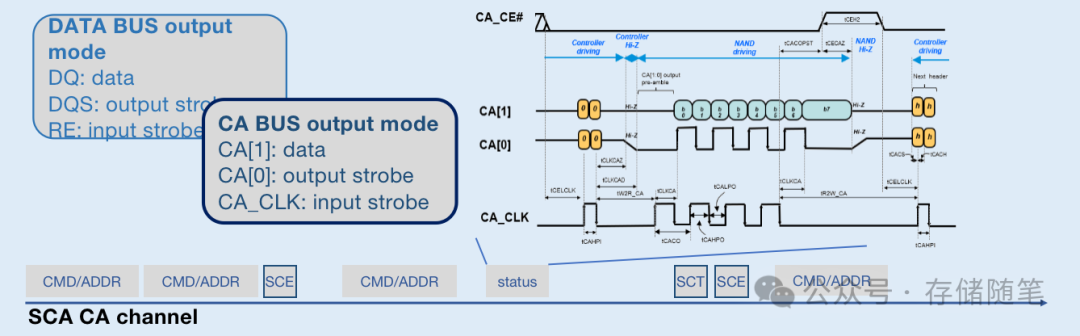

然而,在Separate Command Address (SCA) 接口中,设计思路发生了根本性的变化。SCA接口将命令和地址信号与数据传输分离开来,增加了专门的CA(Command and Address)通道,而不是像传统接口那样混用I/O线传输命令、地址和数据。

传统接口中的CE#和其他引脚主要是用来完成基本的芯片选择、读写操作以及数据和命令地址的并行传输,而SCA引入的CA引脚则是专为串行化命令和地址信息设计,以此实现更高效、灵活的多任务处理能力。

-

CA pins:这些引脚专用于传输命令和地址信息,采用并行转串行的方式,降低了所需的物理引脚数目,同时提高了信号完整性,并允许在数据传输的过程中并发执行命令和地址更改。

-

CA_CLK:用于驱动CA通道的串行数据时钟。

-

CA[1:0] :用于在CA通道上传输串行化的命令和地址数据。

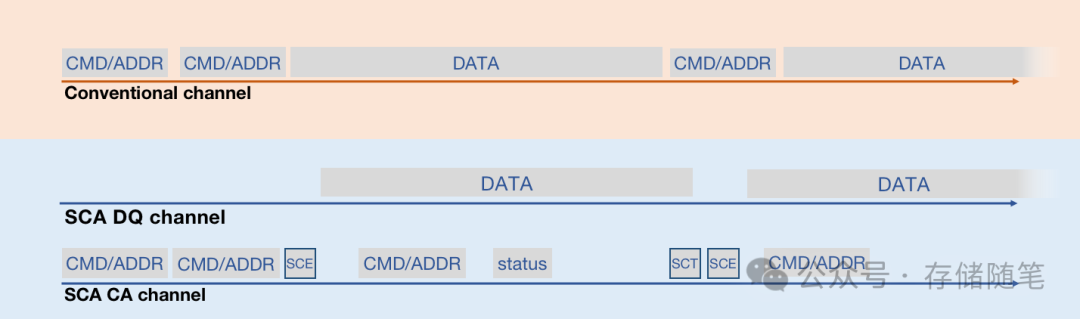

它的主要原理在于将传统的命令和地址(CMD/ADD R)信号与数据传输(DATA/DQ)信号分离到不同的通道上,即创建了专门的SCA CA通道用于命令和地址的串行传输,而DQ通道专注于数据的并行传输。

通过这种方式,SCA接口不仅简化了布线和电路设计,还优化了控制器与NAND闪存之间的交互,允许更高级别的命令交错执行,从而显著提升固态硬盘(SSD)的并行操作能力和整体性能。

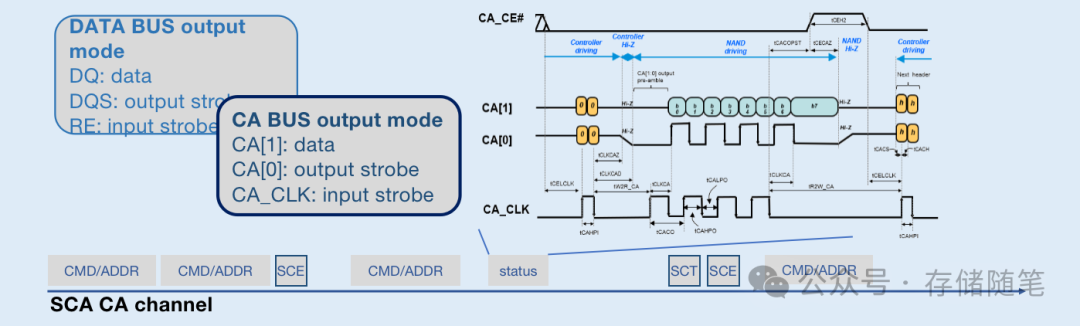

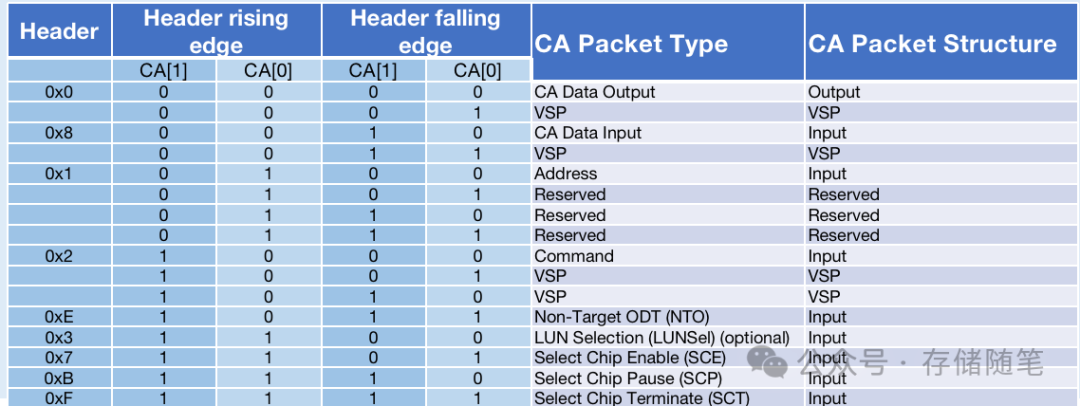

CA output packet和CA input packet是Separate Command Address (SCA) NAND接口协议中用于命令和地址传输的关键数据结构。

-

CA Input Packet:

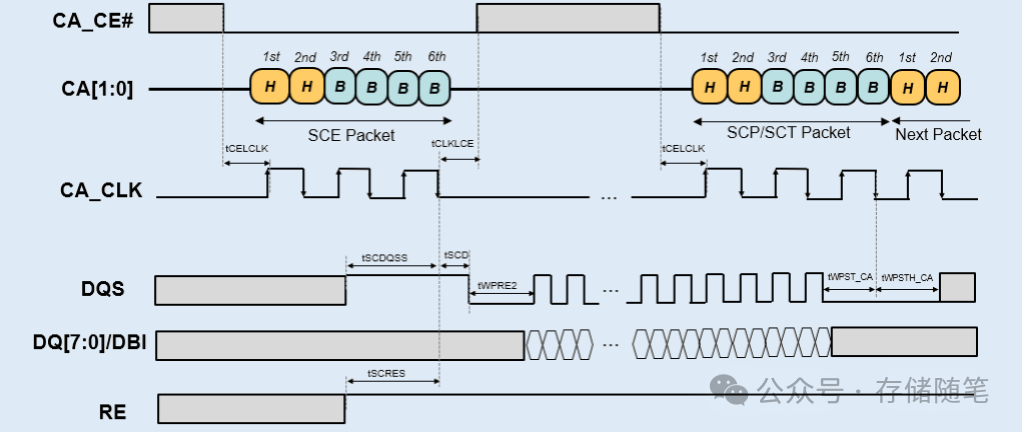

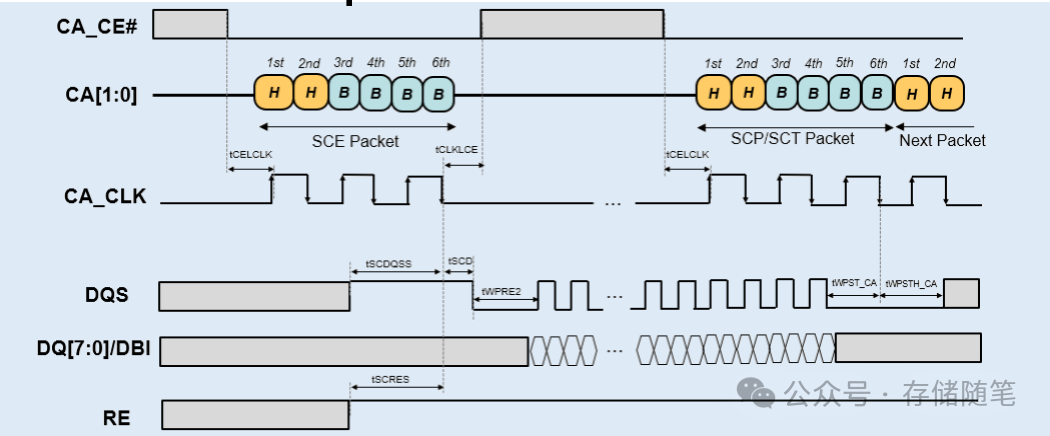

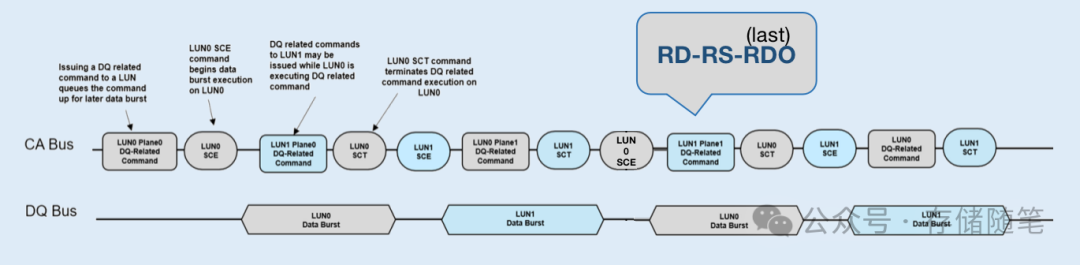

在SCA接口中,输入到NAND器件的命令和地址信息被组织成并行至串行转换的CA(Command and Address)输入包。这些包通常包含具体的命令类型、地址以及其他控制信号,比如LUN选择(LUNSel)、选中芯片启用(SCE,Select Chip Enable)、选中芯片终止(SCT,Select Chip Terminate)等。通过这种设计,控制器可以将原本在传统接口中并行传输的命令和地址以更高效、更低干扰的方式序列化后发送给NAND闪存设备,从而提高整个系统的性能和稳定性。

-

CA Output Packet:

CA输出包则是从NAND器件返回到控制器的数据形式,它主要承载了NAND器件对控制器发出命令的响应以及可能需要的数据输出。在SCA接口下,CA总线上的输出模式包括数据位(如CA[1:0])以及一个输出时钟信号(CA_CLK),其中数据位上携带的是状态信息或其他与操作相关的反馈内容。同样采用串行方式输出,CA输出包能够更好地配合DQ总线进行读写操作,并支持多字节连续输出,从而使得数据流更加顺畅且充分利用通道带宽。

CA input packet 和 CA output packet 作为SCA接口的核心组成部分,分别负责向NAND器件发送指令和地址请求及接收来自NAND器件的操作回应,它们通过分离命令与数据路径来实现并发处理,提升了固态硬盘(SSD)的I/O性能和系统效率。

在采用Separate Command Address (SCA) 接口的存储产品中,DQ input burst和DQ output burst又是什么样的策略呢?

-

DQ Input Burst:

在读取操作期间,数据以一种快速并行的方式通过DQ总线传送到控制器。在SCA接口下,虽然命令和地址信息与数据传输分离,但当命令执行后,相应的数据会被一次性或分段式地通过DQ通道传输到控制器,以便于高效利用带宽资源,并减少数据读取延迟。

-

DQ Output Burst:

在写入操作时,控制器将要写入的数据块以高速连续的方式通过DQ总线发送给NAND闪存芯片。这个过程同样要求在短时间内完成大量的数据传输,确保高效率地填充目标页或区块。在SCA架构中,尽管CA总线负责命令和地址交互,但数据的实际写入动作仍然依赖于DQ总线输出能力,使得数据能够在指定的存储单元上被迅速且准确地更新。

SCA接口的一大优势在于它可以实现命令交错(command interleaving),使得在DQ总线忙于数据传输的同时,可以通过CA总线发送非数据相关的命令,例如读取状态(Read Status, RS)、读取ID(Read ID)、设置功能(Set Feature)等。这样就提高了闪存操作的并发性和整体效率。

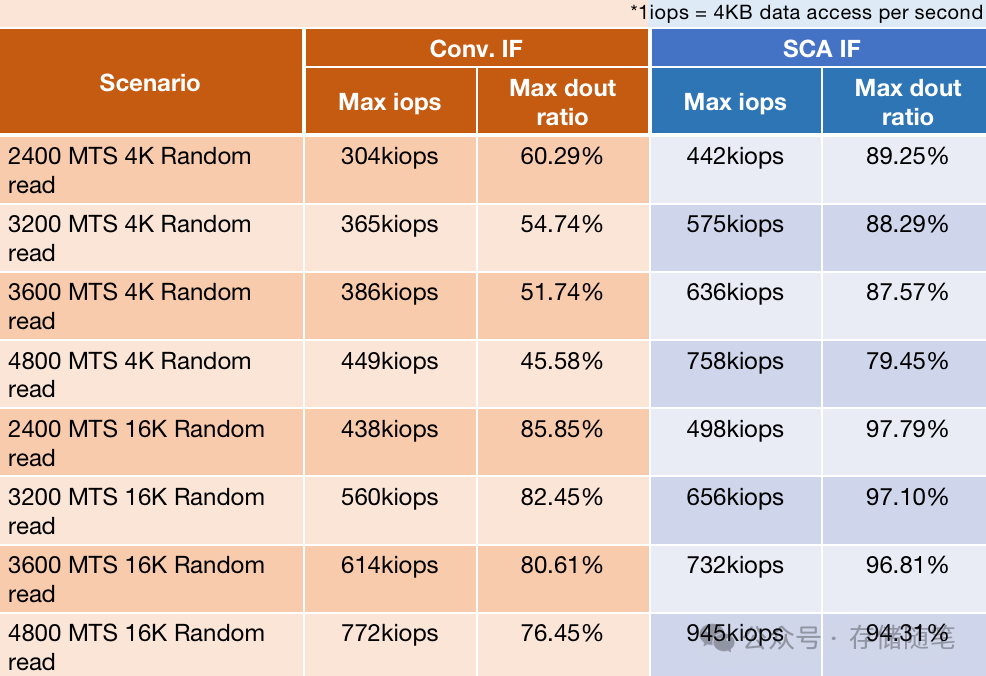

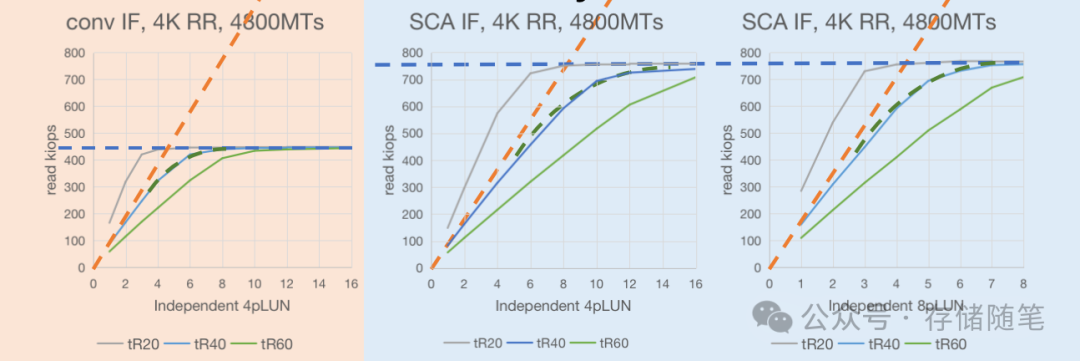

在多逻辑单元(Multi-LUN)的场景下,SCA接口尤其有助于提高随机读取性能。通过合理安排读取命令和等待时间(如tR),SCA接口可以在一个LUN完成读取后立即开始另一个LUN的读取操作,而无需等待整个DQ总线空闲,从而减少了延迟和提高了IOPS。并且在实际测试案例中,与传统接口相比,SCA接口在不同速率下的4KB和16KB随机读取性能都有显著提升,表现为更高的最大IOPS和数据输出比率(dout ratio)。

此外,SCA接口还有助于缓解闪存通道饱和问题。对于多层结构的NAND闪存,SCA接口能更好地调度和协调各平面的操作,从而在8个独立LUN或者更多的情况下确保高效并行访问,进而提升整体系统的带宽利用率和性能表现。

综上所述,SCA接口通过分离命令和地址与数据传输,不仅简化了接口设计,降低了物理引脚的需求,还增强了多任务处理能力,改善了闪存操作的并发性,显著提高了SSD的性能指标,尤其对于高负载、高并发随机访问的应用场景而言具有显著的优势。

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

959

959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?