文章目录

1.说明

该文参考链接:

参考原文1

这里对这篇文章做下笔记,以及加上一些自己的理解;如有需要,可联系删除;

2.简介

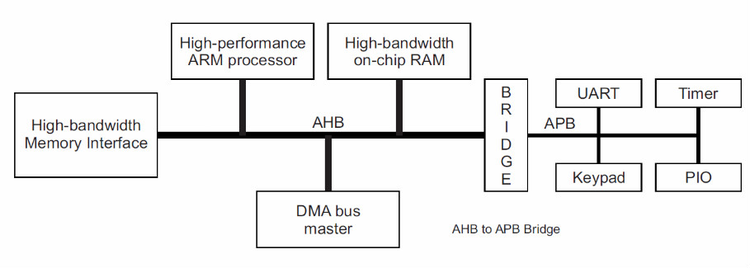

AHB总线规范是AMBA总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。

3. SOC中的AHB

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。

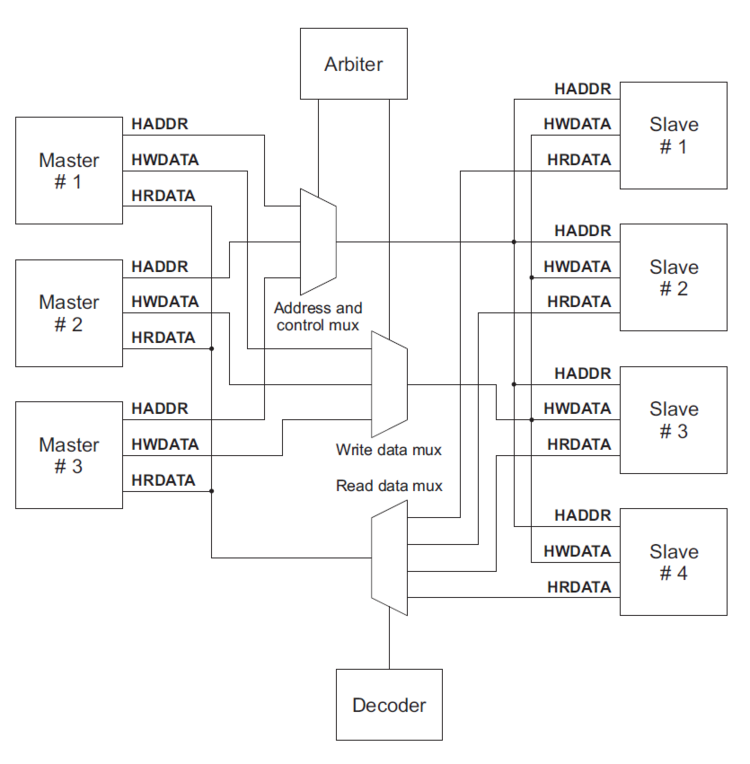

4.完整的AHB架构

- 只允许一个master进行总线占用;

- arbiter需要正确的仲裁master请求,送给相应的slave,有关仲裁的知识可以看我下面的这篇文章哦;

仲裁那些事 - decoder接受slave送回的读数据以及其它信号,正确的送回给相应的master;

5.AHB接口信号列表

| 接口名 | 方向 | 描述 |

|---|---|---|

| hclk | systerm | 系统时钟 |

| hresetn | systerm | 系统复位 |

| haddr[31:0] | master->slave | 读写地址 |

| htrans[1:0] | m->s | 传输类型NONSEQ/SEQ/IDLE/BUSY |

| hwrite | m->s | master读写指示 0为读,1为写 |

| hsize[2:0] | m->s | 每次传输的大小指示 |

| hburst[2:0] | m->s | 传输burst指示 |

| hprot[3:0] | m->s | 保护类型该信号一般不用,就没看了 |

| hwdata[31:0] | m->s | 写数据 |

| hrdata[31:0] | s->m | slave返回读数据 |

| hready | s->m | slave在读操作下,为读数据有效指示,写操作下,表示可以接收数据了; |

| hresp[1:0] | s->m | slave指示当前传输状态 |

| hsel | m->s | master选择slave指示 |

6.htrans[1:0]/hsize[2:0]/hburst[2:0]/hresp[1:0]信号解读

1.htrans[1:0]

| htrans[1:0] | 传输类型 | 描述 |

|---|---|---|

| 2’b00 | IDLE | 主设备占用总线,但没进行传输两次burst传输中间主设备可发IDLE此时就算slave被使能,不会从总线上获取任何的数据信号。如果此时salve被选中,那么每一个IDLE周期slave都要通过HRESP[1:0]返回一个OKAY响应 |

| 2’b01 | BUSY | 主设备占用总线,但是在burst传输过程中还没有准备好进行下一次传输一次burst传输中间主设备可发BUSY这时slave不会从总线上收取数据而是等待,并且通过HRESP[1:0]返回一个OKAY响应。需要注意的是,这个transfer需要给出下一拍的地址和控制信号,尽管slave不会去采样。 |

| 2’b10 | NONSEQ | 表明一次单个数据的传输或者一次burst传输的第一个数据地址和控制信号与上一次传输无关。也就是新一次传输的头一个 |

| 2’b11 | SEQ | burst传输接下来的数据地址和上一次传输的地址是相关的,这时总线上的控制信号应当与之前的保持一致,地址视情况递增或者回环。NONSEQ后面紧跟着的就是SEQ; |

2.hsize[2:0]

| hsize[2:0] | 传输大小 |

|---|---|

| 000 | 8bits |

| 001 | 16bits |

| 010 | 32bits |

| 011 | 64bits |

| 100 | 128bits |

| 101 | 256bits |

| 110 | 512bits |

| 111 | 1024bits |

3.hburst[2:0]

注意burst操作不可跨1k(1024)边界

| hburst[2:0] | 类型 | 描述 |

|---|---|---|

| 000 | SINGLE | 单个传输 |

| 001 | INCR | 地增传输 |

| 010 | WRAP4 | 回环传输4个 |

| 011 | INCR4 | 递增的传递4个 |

| 100 | WRAP8 | 回环传输8个 |

| 101 | INCR8 | 递增传输8个 |

| 110 | WRAP16 | 回环传输16个 |

| 111 | INCR16 | 递增传输16个 |

4. hresp[1:0]

| hresp[1:0] | 代表类型 | 描述 |

|---|---|---|

| 00 | OKAY | 传输成功 |

| 01 | ERROR | 传输错误 |

| 10 | RETRY | 请求再次传输 |

| 11 | SPLIT | 请求主设备分离一次传输 (这里需要再理解下) |

7.基本传输

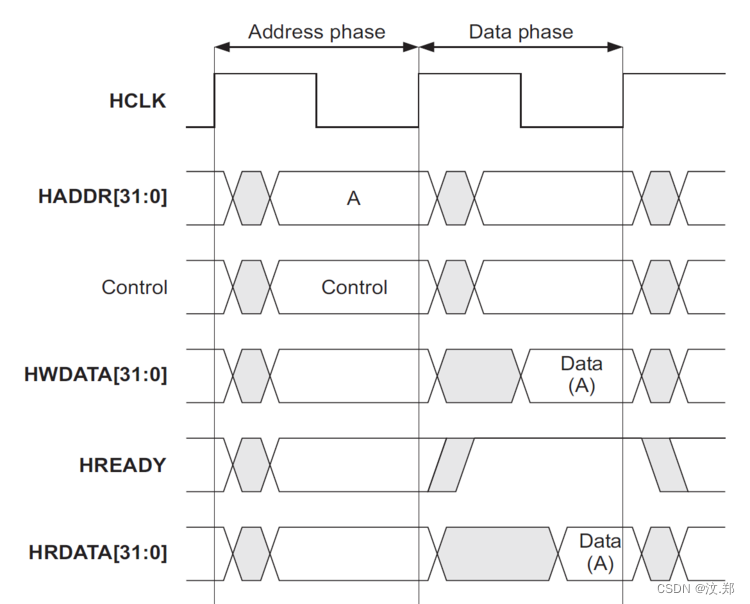

1. 没有等待的读写操作

- master第一个时钟周期发起读写操作,将控制信号及地址信号给到slave;

- 若为写操作,master则在第二拍给出写数据,同时slave将hready拉高代表可以接收数据,则传输结束;注意slave给出hready信号就会给出hresp一系列信号等;

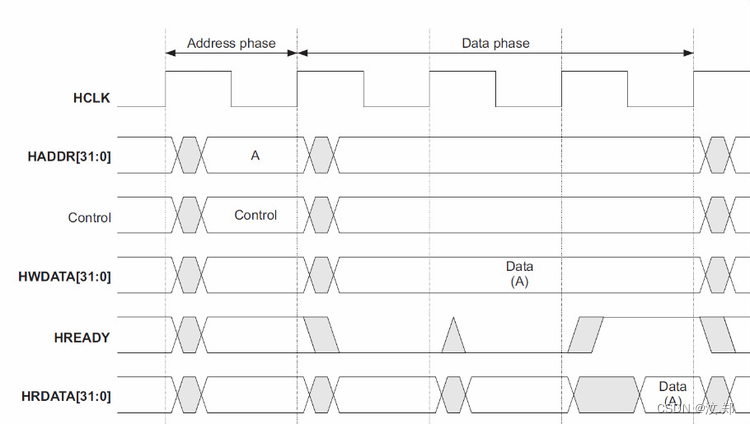

2.有等待的传输

slave可以及时处理master请求,但也可能存在slave太慢不能立即处理的情况。这时需要让master稍微等一等,需要slave插入一些等待的状态。如下图所示,HREADY信号在第二和第三周期拉低,意在告诉master,slave不能立即处理,需要master等待2个周期。在这里需要注意2点:

如果是写操作,master需要在等待期间保持写数据不变,直到本次传输完成;

如果是读操作,slave不需要一开始就给出数据,仅当HREADY拉高后才给出有效数据。

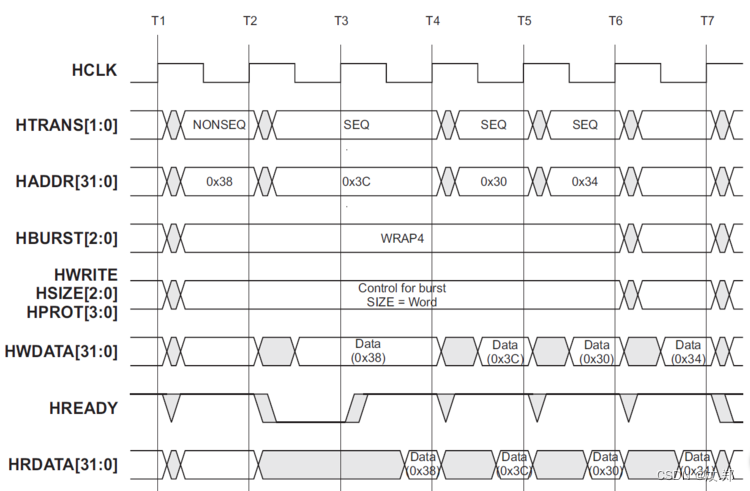

3. 多个流水传输

T1,master传入地址和控制信号,因为是新的burst开始,transfer的类型是NONSEQ;

T2,由于master不能在第二个周期里处理第二拍,所以master使用BUSY transfer来为自己延长一个周期的时间。注意,虽然是延长了一个周期,但是master需要给出第二个transfer的地址和控制信号;

T3,slave采集到了master发来的BUSY,知道master需要等待一拍,所以slave会忽略这个BUSY transfer;

T3,master发起了第二个transfer,因为是同一个burst的第二个transfer,所以transfer的类型是SEQ;

T5,slave将HREADY信号拉低,告诉master需要等待一个周期;

T8时刻完成最后一个transfer。

需要注意的 虽然slave会忽略掉BUSY transfer,但是master也需要给出下一拍的地址和控制信号。

(直接复制过来了,还是建议看看原文哈)

这里每个传输至少两拍,可以流水传输;slave没有等待的话就很顺,有需要等待的话,注意数据在slave没有准备好的情况下,master需要保持相关的数据不动;

3.WRAP4的传输

这里不同的点就是连续了4个传输;

8. hready_out 与 hready_in;

in与out的概念是相对slave来说的,对于slave是一个in信号,还是一个out信号;

- hready_in:总线master侧的信号,用于表示上一笔传输结束,总线准备好开始一次新的传输,主要是用于切换slave时用,让后一个slave(2)的数据始终保持在前一个slave(1)的后面,不会因为slave1的延时导致总线混乱;

- hready_out:总线slave侧信号,表示slave可以接收数据;

8.问题求教

这里有几个疑惑希望有大佬可以解答一下:

- 如果已经指定为WRAP4了,那master还需要按SINGLE方式去计算地址给到地址接口么;

- 是不是只有在数据接口足够大的时候才可以配置相关的hsize;如图中数据位宽为32bits,那么我hsize的一个可配置的范围是否只能是0-2;不能再多了?

1563

1563

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?