AXI(Advanced eXtensible Interface)是一种高性能、高带宽的总线协议,用于在集成电路系统中连接和交互各个IP(Intellectual Property)模块。它是由ARM公司提出的,并被广泛应用于众多的系统级集成电路设计中。

AXI协议定义了一组规范和规则,用于描述数据传输、信号控制和传输协议,以实现可靠和高效的通信。它提供了多种类型的总线接口,包括AXI4、AXI4-Lite、AXI4-Stream等。在上面发表的博文里已经介绍过AXI-Stream了接下来,这篇主要介绍AXI4的功能。

总的来说,AXI协议提供了一种灵活、高性能的总线接口,适用于复杂的集成电路设计和高速数据传输应用。它在各种系统级设计中被广泛使用,并且被许多FPGA和ASIC供应商所支持和采用。

一.介绍

1.1关于AXI协议

• 适用于高带宽和低延迟设计。

• 无需使用复杂的电桥即可提供高频操作。

• 该协议满足各种组件的接口要求。

• 适用于具有高初始访问延迟的内存控制器。

• 提供互连架构实施的灵活性。

• 向下兼容AHB 和APB 接口。

AXI协议的关键特性是:

• 独立的地址/控制和数据阶段。

• 支持使用字节选通的未对齐数据传输。

• 使用仅发出起始地址的基于突发的事务。

• 独立的写入和读取数据通道,可提供低成本的直接内存访问(DMA)。

• 支持发布多个未完成的地址。

• 支持乱序交易完成。

• 允许轻松添加寄存器级以提供时序收敛。

1.2AXI结构

AXI主要包括五个数据通道,分别是:

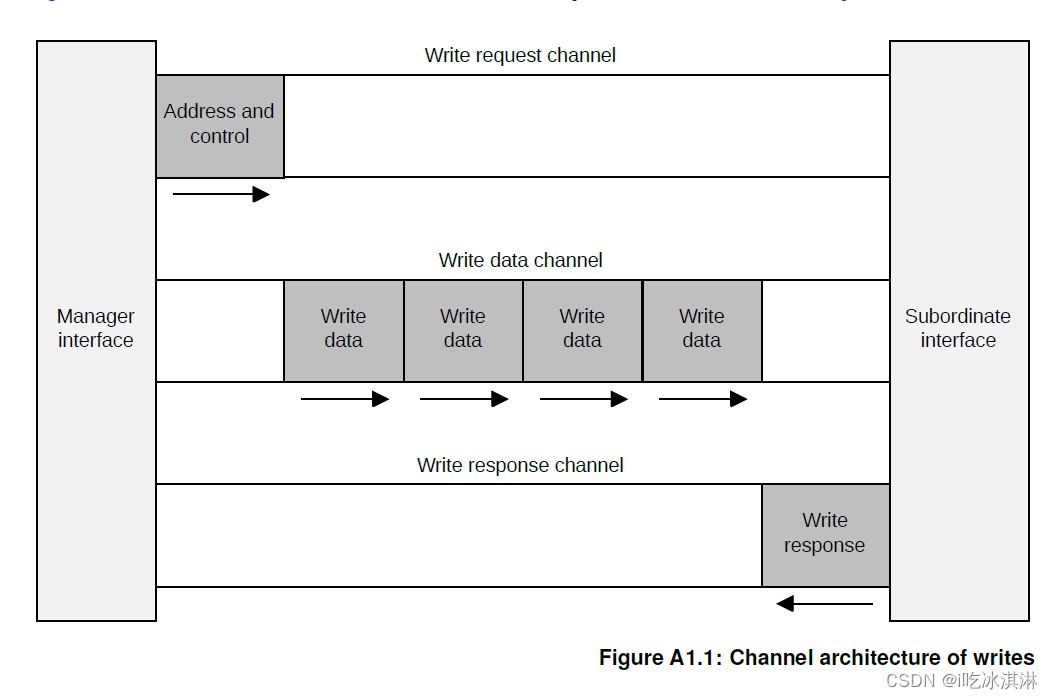

①AW-写请求通道:主要包括写地址和control信号 ②W-写数据 ③B-写相应

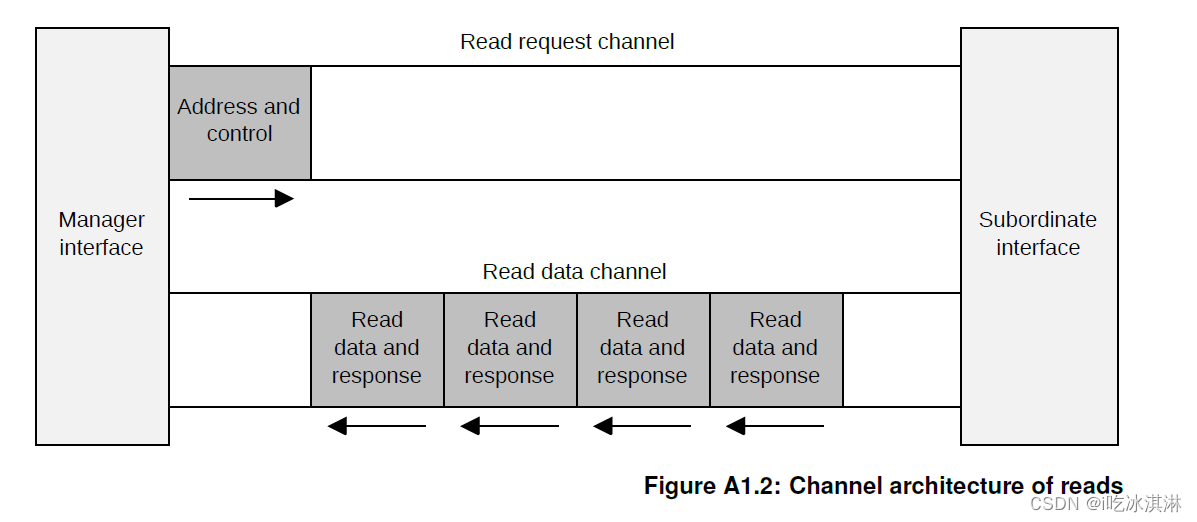

④AR-读请求 ⑤R-读数据

写过程

读过程

1.2.1通道定义

这五个通道中都有独立的VALID和READY信号以提供双方握手机制。DATA_WIDTH=2^3-2^10

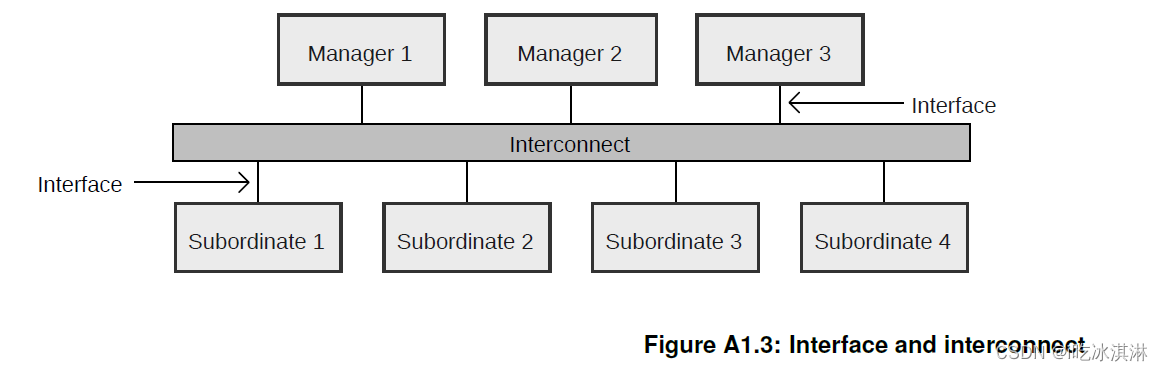

1.2.2接口与互联

AXI提供三种接口:

①主设备到互联

②从设备到互联

③主设备到从设备

1755

1755

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?