目录

一、概念

MTBF(Mean Time Between Failure平均故障间隔时间)是一种统计指标,表示系统或组件预计的平均故障间隔时间。它是评估 FPGA 可靠性的关键指标,尤其是在故障可能造成严重后果的关键任务应用中。

设计中当异步信号跨时钟域传输时,触发器可能采样在信号翻转的临界时刻出现亚稳态。触发器输出可能在一段时间内无法稳定到 0 或 1,甚至导致后续逻辑错误。为了降低这种概率,通常会在跨时钟域时使用 同步器(synchronizer,级联触发器),而MTBF 用来量化“系统因为亚稳态导致出错的平均时间”。

二、MFTB计算

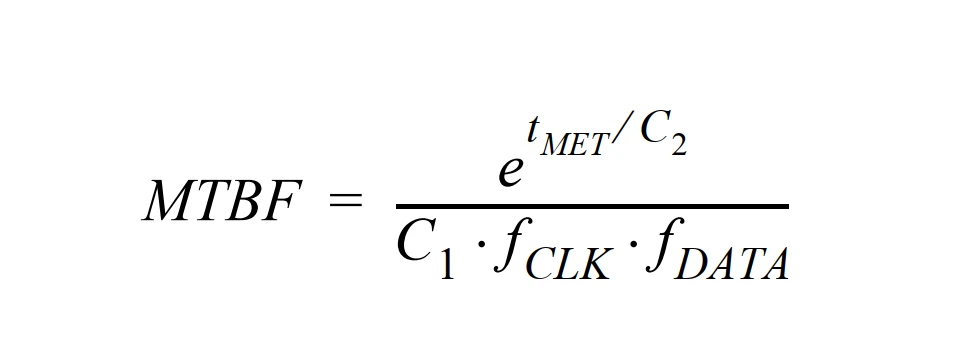

MTBF值越大表示设计越稳定(如值为几百上千年),不同的应用场景要求不同,如使用长的医疗设备的MTBF要求比常用的视频播放设备要求高。MTBF的计算公式如下

其中:

-

C1,C2常量:取决于器件工艺和运行环境

-

fclk:接收异步信号中时钟域的时钟频率,值越大MTBF越小

-

fdata:异步输入信号的翻转频率,值越大MTBF越小

-

tMET:可用的亚稳态建立时间,或者说是寄存器的tco外的可用时序裕量,用于将潜在的亚稳态信号解析为已知值,同步链的 tMET 是链中每个寄存器的输出时序裕度之和。

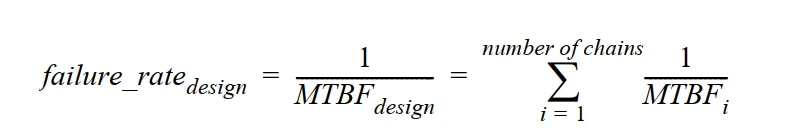

整体设计的MTBF可以通过设计中每个同步器链的MTBF来确定。同步器的故障率为1/MTBF,整个设计的故障率是通过将每个同步器链的故障率相加来计算的,设计的MTBF是1/failure_ratedesign,如下所示:

三、如何改善MTBF

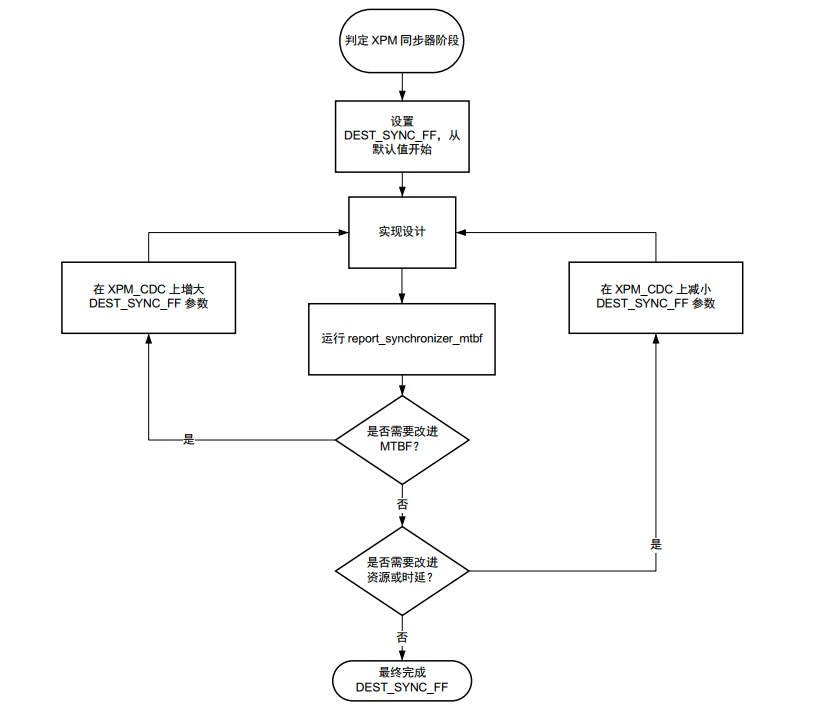

设计中的MTBF由同步器MTBF和单事件故障(SEU)导致的器件故障时间决定。单事件故障很大程度取决于工艺和器件大小)。同步器的MTBF受异步CDC数量,每个交汇点处同步器级数,接收触发器的频率,源点的切换速率。以AMD的Ultrascale器件为例,MTBF的优化流程如下。

对于一些常用的场景,可以做如下改善

1)所有跨域单比特信号,保证最少 2 级同步器。

2)对于脉冲信号,先在源域做 toggle 或脉冲展宽,再同步(避免短脉冲丢失)。

3)对多比特或数据流,采取握手/异步 FIFO,绝不逐位同步。

4)在源域寄存,先进行去抖/限速操作。

四、Vivado报告MTBF

在vivado中,通过report_synchronizer_mtbf可以对跨时钟域路径进行计算MTBF并报告

以如下设计为例

module report_mtbf(in1,in2,rst,clk1,clk2,ff3,ff3_p);

input in1,in2,rst,clk1,clk2;

output ff3,ff3_p;

reg ff1,ff2,ff3;

(*ASYNC_REG="TRUE"*) reg ff1_p,ff2_p,ff3_p;

always@(posedge clk1,negedge rst)

if(!rst)

ff1<=1'b0;

else begin

ff1<=in1;

end

always@(posedge clk2,negedge rst)

if(!rst)

ff2<=1'b0;

else begin

ff2<=ff1;

end

always@(posedge clk2,negedge rst)

if(!rst)

ff3<=1'b0;

else begin

ff3<=ff2;

end

always@(posedge clk1,negedge rst)

if(!rst)

ff1_p<=1'b0;

else begin

ff1_p<=in2;

end

always@(posedge clk2,negedge rst)

if(!rst)

ff2_p<=1'b0;

else begin

ff2_p<=ff1_p;

end

always@(posedge clk2,negedge rst)

if(!rst)

ff3_p<=1'b0;

else begin

ff3_p<=ff2_p;

end

endmodule 时序约束

create_clock -period 10.000 -name clk1 -waveform {0.000 5.000} -add [get_ports clk1]

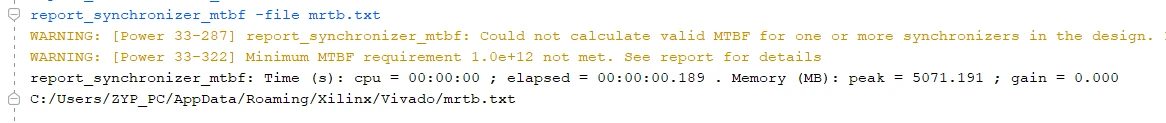

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} -add [get_ports clk2]在Tcl Console执行report_synchronizer_mtbf -file mrtb.txt,mrtb.txt为报告文件

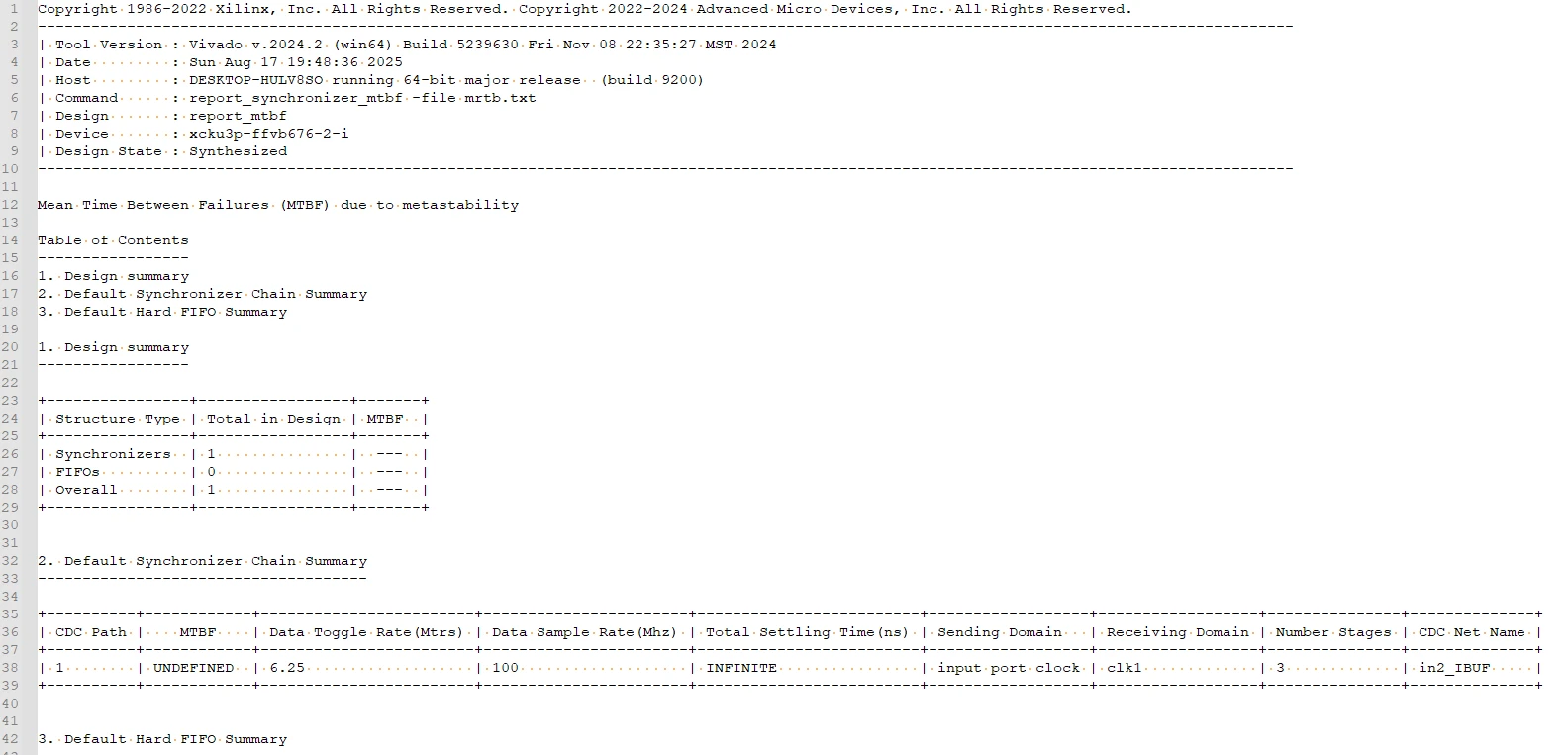

报告主要由3部分组成,Design Summary,Default Synchronizer Chain Summary,Default Hard FIFO Summary,对于跨时钟域路径ff1到ff2无Async_reg属性时,无法进行MTBF分析。

五、参考资料

1、《White Paper Understanding Metastability in FPGAs》

2、《ug949-vivado-design-methodology》

676

676

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?