参考 百度文库:http://wenku.baidu.com/view/cd93f34ecf84b9d528ea7a95

安装完成之后,先在Modelsim中File——New——Library,默认会建立work库

建立好work库后,File——New——Project,新建一个工程,导入写好的verilog文件和verilog test bench文件,并在Workspace空白处右键编译所有文件。

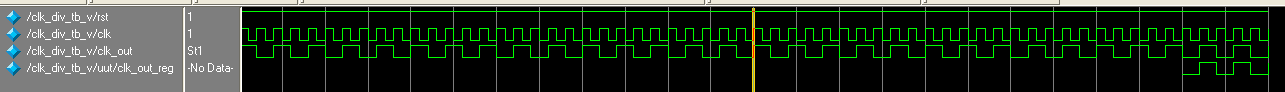

当前在Workspace的Project标签下,选择Library标签,可以看到work目录,选择刚才建立的test bench文件,右键,选择Simulate,即可打开Workspace的Sim标签,选中uut,即可在右侧Objects窗口看到所有的信号,包括输入输出信号,和中间信号,选中所有信号,右键Add to wave,即可添加到Wave波形中。

下面输入框中可以设置仿真步长,点击右侧的run按钮,即可执行一个仿真步长的仿真。

在ISE中启动Modelsim,会首先仿真一定的时间,然后在Workspace的Sim标签下选中uut,添加中间信号时,中间信号只能在出现在后面的仿真中,而不能出现在前面的仿真中。

把Wave窗口关掉,重新仿真,前面的信号仍然不能产生,仍然是从后面接着仿真。

因此,仿真中间信号,目前,应该在Modelsim中建立工程仿真。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?