提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

一、用与非门电路实现四路表决器

四路表决器:当四个输入端A、B、C、D中有三个或四个“1”时,输出端才为“1”。

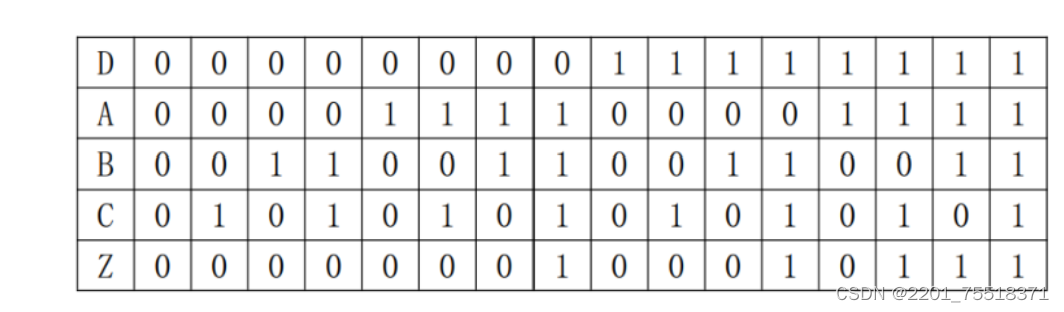

其真值表如下所示:

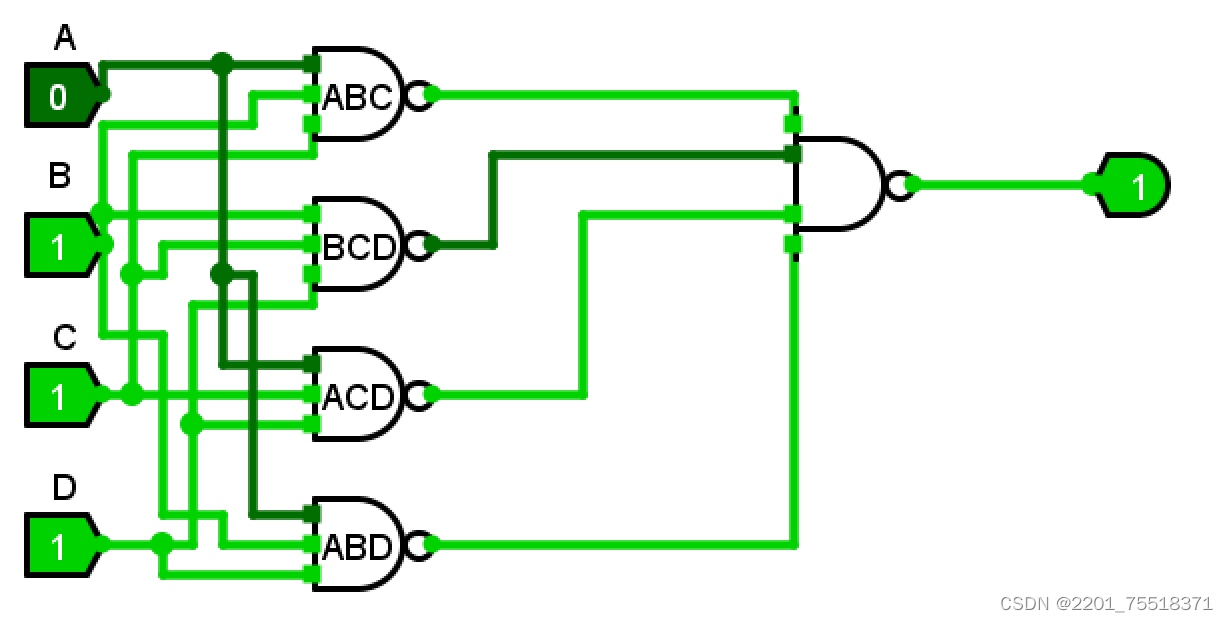

根据真值表使用卡诺图可以得出化简后用与非表达的逻辑表达式:

![]()

由表达式可知仿真电路需要用到5个与非门,在实际搭建电路时可以用到3个74LS20芯片或者2个74LS00芯片。仿真电路图如下:

二、用表决器将投票的结果显示在LED屏上

1.4位全加器

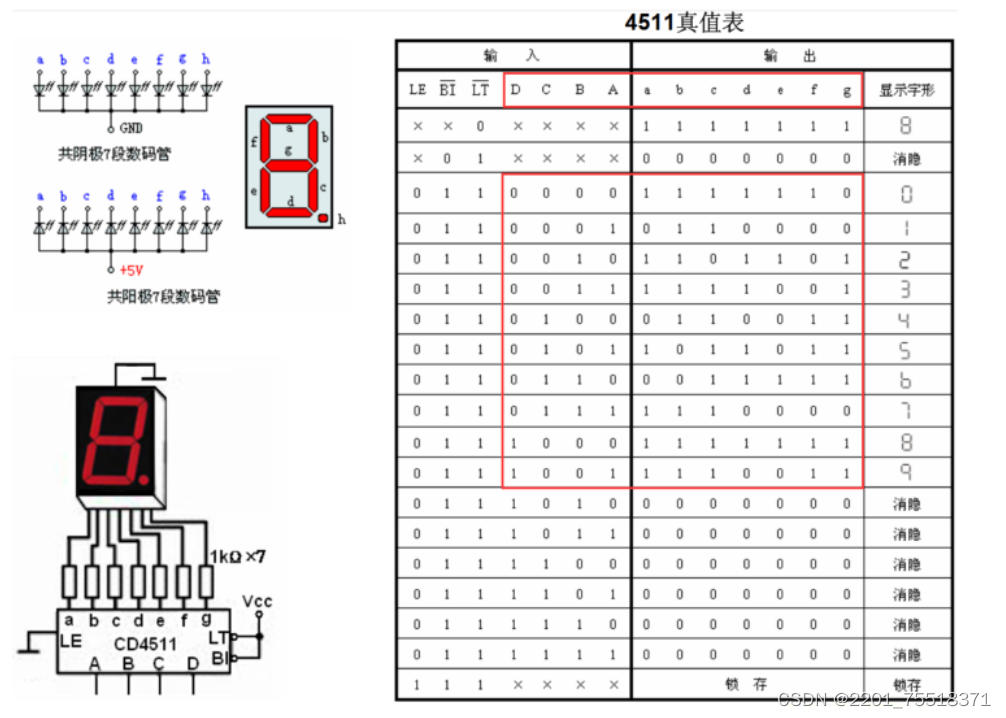

要求将4位输入中将输入为1的票数相加,然后将总的票数显示在LED上。7段数码显示管(LED)是由7个单独LED二极管组合而成,经常用来显示0-9这些数字,它可以用4个输入项A-B-C-D,和7个输出项a-g的逻辑关系真值表来表示。

原理如上图所示,因为7段数码显示管只能将二进制转换为十进制数字显示,所以要先将投票为1的全部相加,然后转化为二进制。既然需要相加且有4个输入,所以用到4位数相加的全加器。其电路仿真图如下所示:

最后得到的二进制可输入7段数码二极管转化成十进制。

2.简化7400电路

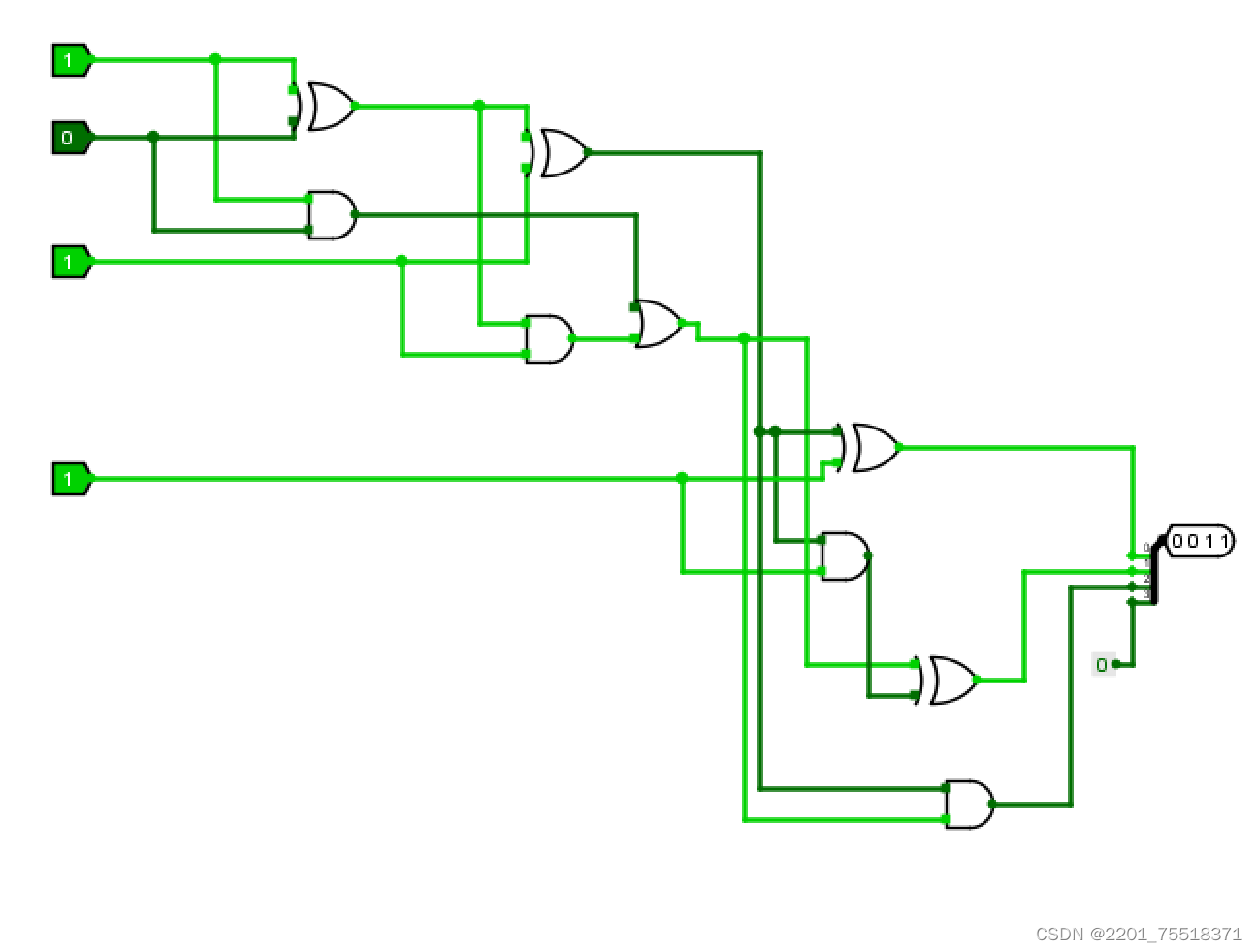

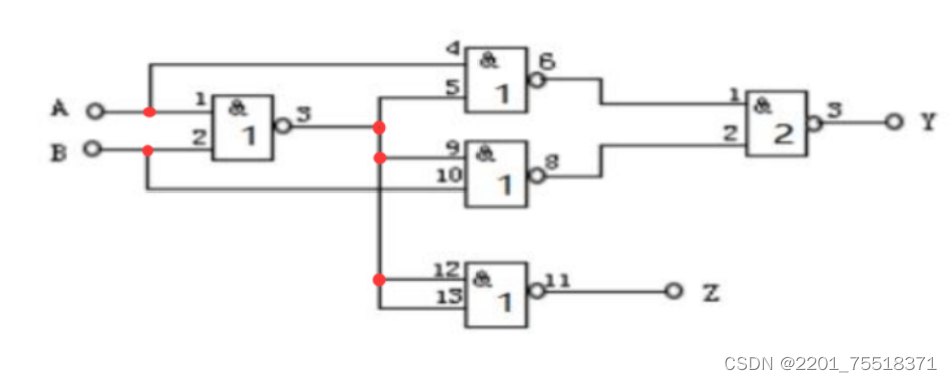

7400逻辑原理图如下所示:

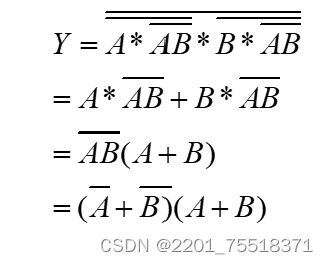

根据此图列出逻辑表达式并化简过程如下:

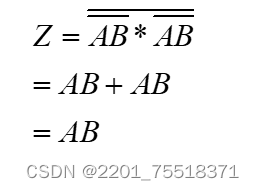

化简后的电路仿真如下:

测试结果与7400真值表一致

总结

此次实验将逻辑电路同实际电路搭建以及逻辑关系式化简相关联,加深了对逻辑电路的理解,同时,在三位全加器的基础上改成4位全加器更加加深了对全加器原理的理解。

文章介绍了如何用与非门电路实现四路表决器,将其与LED屏结合,利用4位全加器计算投票结果,并通过74LS20和7400电路简化过程。实验深化了对逻辑电路和全加器的理解。

文章介绍了如何用与非门电路实现四路表决器,将其与LED屏结合,利用4位全加器计算投票结果,并通过74LS20和7400电路简化过程。实验深化了对逻辑电路和全加器的理解。

912

912

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?