目录

时钟源

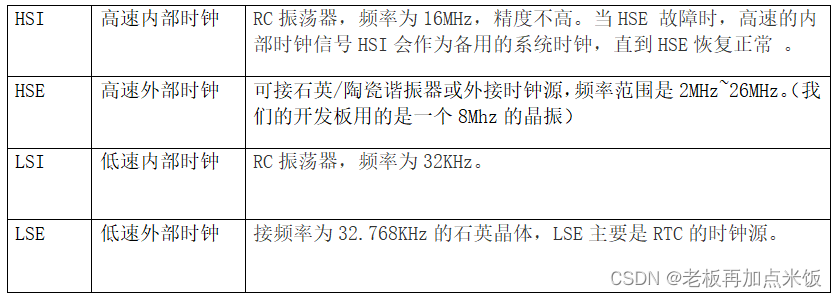

为什么STM32有四个时钟源(HSE、 LSE、HSI、LSI)?

答:为了兼容不同速度的外设。 不同外设需要不同的时钟频率,因为所有外设时钟默认都是关闭状态,所以使用时才开启这个外设的时钟。减少不必要的资源浪费,而且有些外设也接受不了这么高的频率。

51单片机无法做到低功耗。因为51单片机时钟是默认开启的。

锁相环倍频输出(PLL):8Mhz。理论上不能算是时钟源,只是接收时钟源后对其进行分/倍频,分/倍频倍数可修改参数调节。(我们的开发板输出168Mhz稳定,已测最大超频224Mhz)

精度需求不高用内部,精度要求高用外部时钟。

总线

不用记,固件库里都有。

APB

低速 APB1 域的最大允许频率为 42 MHz。分频系数4:168/4=42MHz

/**

* @brief Enables or disables the Low Speed APB (APB1) peripheral clock.

* @note After reset, the peripheral clock (used for registers read/write access)

* is disabled and the application software has to enable this clock before

* using it.

* @param RCC_APB1Periph: specifies the APB1 peripheral to gates its clock.

* This parameter can be any combination of the following values:

* @arg RCC_APB1Periph_TIM2: TIM2 clock

* @arg RCC_APB1Periph_TIM3: TIM3 clock

* @arg RCC_APB1Periph_TIM4: TIM4 clock

* @arg RCC_APB1Periph_TIM5: TIM5 clock

* @arg RCC_APB1Periph_TIM6: TIM6 clock

* @arg RCC_APB1Periph_TIM7: TIM7 clock

* @arg RCC_APB1Periph_TIM12: TIM12 clock

* @arg RCC_APB1Periph_TIM13: TIM13 clock

* @arg RCC_APB1Periph_TIM14: TIM14 clock

* @arg RCC_APB1Periph_WWDG: WWDG clock

* @arg RCC_APB1Periph_SPI2: SPI2 clock

* @arg RCC_APB1Periph_SPI3: SPI3 clock

* @arg RCC_APB1Periph_USART2: USART2 clock

* @arg RCC_APB1Periph_USART3: USART3 clock

* @arg RCC_APB1Periph_UART4: UART4 clock

* @arg RCC_APB1Periph_UART5: UART5 clock

* @arg RCC_APB1Periph_I2C1: I2C1 clock

* @arg RCC_APB1Periph_I2C2: I2C2 clock

* @arg RCC_APB1Periph_I2C3: I2C3 clock

* @arg RCC_APB1Periph_CAN1: CAN1 clock

* @arg RCC_APB1Periph_CAN2: CAN2 clock

* @arg RCC_APB1Periph_PWR: PWR clock

* @arg RCC_APB1Periph_DAC: DAC clock

* @arg RCC_APB1Periph_UART7: UART7 clock

* @arg RCC_APB1Periph_UART8: UART8 clock

* @param NewState: new state of the specified peripheral clock.

* This parameter can be: ENABLE or DISABLE.

* @retval None

*/

void RCC_APB1PeriphClockCmd(uint32_t RCC_APB1Periph, FunctionalState NewState)//最大允许频率42Mhz高速 APB2 域的最大允许频率为 84 MHz。分频系数2:168/2=84MHz

/**

* @brief Enables or disables the High Speed APB (APB2) peripheral clock.

* @note After reset, the peripheral clock (used for registers read/write access)

* is disabled and the application software has to enable this clock before

* using it.

* @param RCC_APB2Periph: specifies the APB2 peripheral to gates its clock.

* This parameter can be any combination of the following values:

* @arg RCC_APB2Periph_TIM1: TIM1 clock

* @arg RCC_APB2Periph_TIM8: TIM8 clock

* @arg RCC_APB2Periph_USART1: USART1 clock

* @arg RCC_APB2Periph_USART6: USART6 clock

* @arg RCC_APB2Periph_ADC1: ADC1 clock

* @arg RCC_APB2Periph_ADC2: ADC2 clock

* @arg RCC_APB2Periph_ADC3: ADC3 clock

* @arg RCC_APB2Periph_SDIO: SDIO clock

* @arg RCC_APB2Periph_SPI1: SPI1 clock

* @arg RCC_APB2Periph_SPI4: SPI4 clock

* @arg RCC_APB2Periph_SYSCFG: SYSCFG clock

* @arg RCC_APB2Periph_TIM9: TIM9 clock

* @arg RCC_APB2Periph_TIM10: TIM10 clock

* @arg RCC_APB2Periph_TIM11: TIM11 clock

* @arg RCC_APB2Periph_SPI5: SPI5 clock

* @arg RCC_APB2Periph_SPI6: SPI6 clock

* @arg RCC_APB2Periph_SAI1: SAI1 clock (STM32F42xxx/43xxx devices)

* @arg RCC_APB2Periph_LTDC: LTDC clock (STM32F429xx/439xx devices)

* @param NewState: new state of the specified peripheral clock.

* This parameter can be: ENABLE or DISABLE.

* @retval None

*/

void RCC_APB2PeriphClockCmd(uint32_t RCC_APB2Periph, FunctionalState NewState)//最大允许频率84MhzAHB

AHB 域的最大频率为 168 MHz。分频系数1:168/1=168MHz

//无需记忆,固件库可查

/**

* @brief Enables or disables the AHB1 peripheral(外围的) clock.

* @note After reset(复位), the peripheral clock (used for(用于) registers(寄存器)

* read/write access(权限))is disabled and the application software has to

* enable this clock before using it.使能或失能前必须开启时钟

* @param RCC_AHBPeriph: specifies the AHB1 peripheral to gates its clock.

* This parameter(参数) can be any combination(组合) of the following(下列)

values(值):

* @arg RCC_AHB1Periph_GPIOA: GPIOA clock

* @arg RCC_AHB1Periph_GPIOB: GPIOB clock

* @arg RCC_AHB1Periph_GPIOC: GPIOC clock

* @arg RCC_AHB1Periph_GPIOD: GPIOD clock

* @arg RCC_AHB1Periph_GPIOE: GPIOE clock

* @arg RCC_AHB1Periph_GPIOF: GPIOF clock

* @arg RCC_AHB1Periph_GPIOG: GPIOG clock

* @arg RCC_AHB1Periph_GPIOG: GPIOG clock

* @arg RCC_AHB1Periph_GPIOI: GPIOI clock

* @arg RCC_AHB1Periph_GPIOJ: GPIOJ clock (STM32F42xxx/43xxx devices)

* @arg RCC_AHB1Periph_GPIOK: GPIOK clock (STM32F42xxx/43xxx devices)

* @arg RCC_AHB1Periph_CRC: CRC clock

* @arg RCC_AHB1Periph_BKPSRAM: BKPSRAM interface clock

* @arg RCC_AHB1Periph_CCMDATARAMEN CCM data RAM interface clock

* @arg RCC_AHB1Periph_DMA1: DMA1 clock

* @arg RCC_AHB1Periph_DMA2: DMA2 clock

* @arg RCC_AHB1Periph_DMA2D: DMA2D clock (STM32F429xx/439xx devices)

* @arg RCC_AHB1Periph_ETH_MAC: Ethernet MAC clock

* @arg RCC_AHB1Periph_ETH_MAC_Tx: Ethernet Transmission clock

* @arg RCC_AHB1Periph_ETH_MAC_Rx: Ethernet Reception clock

* @arg RCC_AHB1Periph_ETH_MAC_PTP: Ethernet PTP clock

* @arg RCC_AHB1Periph_OTG_HS: USB OTG HS clock

* @arg RCC_AHB1Periph_OTG_HS_ULPI: USB OTG HS ULPI clock

* @param NewState: new state of the specified peripheral clock.

* This parameter can be: ENABLE or DISABLE.

* @retval None

*/

void RCC_AHB1PeriphClockCmd(uint32_t RCC_AHB1Periph, FunctionalState NewState)//最大允许频率168Mhz系统时钟SYSCLK

系统时钟来源可以是:

HSI

、

PLLCLK

、

HSE

,具体的由时钟配置寄存器

RCC_CFGR

的

SW (选择器)

位配置。

如果系统时钟是由

HSE

经过

PLL

倍频之后的

PLLCLK

得到,当

HSE

出现故障的时候,系统时钟会

切换为

HSI=16M

,直到

HSE

恢复正常为止。

定时器除了挂载在一分频的AHB以外,二分频的APB2和四分频的APB1都需要翻倍(芯片设定)。芯片不同会有所区别。

//配置TIM1时基

TIM_TimeBaseInitTypeDef TIM_TimeBaseStructure;

TIM_TimeBaseStructure.TIM_CounterMode=TIM_CounterMode_Up;

//APB1 42Mhz TIM1=84Mhz

TIM_TimeBaseStructure.TIM_Period= 50000; //ARR计数最大值 输入捕获有什么影响?

TIM_TimeBaseStructure.TIM_Prescaler= 84-1;//PSC分频系数

//84Mhz/84=1Mhz 数一个数:1/1000000 s 1/1Mhz = 168/168M x

TIM_TimeBaseInit(TIM1, &TIM_TimeBaseStructure);时间是频率的倒数

最大定时时间S=2^(SysTick定时器位数)/(时钟源频率/分频)

2437

2437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?