这个例子展示了如何使用Matlab的 Serial Link Designer 应用程序执行高速信号链路的PCB预布局(pre-layout)串扰分析,该应用程序提供专用的系统级设计和分析环境,可以帮助设计者确定干扰源信号对通道整体 BER 的影响,从而预测设计方案如何影响设计裕量。

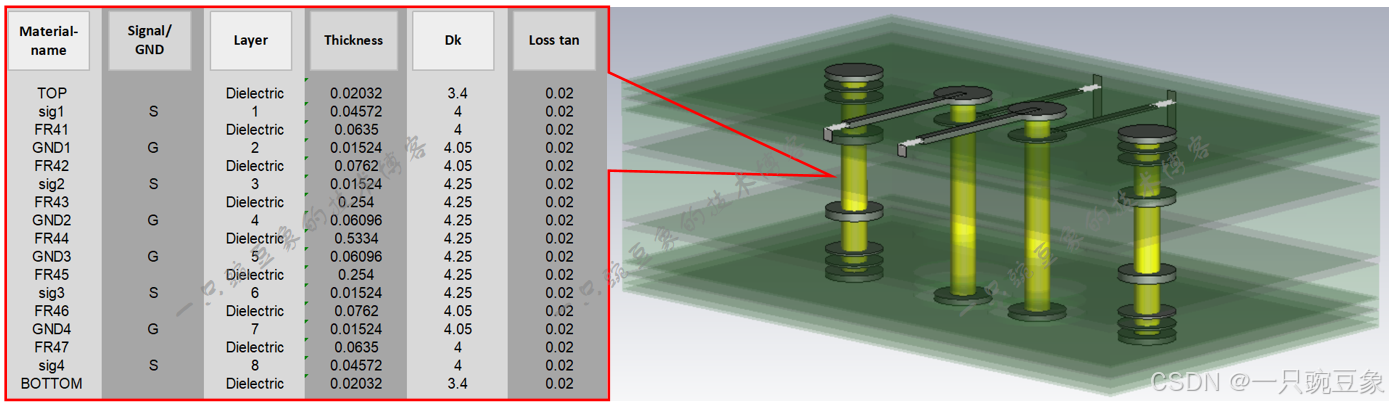

本例基于一个8层板的高速链路设计评估(速率10Gbps,8B10B编码),需要考察长距离并行走线对眼图裕量的影响,并且,整条链路需要在L1和L3之间实施换层(同时参考L2)。

打开Matlab主程序,并在“信号处理和通信”APP菜单栏中找到 Serial Link Designer ,打开后创建一个空白的子工程;

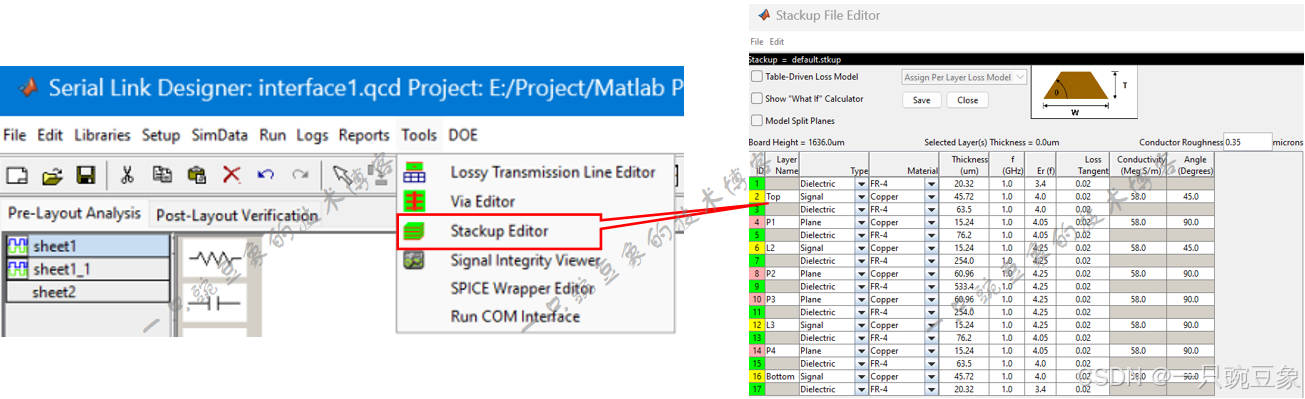

在工程文件的主菜单的 Tools 栏目中,点击选择 Stackup Editor ,手动编辑8层板的叠构信息;

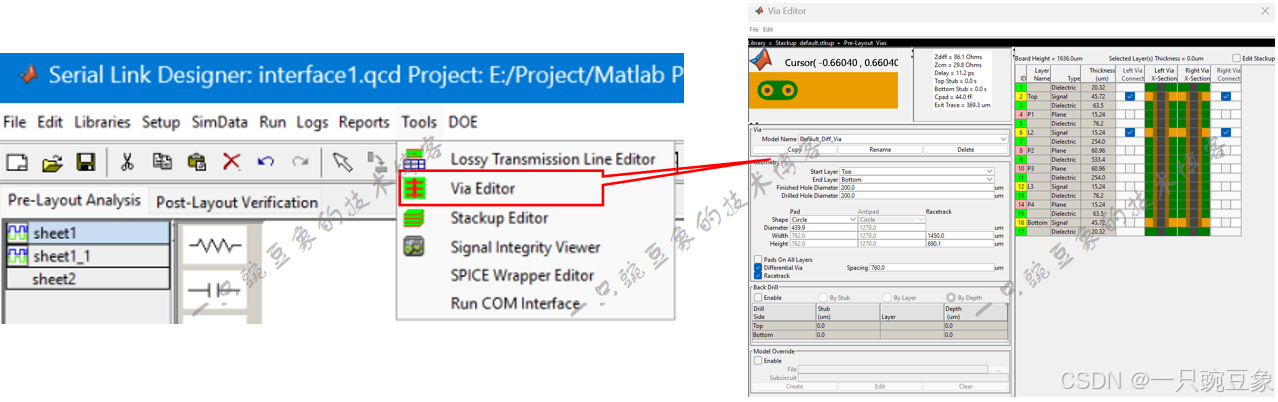

同样在工程文件的主菜单的 Tools 栏目中,点击选择 Via Editor ,手动编辑换层通孔的设计参数;

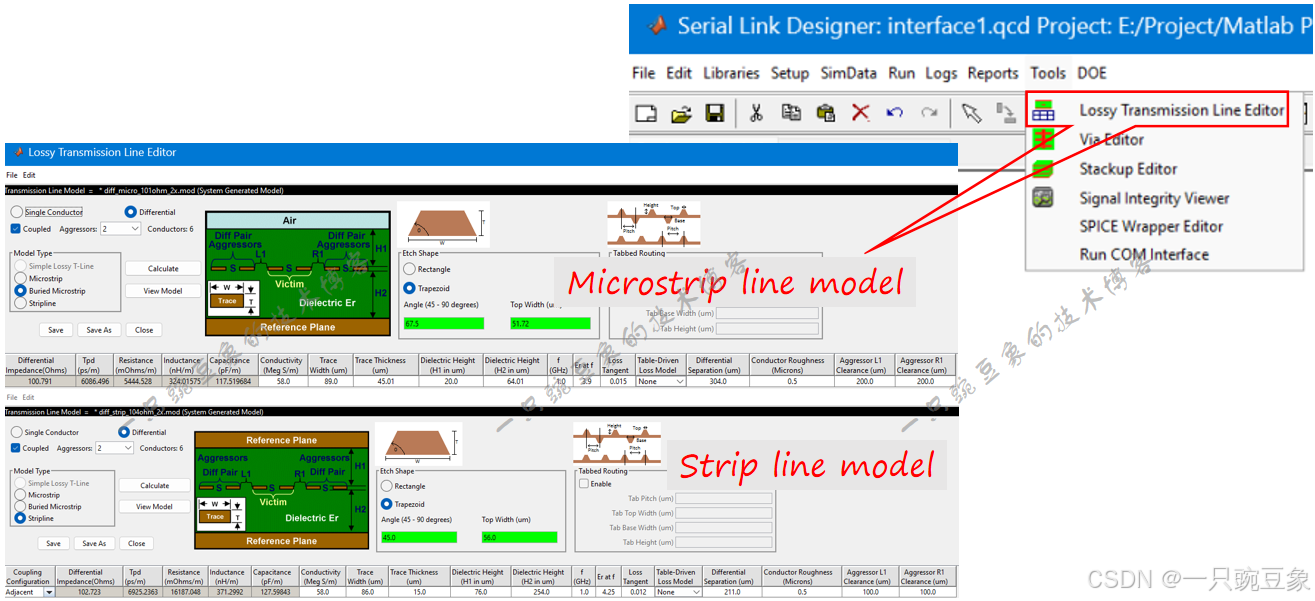

还是在工程文件的主菜单的 Tools 栏目中,点击选择 Lossy Transmissio Line Editor ,手动编辑PCB差分微带和带状线的设计参数,图中展示的是并行三组差分耦合通道的编辑界面;

完成上述的模型创建后,还需了解 Serial Link Designer 是如何考虑时域仿真中串扰的?

Matlab给出了以下两种分析方法:

1. Semi-Analytic -- 从统计分析的角度对串扰进行分析,在没有串扰的情况下模拟系统中的每个通道,并单独计算串扰的概率密度函数 (PDF),然后,将串扰 PDF 与眼图进行卷积,并生成浴盆曲线和误码率估计值;

2. Explicit -- 系统中的所有通道在时域中同时仿真,因此接收器决策点的波形是所需信号和串扰干扰源的组合结果。

建议采用Semi-Analytic模式,在时域内模拟所需信号的几百万比特,然后利用统计技术估计噪声、串扰和时钟相位噪声的影响。这样做的优点是可以同时研究时变和非线性效应,并且,这种方法对于确定最坏情况下的性能非常有用。

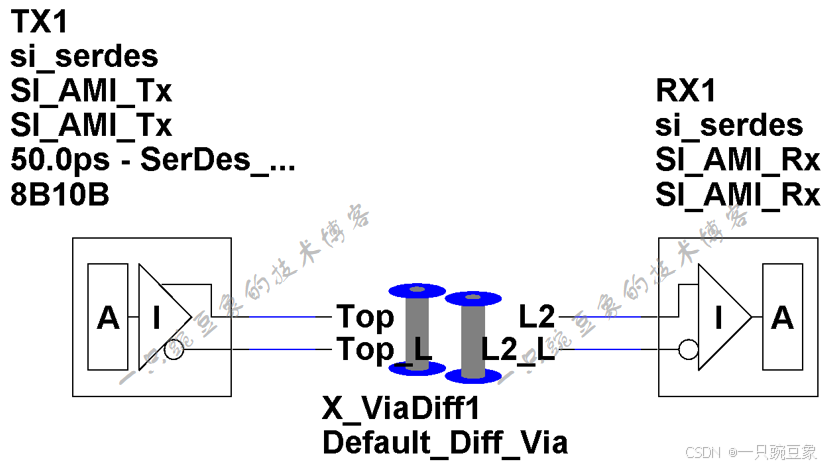

在空白工程中,创建如下的通孔仿真链路,通孔数据如上文所述,驱动模型则使用自带的PRBS编码驱动源;

并且,为了评估Matlab建模的准确性,利用CST进行了信号换层通孔的三维建模,模型及叠构信息如下图所示:

两者的仿真数据对比如下,从趋势上看,Matlab和CST的通孔模型均预测出了由于通孔残桩所产生的SDD21谐振的现象,并且,谐振点的预测也较为接近,如果不是特别在意结果的精度,Matlab的仿真结果完全可以用于前仿真的设计评估。

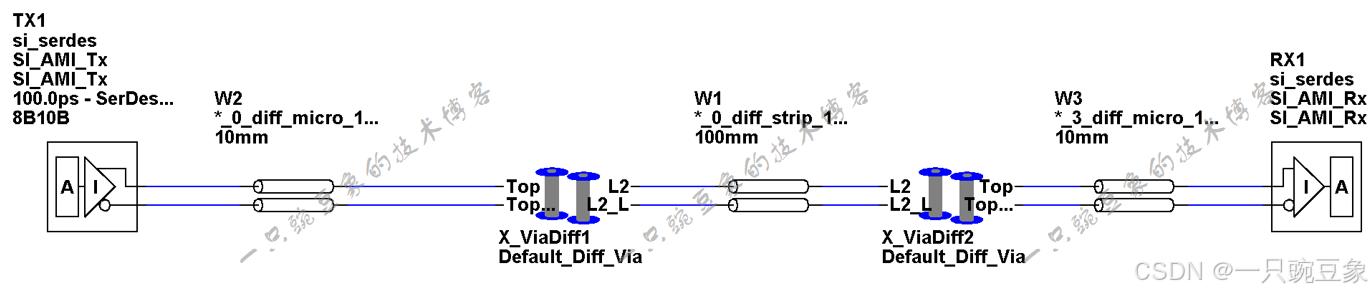

在上述仿真的基础之上,创建了一条单信号收发链路,其中,包括了两边各10mm的微带走线、两个差分换层通孔和一根100mm的带状走线;

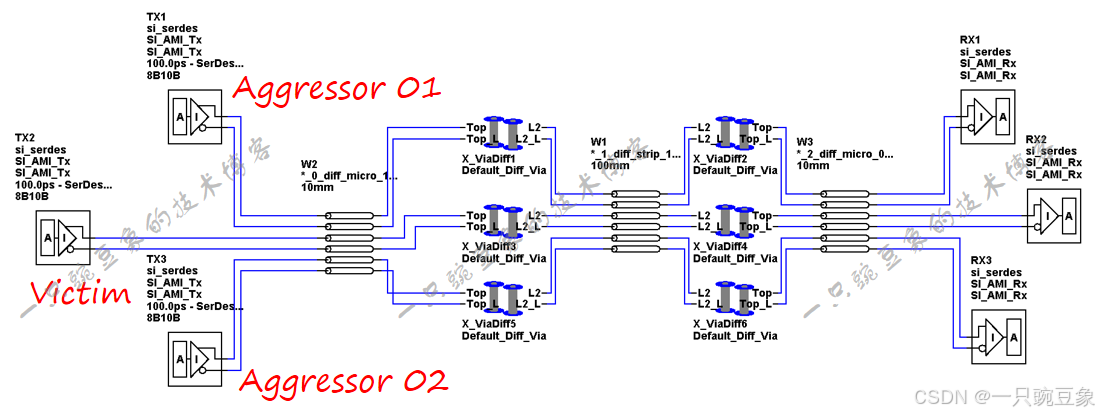

在以上所创建的链路模型基础上,再创建一条包含两路攻击线的串扰链路模型,而被攻击线位于两条攻击线之间,线间距的信息已在上文创建传输线模型时定义;

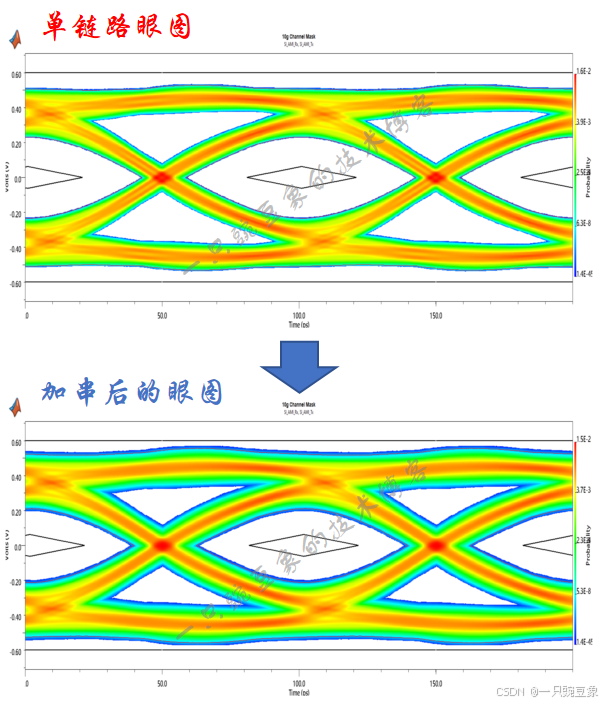

将上述两种链路条件下,所得到的统计眼图效果进行对比,可以明显地观察到,在攻击线的影响下,中间链路的眼图裕量被压缩。

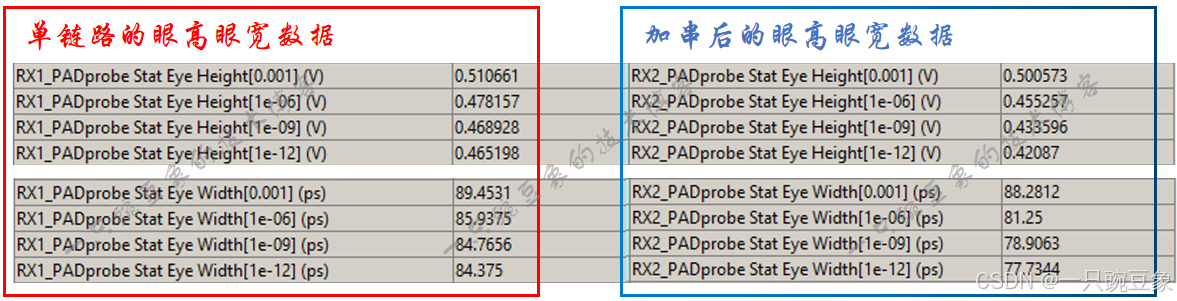

通过具体量化数据的对比,可以更为明显地发现通道耦合对眼图裕量的影响,如下图所示,分别对比了BER等级1E-3 / 1E-6 / 1E-9 / 1E-12 中的眼高眼宽数据,串扰的影响非常直观地体现了出来。

最后,可以在Matlab的主界面中输入下述指令,获取以上链路串扰分析的设计模板,从而节省操作时间,提高分析工作效率。

366

366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?