关注 望森FPGA 查看更多FPGA资讯

这是望森的第 29 期分享

作者 | 望森

来源 | 望森FPGA

目录

摘要

本文主要介绍了常用的 Intel/Altera FPGA 和 Xilinx FPGA的内部结构,并对 FPGA 中一些基本单元进行了介绍~

1 常用FPGA的结构

1.Intel/Altera FPGA

Intel/Altera FPGA 由 LAB、布线资源、存储资源、时钟管理单元 PLL 、I/O 引脚、专用硬件块、配置逻辑等组成。

(1)LE

Intel/Altera FPGA 的可编程单元叫 LE (Logic Element,逻辑单元),由一个查找表 LUT 、一个寄存器 Flip-Flop 和进位链 Carry Chain 组成。

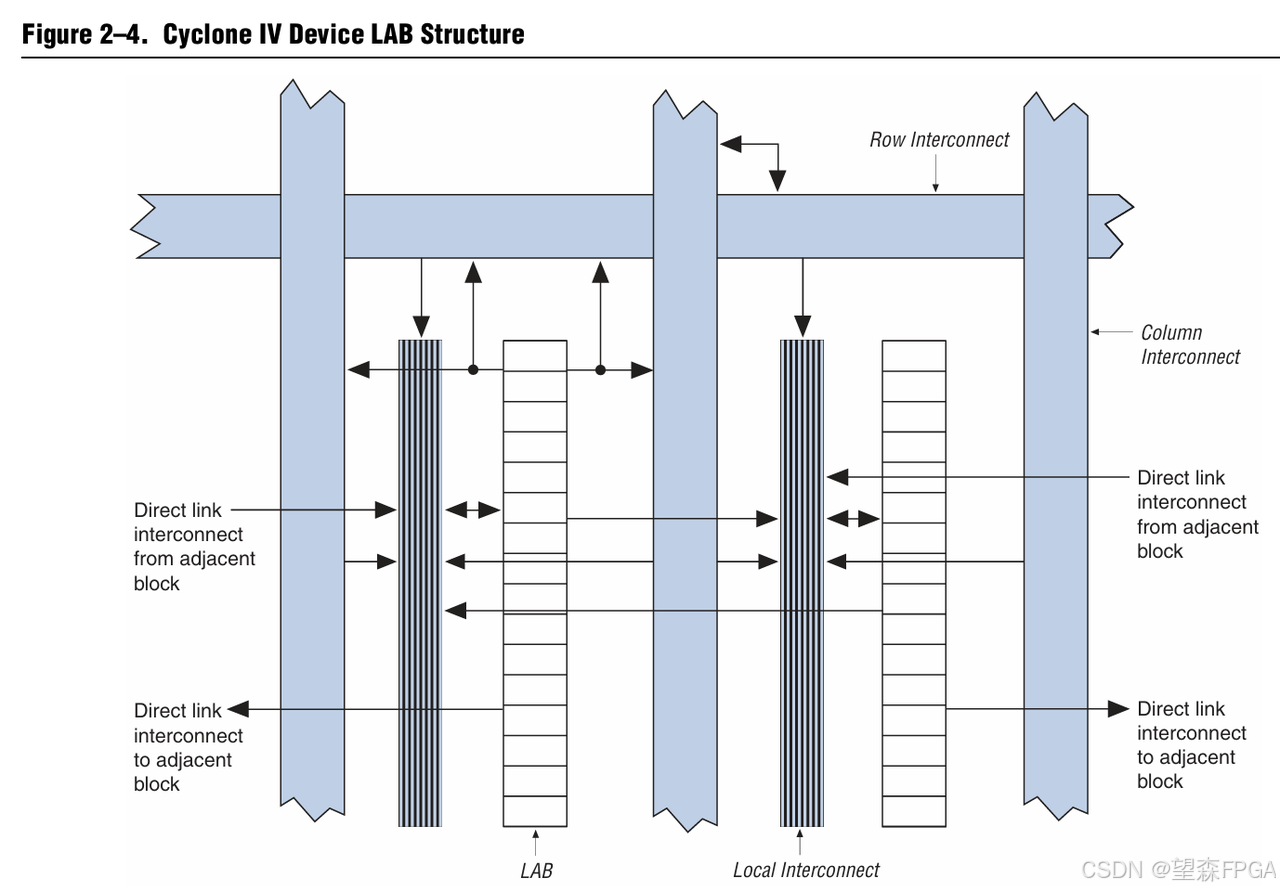

(2)LAB

Intel/Altera FPGA 中更大的逻辑功能单元叫 LAB(Logic Array Block,逻辑阵列模块),它是 Intel/Altera FPGA 最基本的构成块。

LAB 一般包含10个 LE ,LAB 之间通过可编程的布线资源连接,以实现复杂的数字电路。

(3)布线资源

布线资源负责将不同的 LE 和 LAB 互相连接。

布线资源提供了高度灵活的互联结构,允许信号在 FPGA 的不同部分自由传递。

布线资源有以下两种类型:

-

全局布线网络:用于连接远距离的逻辑单元和存储资源。

-

局部布线网络:用于连接相邻的 LAB,以实现低延迟的局部连接。

(4)存储资源

Altera FPGA 内部主要有两种存储资源:

-

分布式 RAM:将 LE 中的 LUT 配置为小型的分布式 RAM。用于小型或临时数据存储。

-

Block RAM(M9K 和 M20K):大容量的存储单元,用于实现 FIFO、缓冲区和数据缓存。

(5)时钟管理单元 (PLL, Phase-Locked Loop)

PLL(锁相环)负责产生时钟信号,并通过全局时钟树将时钟信号分发到 FPGA 的不同区域,保证低延迟和时钟信号的稳定性。

(6)I/O 引脚

I/O 引脚负责 Altera FPGA 与外部设备的通信,支持多种不同的通信标准和电压电平。

(7)专用硬件块

Altera FPGA 集成了一些 专用硬件块,用于加速特定任务。

常见模块包括:

-

DSP 模块:用于加速乘法、累加等数字信号处理任务。

-

硬核处理器:ARM Cortex-A 系列硬核处理器,形成了 FPGA + SoC(系统级芯片)的结构。这允许设计人员在一个 FPGA 内实现硬件加速和软件处理的协同设计。

-

PCIe 控制器:用于高速数据传输的 PCIe 硬核模块,能够大幅提高系统的通信带宽。

(8)配置逻辑

配置逻辑用于存储比特流文件,当 FPGA 上电或复位时,配置存储器会自动将比特流加载到 FPGA 中,设置 FPGA 的逻辑。

下图是 Intel/Altera CYCLONE IV FPGA LAB 的结构图:

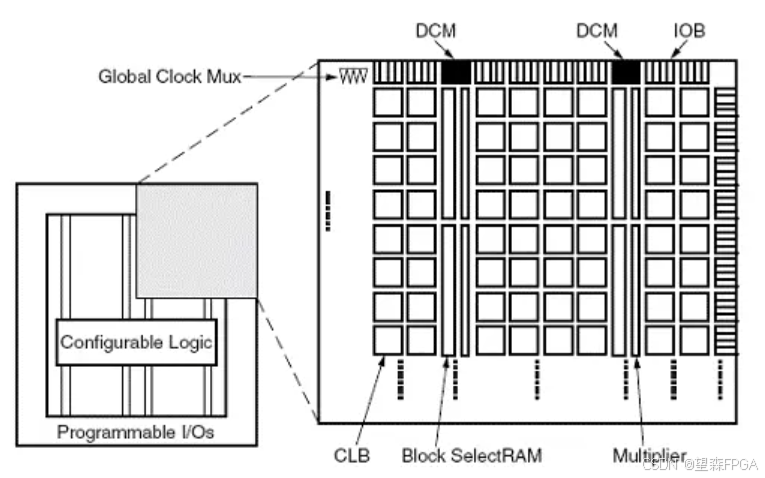

2.Xilinx FPGA

Xilinx FPGA 由可编程逻辑单元 CLB 、布线资源、可编程输入输出接口 I/O 、存储资源、数字时钟管理单元(Digital Clock Manager,DCM)、专用硬件块与配置逻辑等组成。

(1)Slice

Xlinx FPGA 的可编程单元叫 Slice ,它由4 个查找表 LUT(6 输入)、8 个寄存器 Flip-Flop 、进位链等组成。

Slice 有两种类型:

1.Slice-L(逻辑型 Slice)

这种类型的 Slice 主要用于实现一般的组合逻辑和时序逻辑功能。

2.Slice-M(存储型 Slice)

Slice-M 除了具备 Slice-L 的功能外,还可以配置为分布式 RAM 或 移位寄存器。

(2)CLB

Xilinx FPGA 中更大的逻辑功能单元叫 CLB (Config Logic Block,可编程逻辑块),是 Xilinx FPGA 最基本的构成块,它由多个 Slice 组成。

Xlinx FPGA 的其余组成结构大致与 Intel/Altera FPGA 相似,便不再赘述。

下图是 Xilinx FPGA 的内部结构图:

2 FPGA基本单元

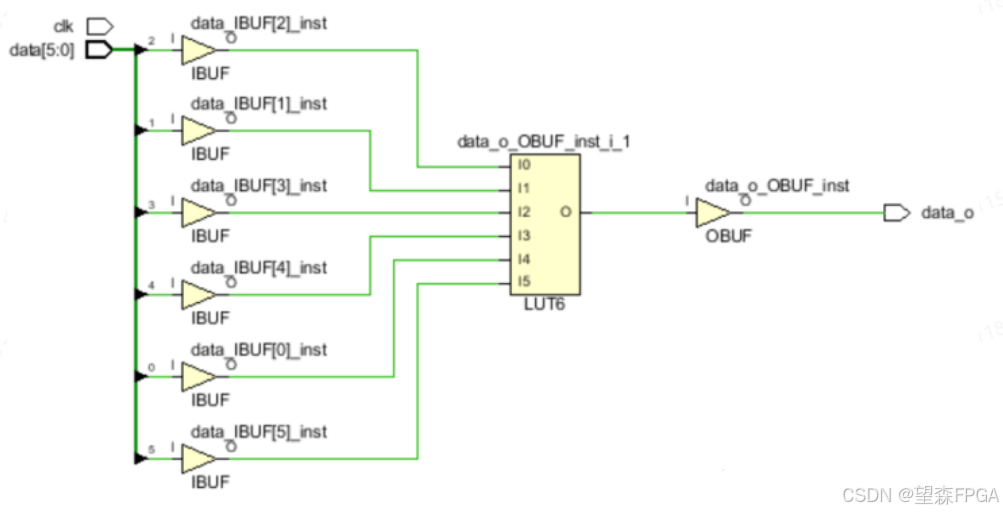

(1)LUT(Look-up table,查找表)

FPGA 使用 LUT 代替逻辑门电路。

LUT 的作用类似于一个小型的SRAM(静态随机存取存储器),通过查表的方式实现任意逻辑函数。

以逻辑表达式“data_o = data[0] & data[1] & data[2] & data[3] & data[4] & data[5]”为例,写为 HDL 代码综合后的结果是一个 LUT6。

(2)进位链(半加器、全加器、多位加法器)

1.半加器

由两个1比特数据(A、B)相加,输出一个1比特结果位(S)和进位(C)的加法器为半加器。

2.全加器

由两个1比特数据(A、B)和一个1比特低位进位(Cin)相加,输出一个1比特结果位(S)和进位(Cout)的加法器为全加器。

3.多位加法器

由半加器或低位进位为0的全加器作为最低位,与全加器级联即可构成多位加法器。

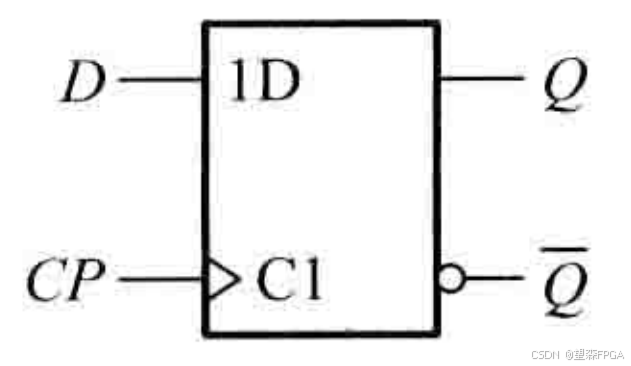

(3)触发器、锁存器

1.触发器 flip-flop

由时钟边沿作为触发条件,将输入送到输出的记忆单元。

一个触发器能存储一位二进制数据。

一个触发器可以组成一个1位寄存器 register;

多个触发器可以组成一个多位寄存器。

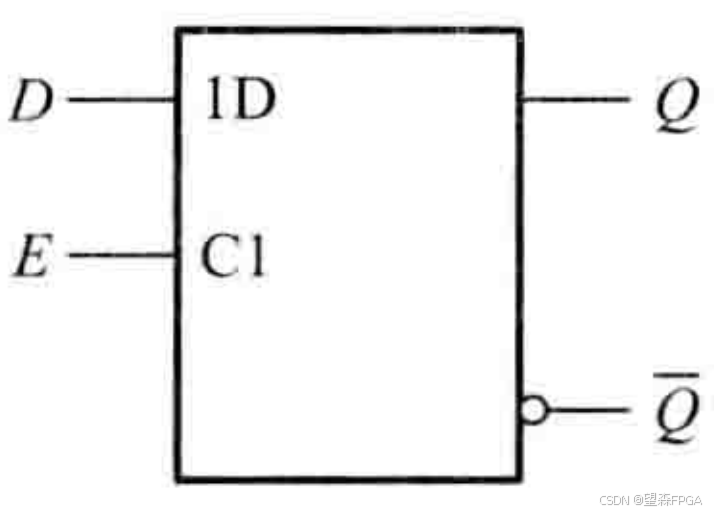

2.锁存器 latch / 闩锁

由电平的改变作为触发条件,将输入送到输出的电路单元。

注意:

-

锁存器不需要时钟,因此也不是时序元件。

-

锁存器对毛刺非常敏感,容易影响电路逻辑,设计中尽量避免使用。

-

为了在设计中不产生锁存器,组合逻辑中的判断语句必须完整(比如,if 语句必须有 else,case 语句必须有 default),而时序逻辑不用考虑该问题。

- END -

相关推荐文章,点击跳转:

1127

1127

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?