本文章继续接着《Altium Designer 入门基础教程(七)》的内容往下介绍:

N. 原理图的修改同步到PCB

有时,在画板布局布线的过程中,可能由于客户原因突然要求我们临时要更改原理图啥的,这时我们就要先修改原理图然后再同步更新到PCB中。

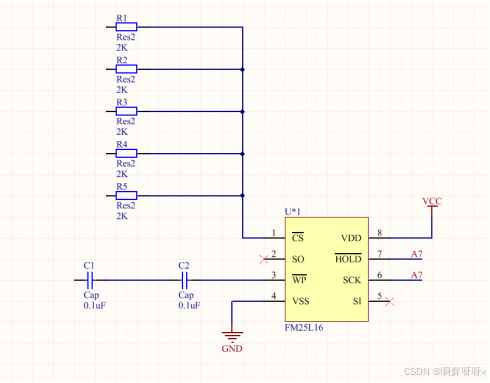

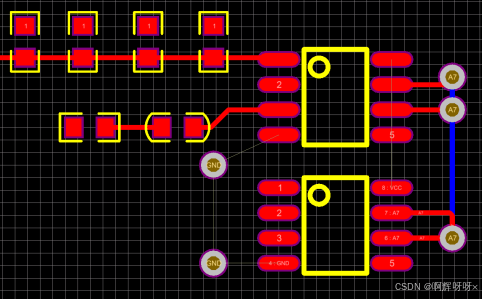

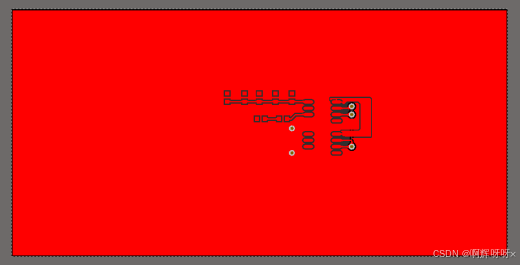

原来的原理图:

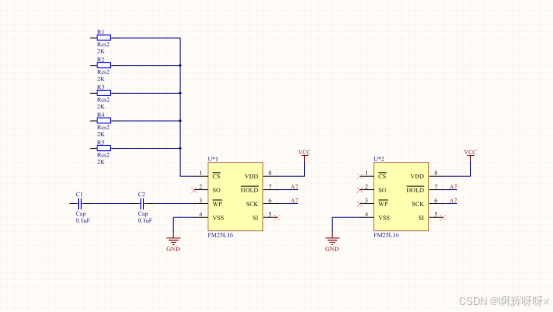

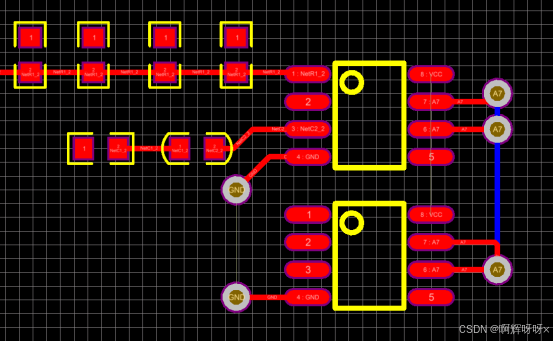

假如下图是我们更新后的原理图(随便添加的):

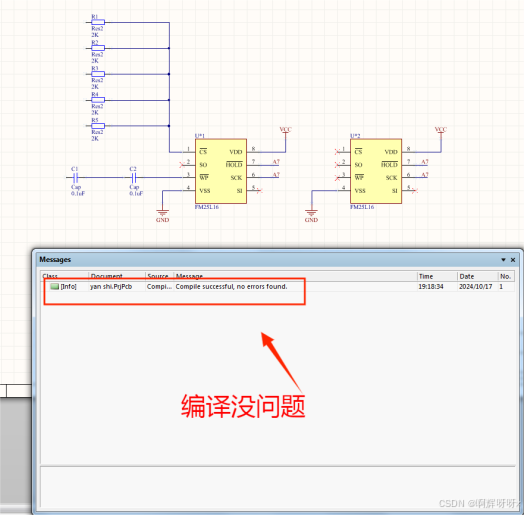

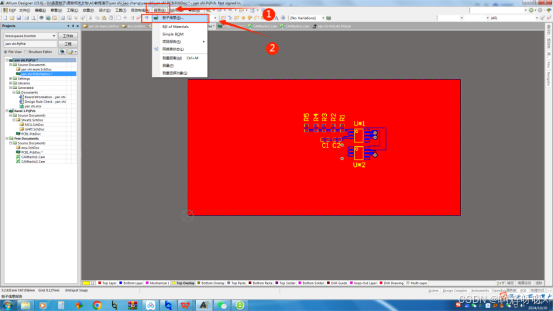

同样的,更新完成之后,我们也要对原理图进行编译。工程》Compile Document 原理图名称》System》Messages》查看是否有错误,没问题之后再同步更新到PCB 中。

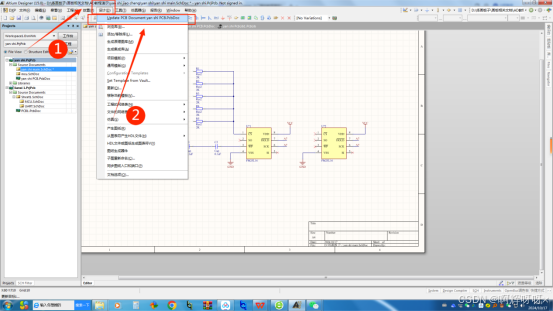

设计》Update PCB Document,同步更新到PCB中。

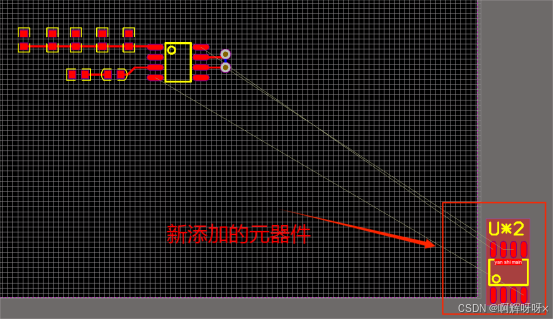

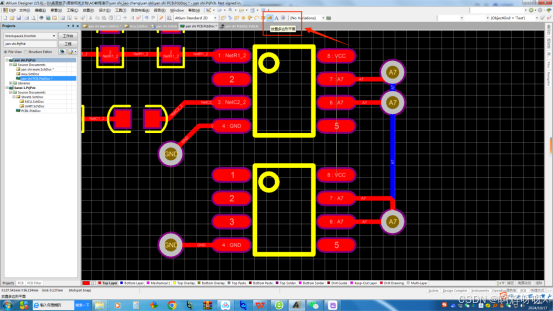

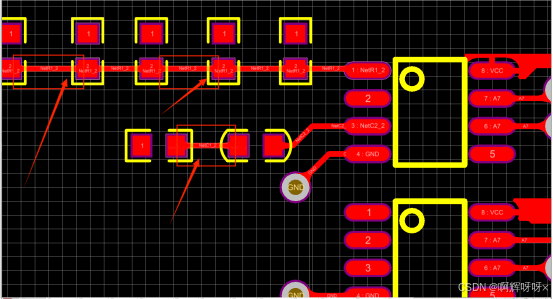

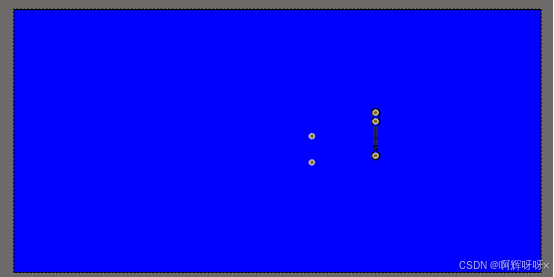

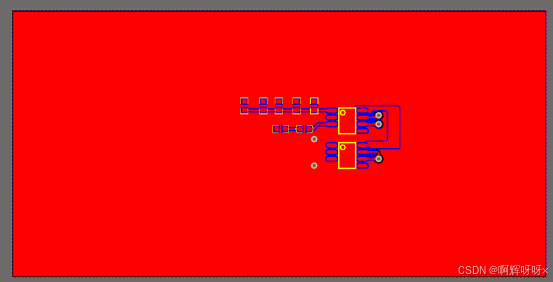

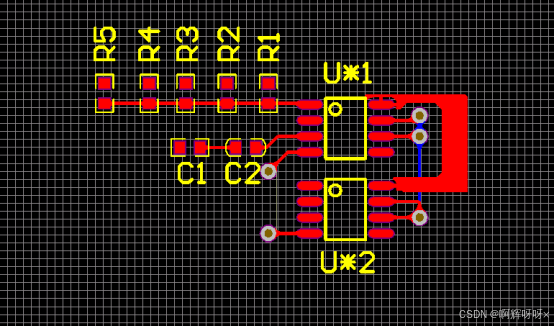

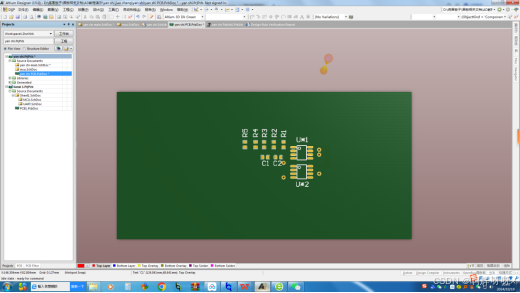

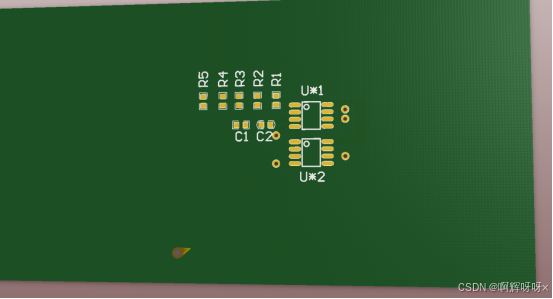

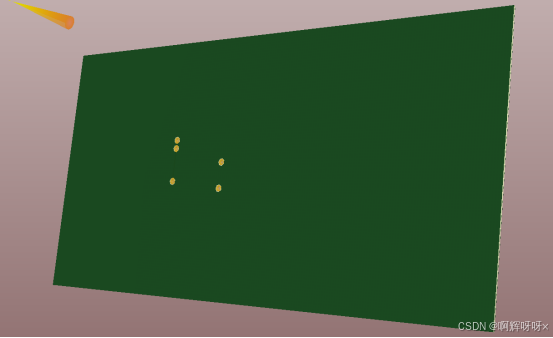

新添加的元器件就会同步到PCB中

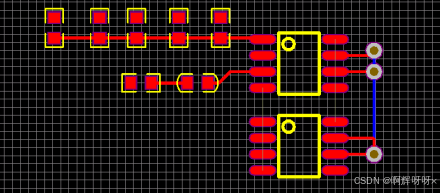

之后,我们调整好元器件。正常布局布线即可。

O.GND的处理、铺铜、泪滴的生成与覆铜

1.GND的处理

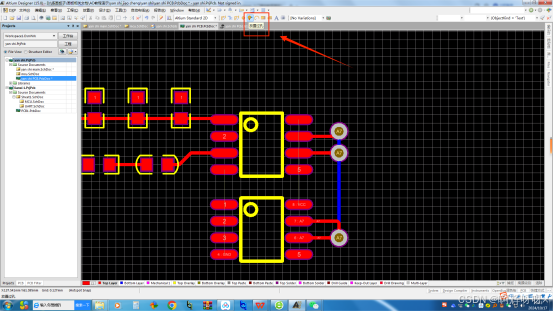

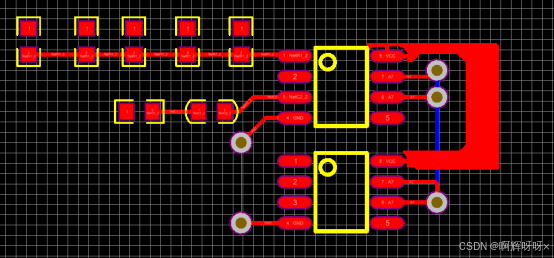

正常情况下,地GND我们一般引线出来打过孔即可,后面铜箔覆铜把整个板子的GND连接起来。

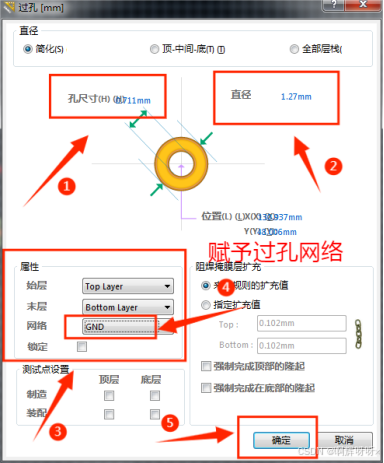

首先,放置过孔

过孔附着在鼠标的时候,按Tab键进入编辑过孔

之后单击鼠标左键放置过孔即可

焊盘与过孔连线

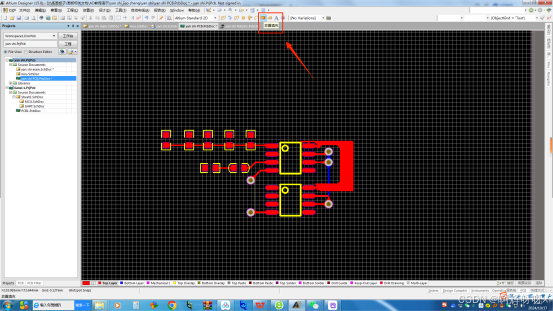

2. 铺铜(有时用填充也可以)

布局布线中有些要过相对大一点电流的地方,我们就不考虑用粗走线来画了,一般考虑用铺铜来代替走线。

放置多边形平面,我们给VCC铺铜

画出铺铜形状即可。

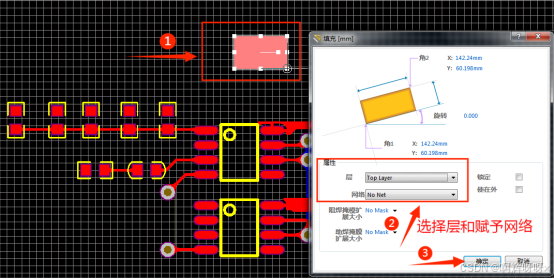

填充

拖动鼠标拉出填充的矩形,按Tab键进去编辑。

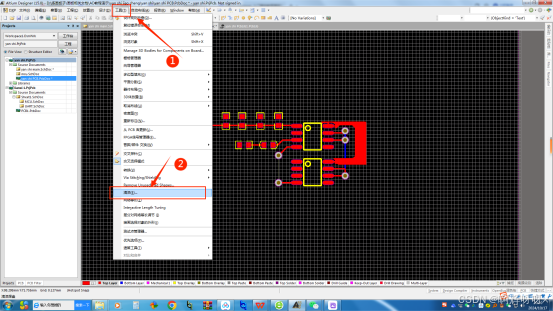

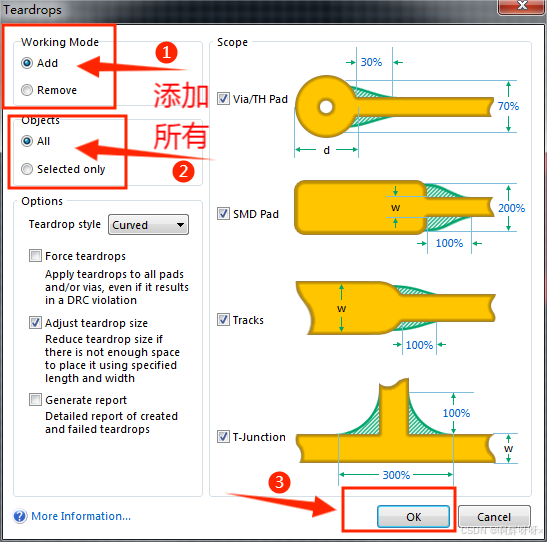

3. 泪滴的生成

工具》泪滴

整个板子所有的连线便自动生成泪滴,类似下图所示。

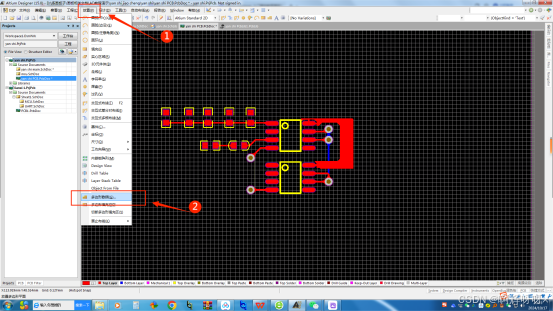

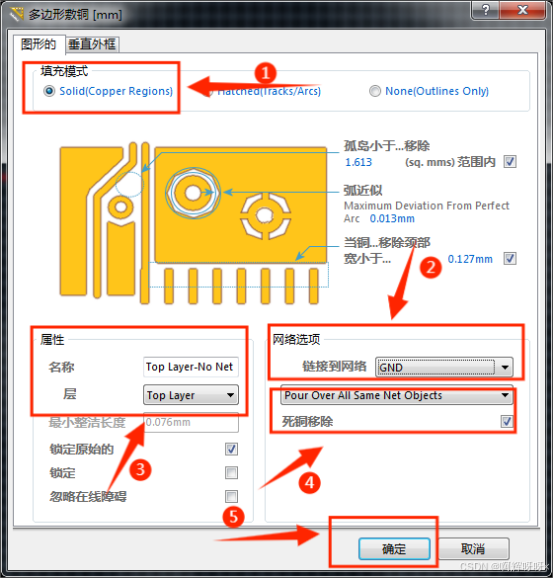

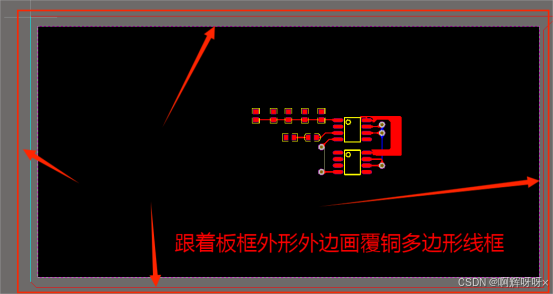

4.覆铜(快捷键PG)

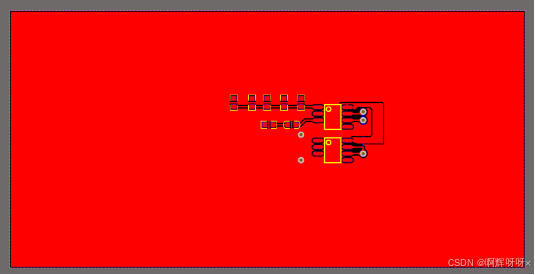

顶层覆铜(覆铜GND)

顶层完成覆铜

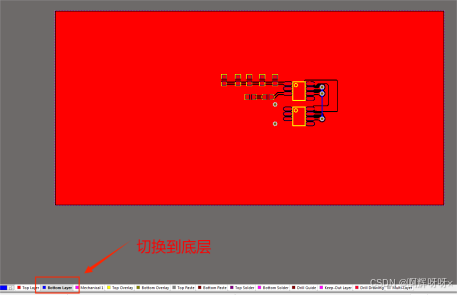

同理,底层也同样覆GND的铜

底层完成覆铜

若要删除覆铜,切换到相应的层,选中覆铜,直接Delete删除即可

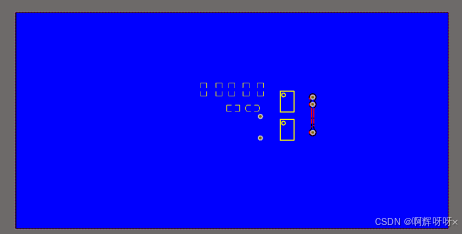

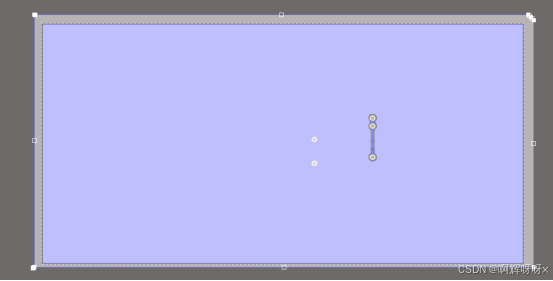

单层显示,想要单层显示哪层,就切换到哪层,快捷键shift+S即可单层显示该层。单层显示顶层:

单层显示底层:

再按一次shift+S即可恢复全部层显示

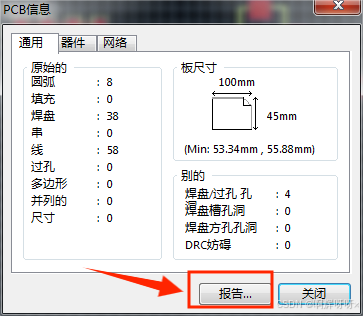

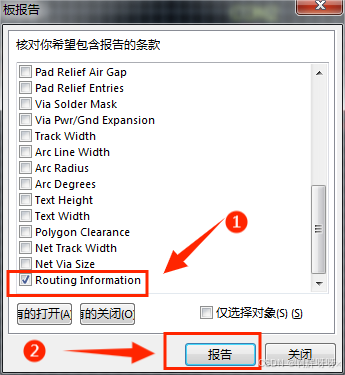

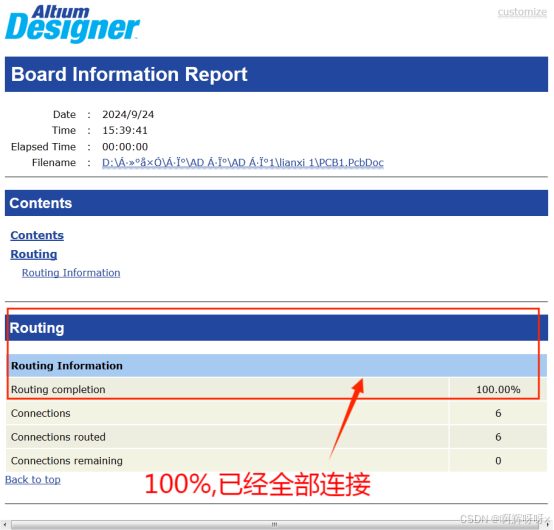

P.布线完整性检查(连接性检查)

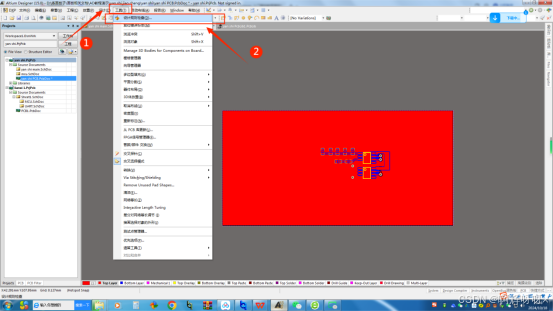

Q.设计规则检查(DRC)

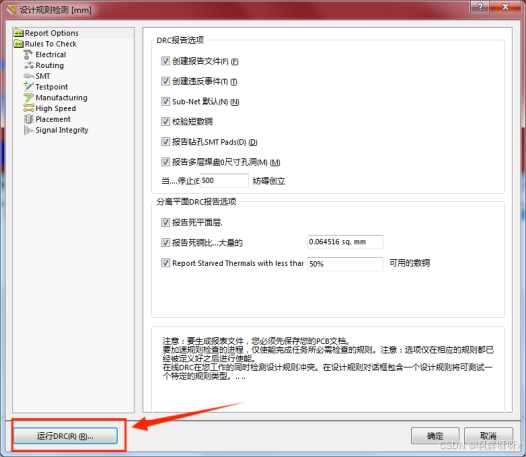

布局布线覆铜等相关步骤都完成后,接下来就是对整个板子进行设计规则检查。所谓的设计规则检查,简单来说就是对我们画好的板子,看符不符合我们布局之前所设定的规则。工具》设计规则检查

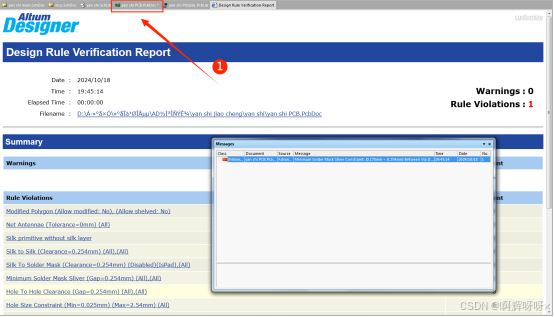

之后会弹出一个检查设计规则检查报告

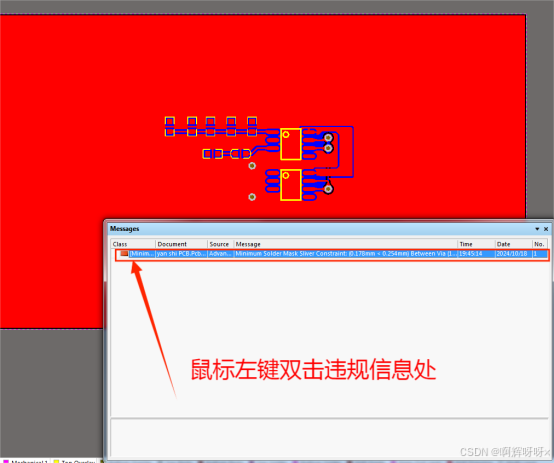

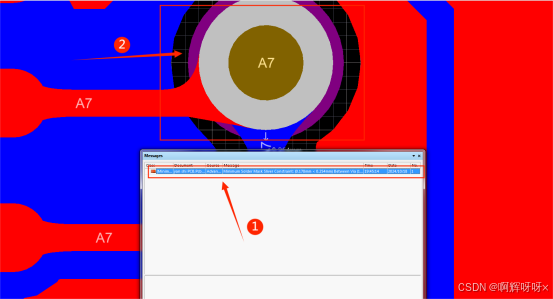

我们调出Messages窗口,然后点击PCB界面,双击Messages窗口中的违规信息,即可在PCB界面跳转到相应的违规点位,然后我们根据实际情况去修改直到DRC没问题即可。

之后界面直接跳转到有违规的问题点位处,我们根据提示做相应的修改即可。

R.元器件丝印和属性的调整及板子3D效果预览

1.元器件丝印和属性的调整

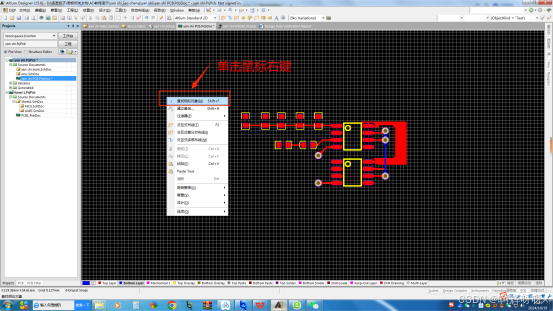

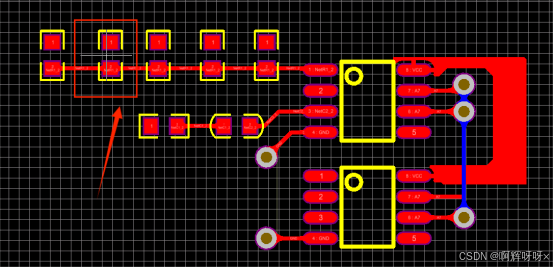

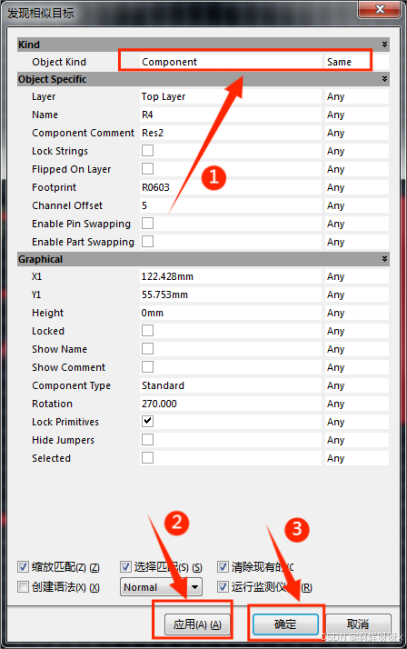

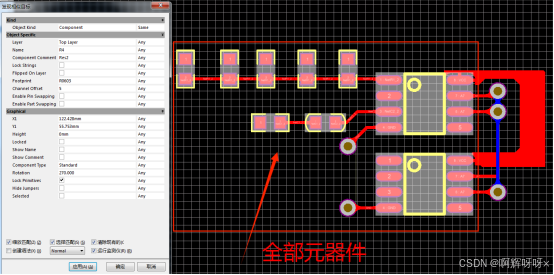

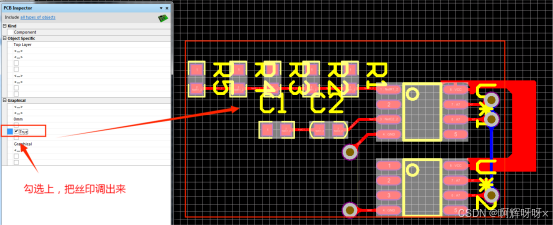

若DRC检查没问题之后,接下来我们对板子元器件的丝印进行调整。把之前我们隐藏掉的丝印调出来先。回到PCB界面,单击鼠标右键》查找相似对象》出现十字光标后,任意单击一个元器件》弹出过滤器(component(same))》应用,确定筛选出全部元器件》调出 PCB Inspector窗口》显示丝印即可。

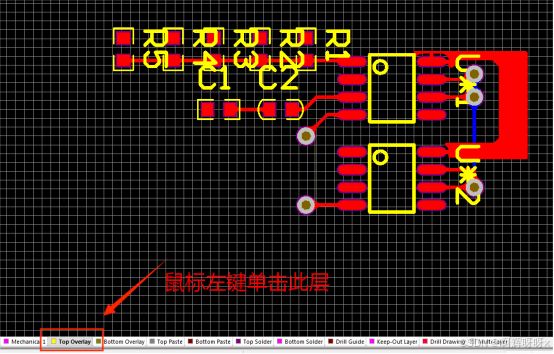

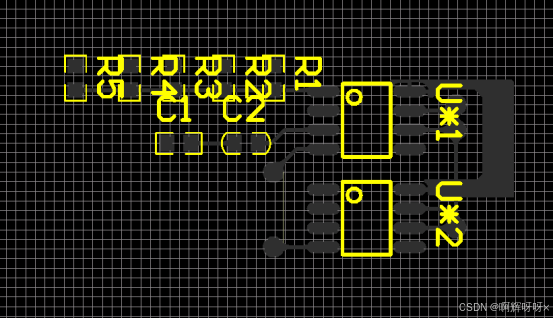

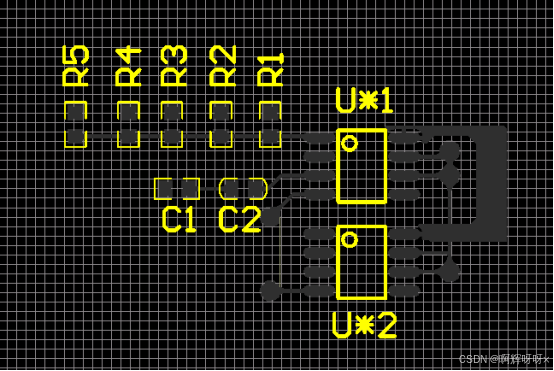

然后选中丝印层(TOP Overlay),单层显示快捷键shift+S,单层显示丝印层,对丝印进行调整即可。

快捷键shift+S单层显示对丝印进行调整(调整过程中长按鼠标左键选中位号进行移动,空格键对位号进行旋转,前面介绍的对齐方式也同样适用)

再次shift+S,整板全部显示回来。

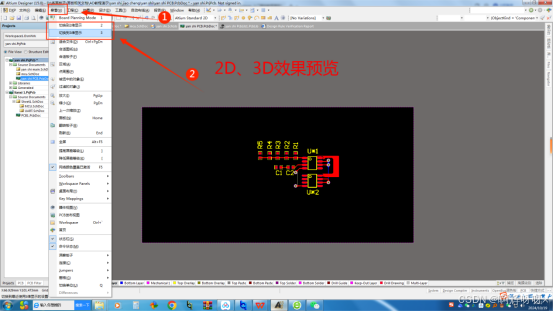

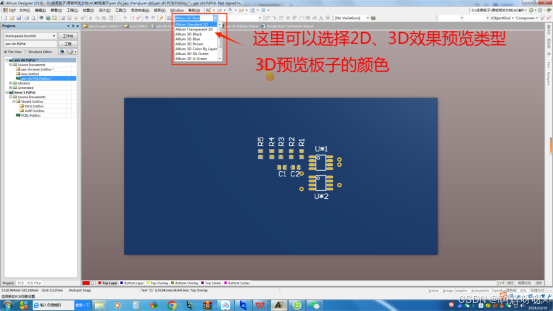

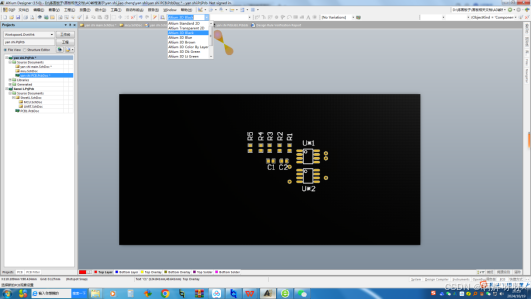

2.板子3D效果预览

3D效果预览快捷键:3 2D效果预览快捷键:2

3D预览效果下,按住鼠标滚轮往上拖动可以放大界面,往下拖动可以缩小界面。

放大:

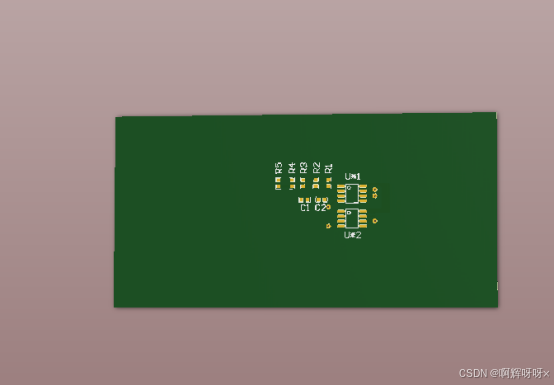

缩小:

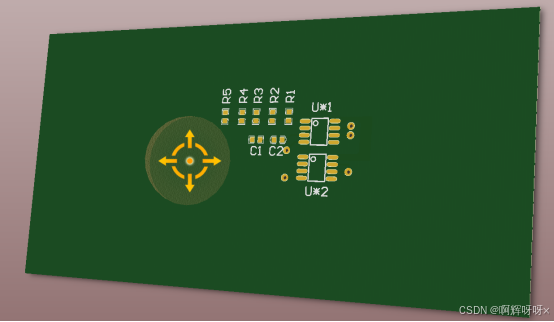

按住shift+鼠标右键可以对板子进行拖动旋转

VB对整个板子翻转:

至此,AD软件中原理图的修改同步到PCB、GND的处理、铺铜、泪滴的生成与覆铜、布线完整性检查(连接性检查)、设计规则检查(DRC)、元器件丝印和属性的调整及板子3D效果预览的相关内容已介绍完成。

此博客是利用空闲时间每天编辑一点断断续续编辑出来的,由于个人空闲时间有限,所以此博客暂时先编辑到此。后续会利用空闲时间整理更新好《Altium Designer 入门基础教程(九)》发到此博客号,喜欢本系列课程的朋友们可以点点关注和订阅以便更新教程可以第一时间阅读到,先睹为快!谢谢大家!

7475

7475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?