要从PL端引出20MHz的差分时钟信号,接到DDS9954的OSC时钟引脚

要从PL端引出20MHz的差分时钟信号,接到DDS9954的OSC时钟引脚

一、创建vivado工程

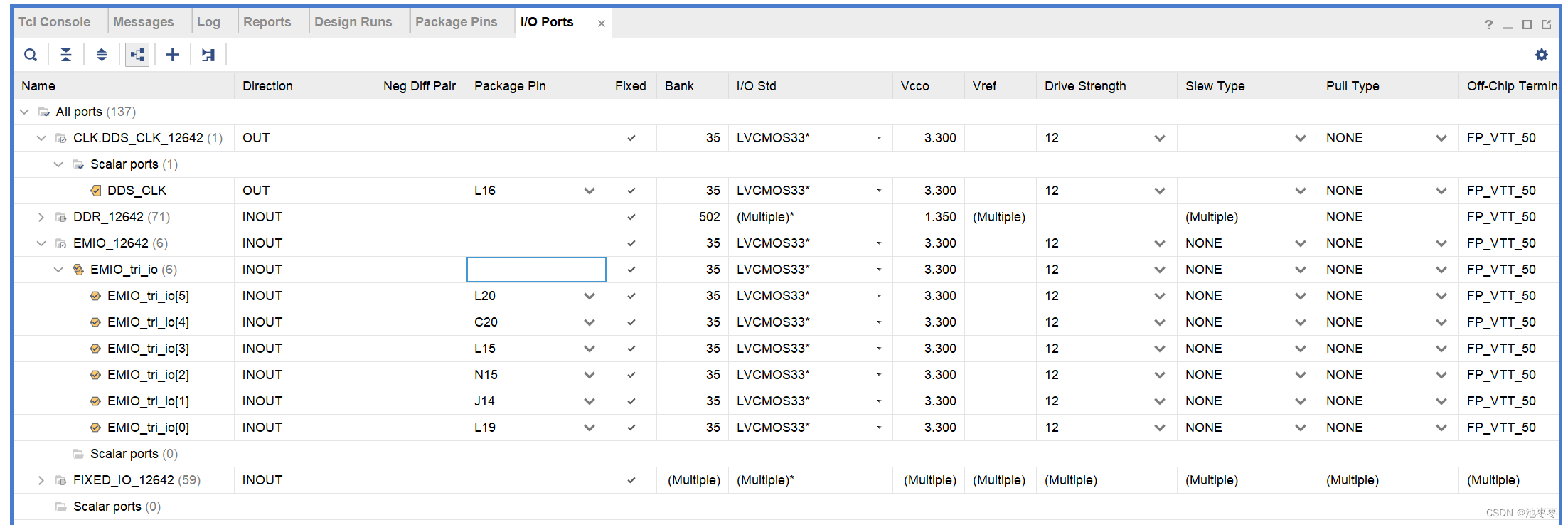

设置6个EMIO引脚,添加UART,添加clocking wizard模块和reset模块

生成OUTPUT文件,和HDL文件;

然后做管脚约束,我把DDS_CLK约束到L16引脚。然后生成比特流

报错:

然后我重新生成了一次OUTPUT文件,再生成一次bitstream,竟然好了.

看到有人说时钟不能引到普通的引脚上,但是应该是对输入来讲,我的操作是把时钟引出去,按理来说应该没问题。

后续没有错误了,就暂时忽略这个问题了。

离谱问题+1

二、产生差分时钟

输出采用OBUFDS原语可以产生差分的时钟信号

在system wrapper文件里面添加下面的一段

要把DDS_CLK分成DDS_CLK_p 和DDS_CLK_n。

三、D触发器方法

由于电路板当中,将时钟信号连接到了BANK35的引脚上,所以他的电平是3.3V。但是OBUFDS原语只支持2.5V差分电平标准,但是DDS时钟对应的FPGA BANK是3.3V的。

所以修改一下,让DDS_CLK的时钟频率变成40MHz,然后通过设置两个D触发器,一个初值是0,一个初值是1,就可以产生两路差分信号

要在在system wrapper文件里面添加下面的一段。

reg dds_clk_p;

reg dds_clk_n;

always @ (posedge DDS_CLK) begin

dds_clk_p <= ~dds_clk_p;

dds_clk_n <= ~dds_clk_n;

if(DDS_RST) begin

dds_clk_p <= 1'b1;

dds_clk_n <= 1'b0;

end

end

assign DDS_CLK_p = dds_clk_p;

assign DDS_CLK_n = dds_clk_n;(在修改system wrapper文件的时候,还更改了一些线,我现在还不太清楚这个文件里面的wire input output等等的作用,后续要弄清楚)

最后产生了正确的时钟波形。

1997

1997

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?