1.GPIO的功能作用

GPIO俗称IO端口,可以连接外部设备,通过输入输出电平来控制设备。

这里我们需要了解一个概念,电平,通常称1为高电平,0为低电平,当电平不一样时会产生电压,这是时候外部设备就通电工作了。

还有一种是高阻态,既不是高电平也不是低电平,对电路毫无影响。

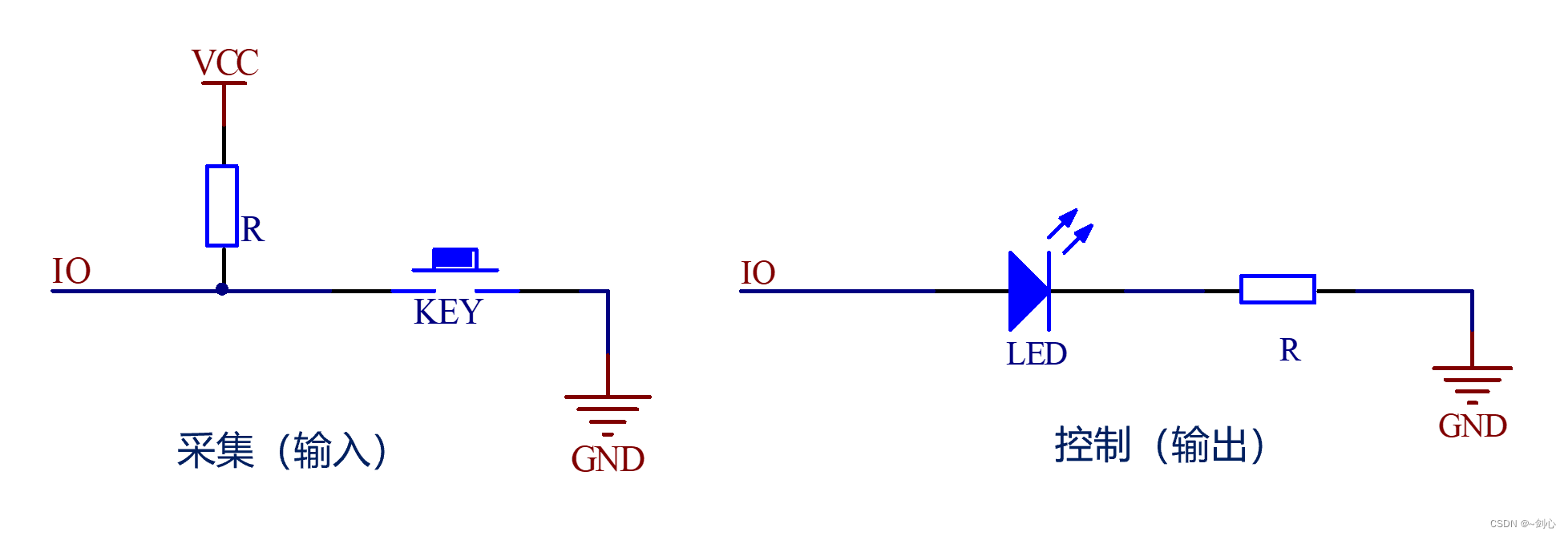

vcc:电源 key:按键 GND:接地电平为0

- 第一个图是输入设备,当我们按下key按键的时候,此时电路接通,vcc输出高电平1,GND是低电平0,此时产生电压差。

- 第二个图也是一样工作原理,如果输出为高电平则 LED点亮,如果输入为低电平则LED不能点亮。

这是IO大致的功能,接下来我们可以看看IO口内部大致的样子

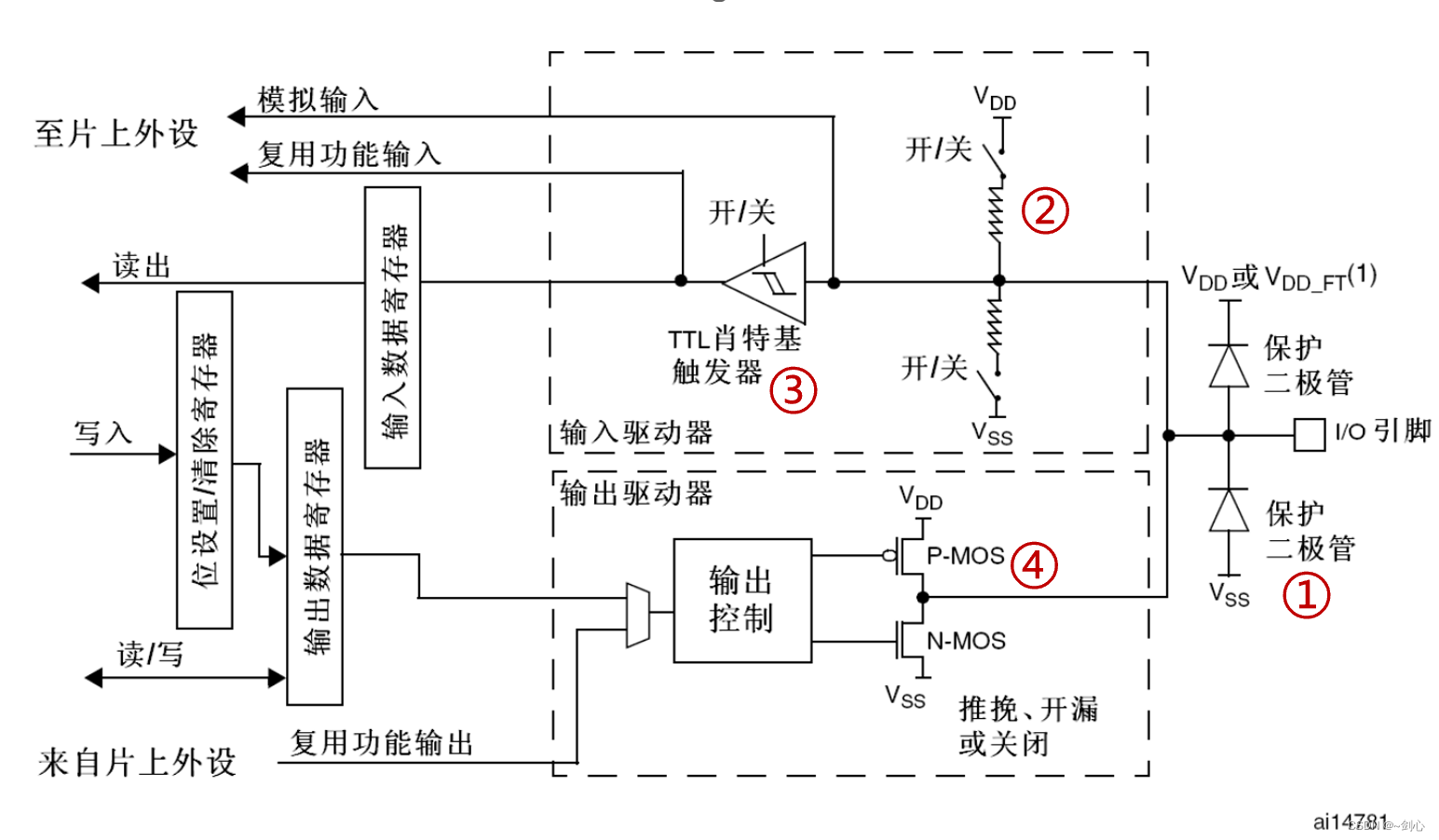

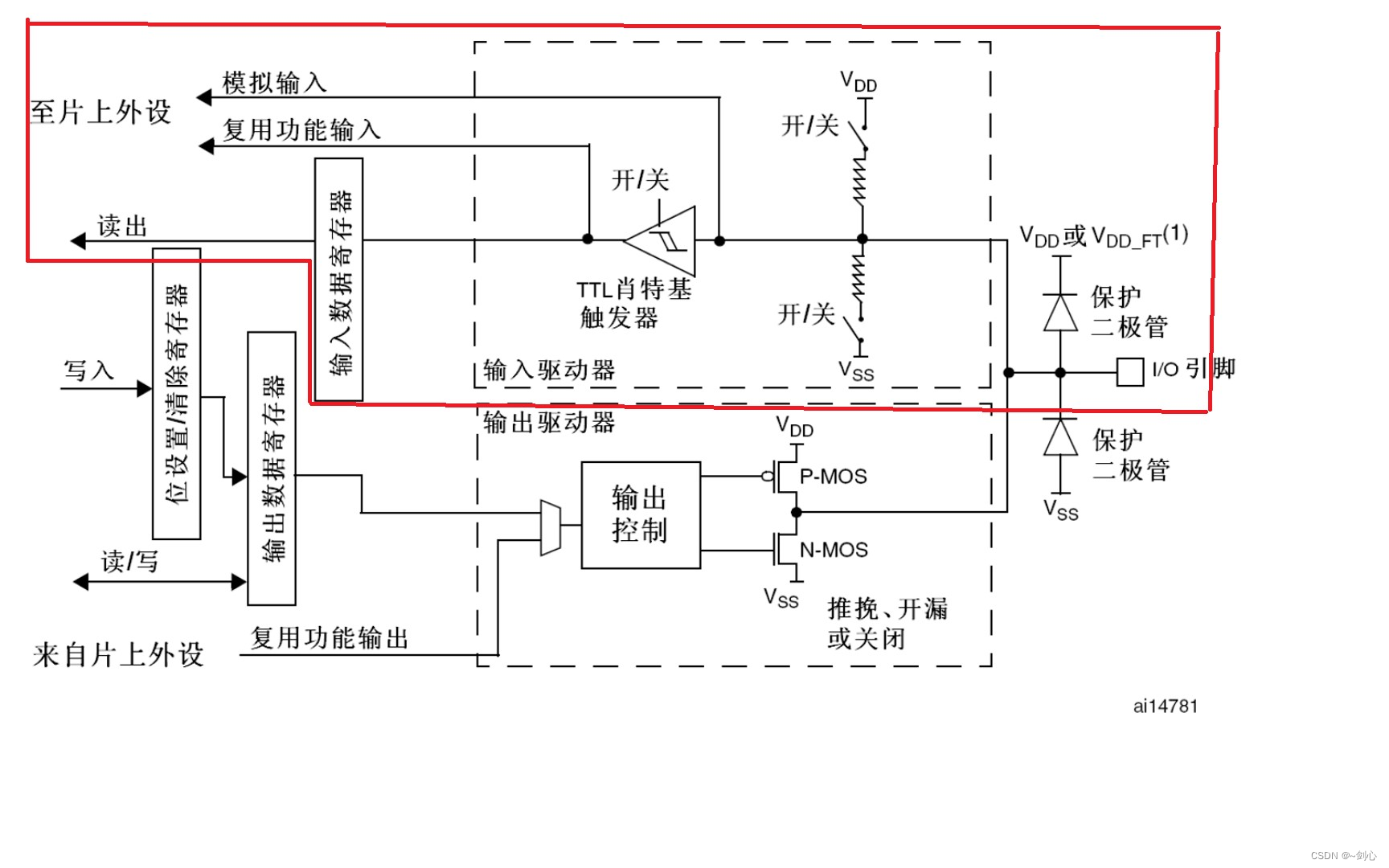

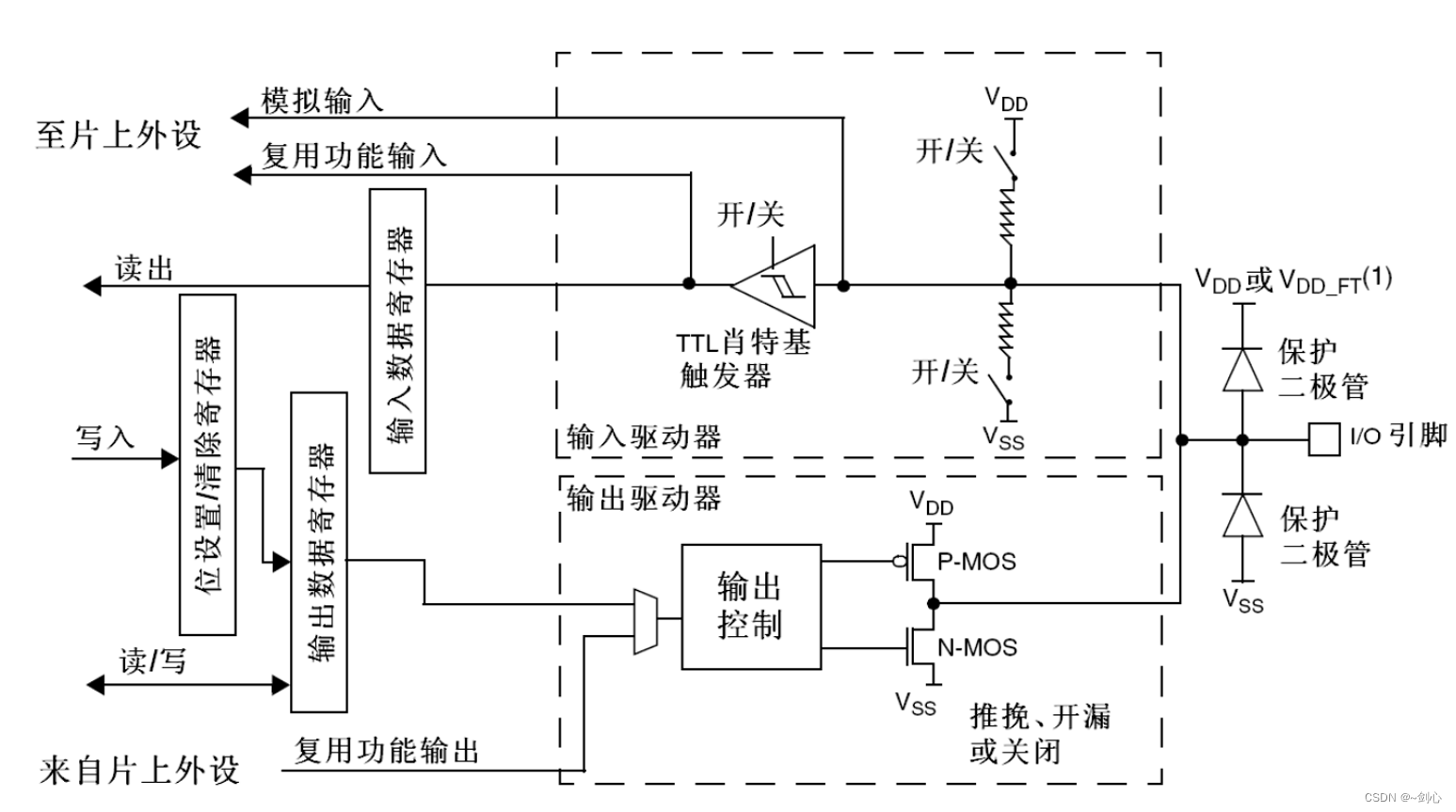

2.IO端口内部结构

保护二级管:保护电路。上.下拉电阻:上拉电阻把高阻态转化为高电平1,下拉电阻把高阻态转化为低电平0。施密特触发器:把波形电压转化为1或0。n-mos输出0,p-mos输出1。

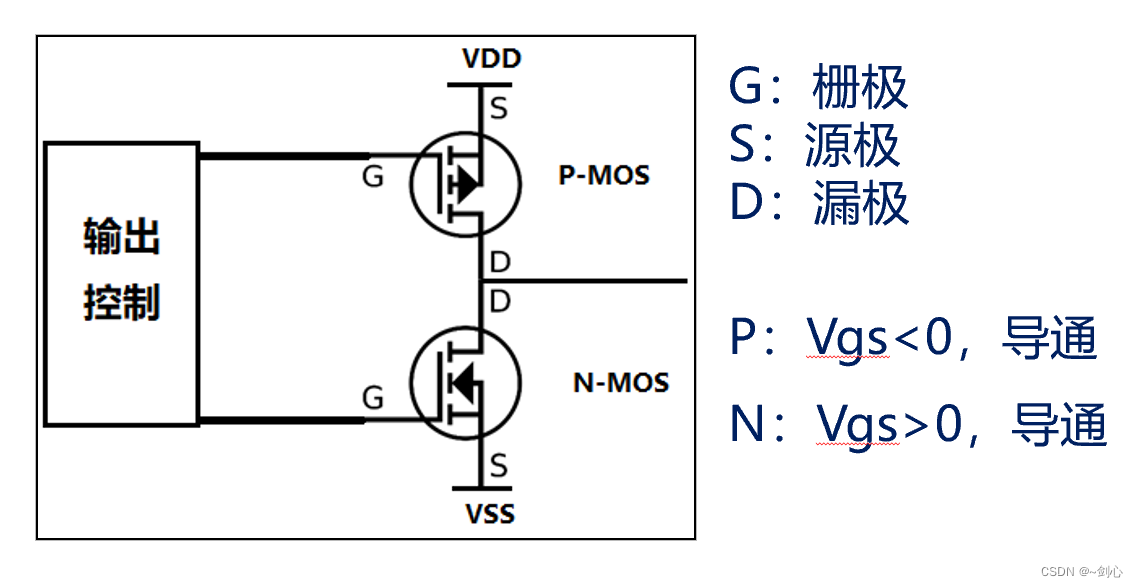

下面让我们看一看mos具体应用

在G的位置可以输出低电平或高电平。

P-MOS处电平为1,在G处通入0则导通,N-MOS管相反。

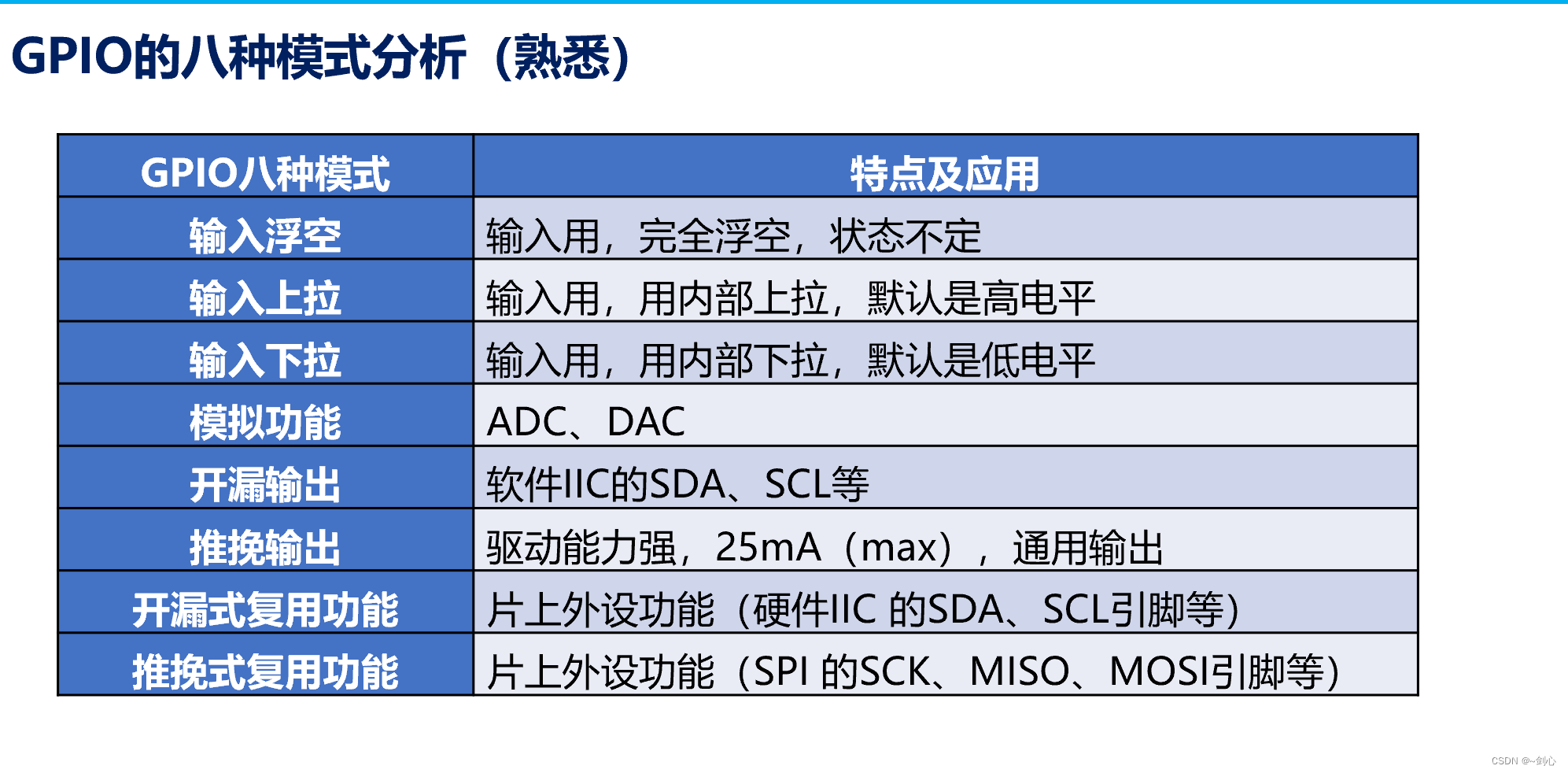

3.GPIO的八种模式分析

这八种模式中,前四个只有输入没有输出,后四个既有输入也有输出。

现在就来看看前四个输入模式

-

输入浮空的工作路径:引脚——施密特触发器——输入数据寄存器(IDR)——CPU

解析:这个工作模式是在引脚处输入1或0,通过寄存器输入cpu,所以这个模式电平是由外部设备决定的。 -

输入上拉(输入下拉)的工作路径有两个:

模式一.(输入1或0)引脚——施密特触发器——输入数据寄存器(IDR)——CPU

模式二.(输入高阻态)VDD(VSS)开关——施密特触发器——输入数据寄存器(IDR)——CPU

解析:在引脚处输入1或0时,此时cpu可以接受到电平,但是一但输入高阻态,那么处于不确定模式则会直接通过VDD(VSS)输入高低电平

VDD 高电平

VCC 低电平 -

模拟输入的工作路径:引脚——模拟输入——至片上外设。

解析:这是直接输出到外部设备(DAC)或(ADC)。

后面四种模式输入都是:引脚——施密特触发器——输入数据寄存器(IDR)——CPU -

开漏输出:通过输出数据寄存器(ODR)输出。

开漏复用输出:通过复用功能,由外部设备输出。

然后都是通过输出控制——N-MOS——引脚

解析:由于N-MOS只能输出低电平,如果输出高电平需要在外部加入下拉电阻 -

推挽输出:通过输出数据寄存器(ODR)输出。

推挽式复用输出:通过复用功能,由外部设备输出。

然后都是通过输出控制——N-MOS(P-MOS)——引脚

解析:此时由于两个MOS都能使用,可以自由输出高低电平大概了解完GPIO工作模式后,那么如何设置工作模式呢?

这时候就靠操作寄存器来控制工作模式了。

在下一个文章我会详细说明如何操作寄存器来控制该工作模式。

2238

2238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?