IP核基本概念

IP核,即知识产权核(Intellectual Property core),是一种预先设计好的、经过验证的、可重复使用的电路功能模块,它通常以硬件描述语言(HDL)的形式存在,有时也以原理图的形式出现。这些模块可以被集成到更大的数字电路或系统中,从而加快系统的设计和验证过程,同时减少错误和提高可靠性。

在FPGA开发中,IP核扮演着至关重要的角色。FPGA是一种可以通过编程来改变其内部连接和功能的集成电路,因此它非常适合实现复杂的数字逻辑。然而,随着设计复杂度的增加,从零开始设计和验证所有必要的功能模块变得越来越耗时且容易出错。这就是IP核发挥作用的地方。

IP核可以分为三种类型:软核、固核和硬核。

软核:软核是指以硬件描述语言(如VHDL或Verilog)编写的代码,它可以被综合成FPGA中的逻辑元素。软核具有很高的灵活性,可以根据需要进行修改和优化,但它们占用的资源较多,性能相对较低。

固核:固核是介于软核和硬核之间的一种形式,它通常包含一部分已经映射到特定工艺的物理版图,但可能还包含一些需要通过综合工具映射的部分。固核的性能和资源占用介于软核和硬核之间。

硬核:硬核是完全针对特定工艺节点定制的物理版图,它直接作为物理模块嵌入到FPGA芯片中,无法更改。硬核通常提供最高的性能和最低的功耗,但缺乏灵活性。

使用IP核的主要优势在于它可以大大缩短产品上市时间,因为设计师可以利用已有的、经过验证的模块,而不是从头开始设计。此外,IP核还可以提高设计的可靠性和一致性,因为它们经过了广泛的测试和验证。

IP核为什么是FPGA开发的必修课

IP核在FPGA开发中被视为必修课,主要是因为它以下几个方面的优势:

加速设计流程:

IP核是经过预先设计和验证的模块,可以直接集成到FPGA设计中。这大大减少了从零开始设计和验证所需的时间,加快了产品上市的速度。

1,提高设计质量:

IP核通常由专业的团队开发和测试,因此在质量和可靠性方面有较高的保障。使用IP核可以减少设计中可能出现的错误,提高最终产品的稳定性。

2,降低开发风险:

由于IP核已经过广泛测试,使用它们可以降低设计失败的风险。这对于复杂和高要求的项目尤为重要。

3,节约资源:

IP核允许设计师专注于系统的其他关键部分,而不是花费大量时间在通用功能的开发上。这样可以更有效地利用开发资源。

4,标准化和复用:

IP核提供了一个标准化的解决方案,可以在不同的项目和设计中重复使用。这不仅提高了效率,还有助于保持设计的一致性。

5,易于学习和使用:IP核通常配有详细的文档和示例,使得即使是初学者也能够相对容易地学习和使用它们。适应性强:许多IP核都提供了一定程度的可配置性,允许设计师根据特定需求调整参数,使设计更加灵活。

6,支持复杂功能:IP核可以支持非常复杂的功能,如高速接口、处理器核、加密算法等,这些功能如果自行开发将会非常困难和耗时。

IP核的选择和使用

在FPGA开发中,选择和使用IP核是一个重要的环节,它涉及到项目的性能、成本和开发时间等多个方面。

选择IP 核:

1,确定需求:首先明确你的项目需要实现什么功能,这将帮助你确定需要哪种类型的IP核。例如,如果你需要一个高速数据传输接口,你可能会选择一个PCIE接口的IP核。

2,评估性能:根据项目的性能要求选择合适的IP核。不同的IP核可能在速度、功耗和处理能力上有所不同。

,3,考虑兼容性:确保所选IP核与你的FPGA型号兼容,并且支持你的开发环境和工具链。

4,检查许可证:某些IP核可能需要购买许可证才能使用,这可能会影响项目的成本。

5,阅读文档:仔细阅读IP核的文档,了解其使用方法、配置选项和限制。

6,评估支持和更新:选择那些有良好技术支持的IP核,并且定期检查是否有更新,以确保你的设计能够利用最新的功能和改进。

使用IP核

1,导入IP核:在你的FPGA设计环境中导入所选的IP核。这通常涉及到从IP核库中选择并添加到你的项目中。

2,配置IP核:根据你的需求配置IP核的参数。这可能包括设置时钟频率、数据宽度、缓冲区大小等。

3,集成到设计中:将IP核与其他设计模块连接起来,确保所有的信号正确对接。

4,仿真和验证:在设计中加入IP核后,进行仿真和验证以确保其行为符合预期。

5,综合和布局布线:将整个设计综合到FPGA上,并进行布局布线。这个过程可能会受到IP核的影响,因为它会占用FPGA的资源。,6,调试和优化:在实际硬件上进行测试,并根据测试结果对设计进行调整和优化。

6,文档和维护:记录IP核的使用情况和任何特殊配置,以便于未来的维护和升级。

在整个过程中,重要的是要保持设计的模块化,这样可以更容易地替换或升级IP核,而不会对整个设计造成太大的影响。此外,随着经验的积累,你将更好地了解哪些IP核最适合你的特定需求,并能更高效地将它们集成到你的设计中。

简单IP核调用实例

以下操作基于vivado软件(其他软件基本原理都差不多)

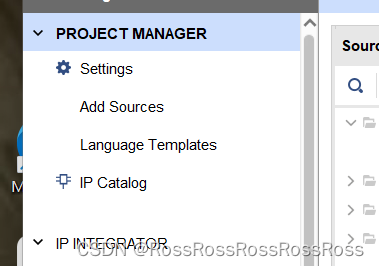

首先我们找到左侧的IP catalog (IP核目录),点击打开它。

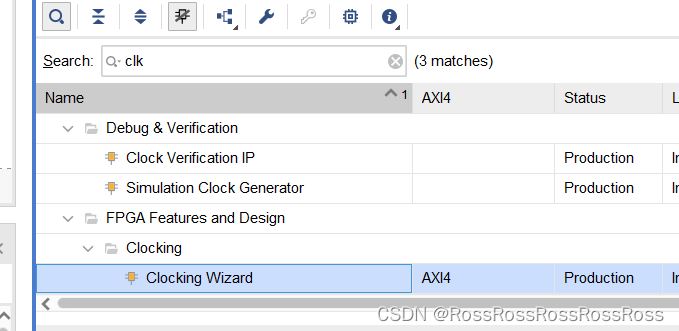

然后在右侧搜索你想用的IP核,比如我搜索clk,然后打开clocking项目

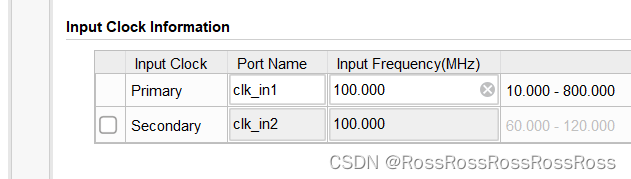

然后根据开发板进行时钟配置

之后在output clocks中设置配置

...

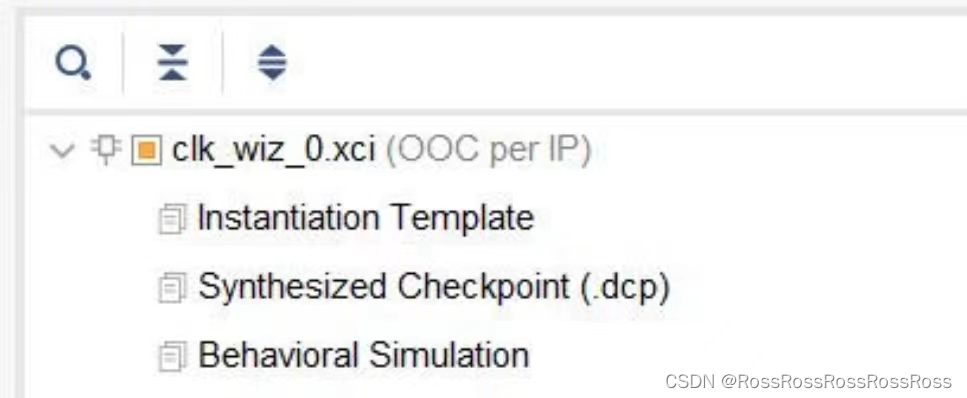

配置好自己的所有参数后,点击OK,生成我们想要的IP核

然后直接正常例化它就行了。

希望大家在FPGA开发中,积极考虑采用IP核。无论是为了缩短产品设计时间,还是为了提高设计的可靠性和性能,IP核都能提供强大的支持。随着技术的不断进步,越来越多的高质量IP核将被开发出来,为设计师提供更广阔的选择空间。因此,使用IP核,让它们成为您FPGA开发旅程中的得力伙伴。

谢谢大家的观看。祝各位越来越好。

12万+

12万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?