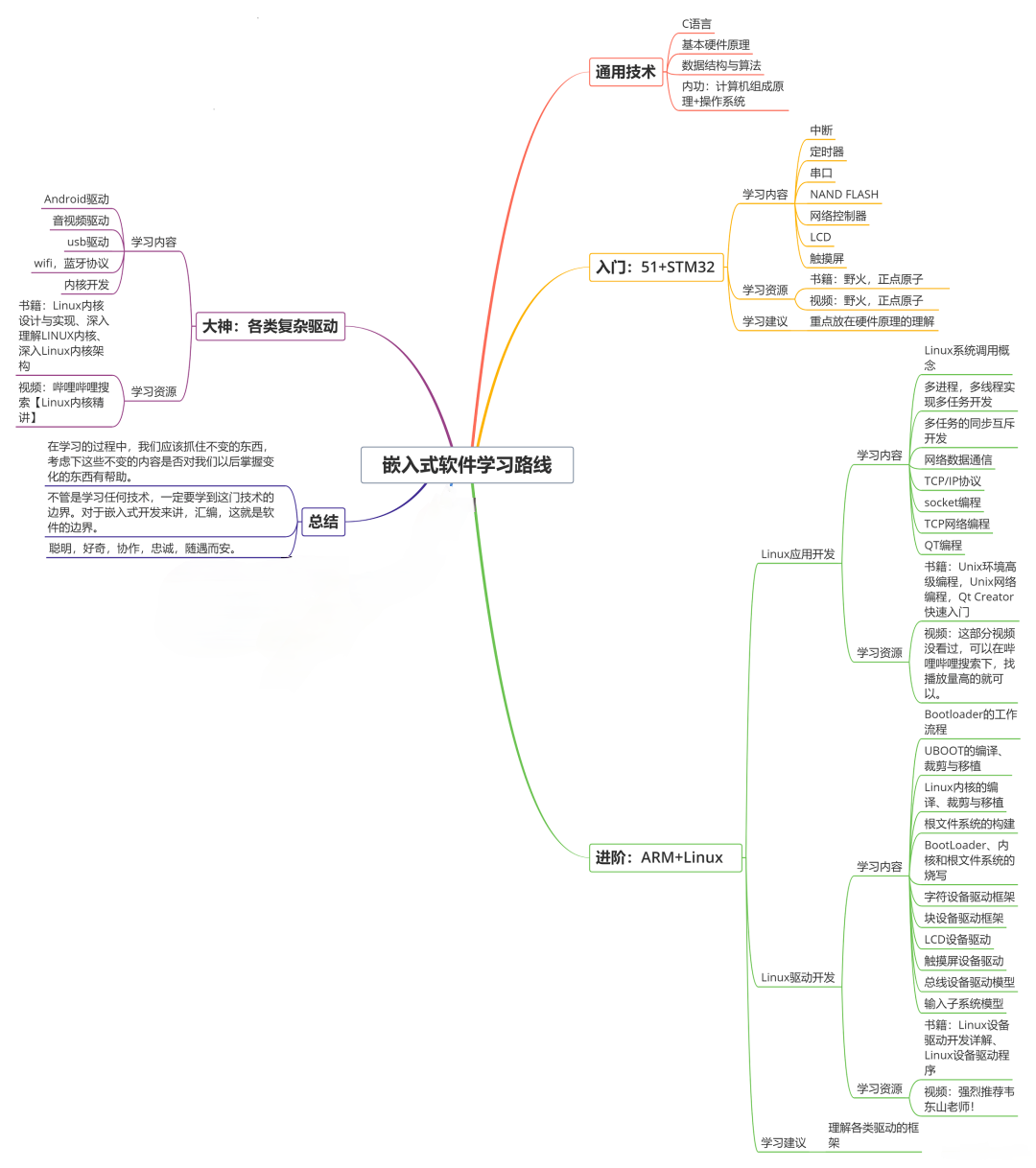

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

把这条规则的间距约束,设置小一点,如下图我设置的5mil。

最后发现就不再报绿色错误了。

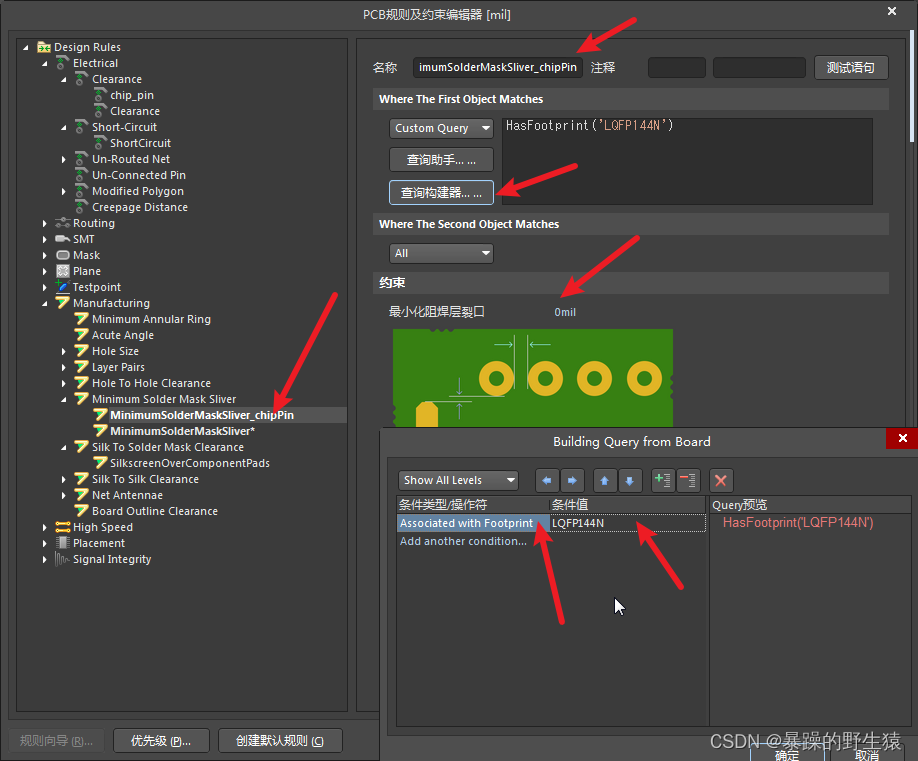

在新版本的AD中,也可以按照如上所述的步骤来处理,只是界面有些许变化,如下图所示的:where the first object matches位置处。

除了以上方法以外,新版本AD还有更简单的方法,直接在规则设置中,勾选上“忽略XXXX”就行了:(英文版为:ignore pad to pad clearance within fooprint)。

有时候,我们发现,按照以上步骤处理完,仍然有报错,运行DRC检查后,报错形如:

[Minimum Solder Mask Sliver Constraint Violation] xxx.PcbDoc Advanced PCB Minimum Solder Mask Sliver Constraint: (0.003mil < 10mil) Between Pad U4-127(2479.946mil,3521.552mil) on Top Layer And Pad U4-128(2460.258mil,3521.552mil) on Top Layer [Top Solder] Mask Sliver [0.003mil]

翻译过来就是:两个阻焊层间距过小。顶层,在U4芯片的第127脚和128脚。

报错的位置如下所示。

这个错误需要设置阻焊层规则才能解决,不过原理与前文一致。

首先点击:minimum solder mask sliver(阻焊层最小间距),

然后右击添加新规则,把最小间距改为0,如下图所示:

收集整理了一份《2024年最新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

IT行业的老鸟或是对IT行业感兴趣的新人**

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

343

343

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?