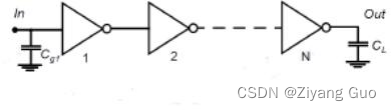

考虑CMOS反相器的驱动能力,所用MOS管的W/L越大,Req越小,驱动能力越大,但同时反相器的输入电容也会增大,延时增大,那么我们采用的方案是设计一个逐级增大的反相器链。

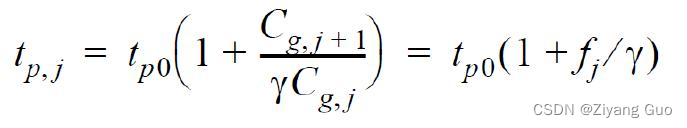

一个自然而然的问题是反相器的尺寸应该如何设计,才能使延时最小。对于一个N级的反相器来说,第j级反相器的延时表达式为

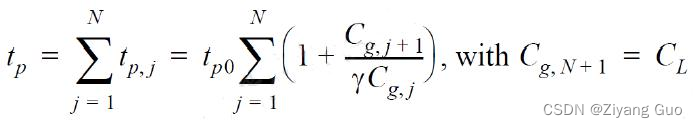

tp0称为本征传播延时,也就是无负载情况下仅由CMOS反相器自带的本征电容引起的延时,那后面的就是负载电容引起的延时,它和下一级反相器的尺寸有关。将这些延时逐级相加,得到总的延时:

在N确定的情况下,要求延时最小,你将如何设计反相器尺寸?进行一波数学上的求偏导取极值的操作,得到反相器的最优尺寸满足如下关系

那如果对N没有要求,你又将如何设计这个反相器链使得延时最小?最优级数为N=ln(F),(F为电路总的扇出)当然N只能取整数。

在实际的工程问题上,并不一定延时最小的方案是最佳方案,除了延时,还需要考虑面积和功耗。反相器链级数越多,面积之和一般越大(在IC上面积就是金钱),电容之和也大,功耗也大。

-------------------------------------------------------------------------------------

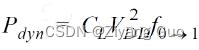

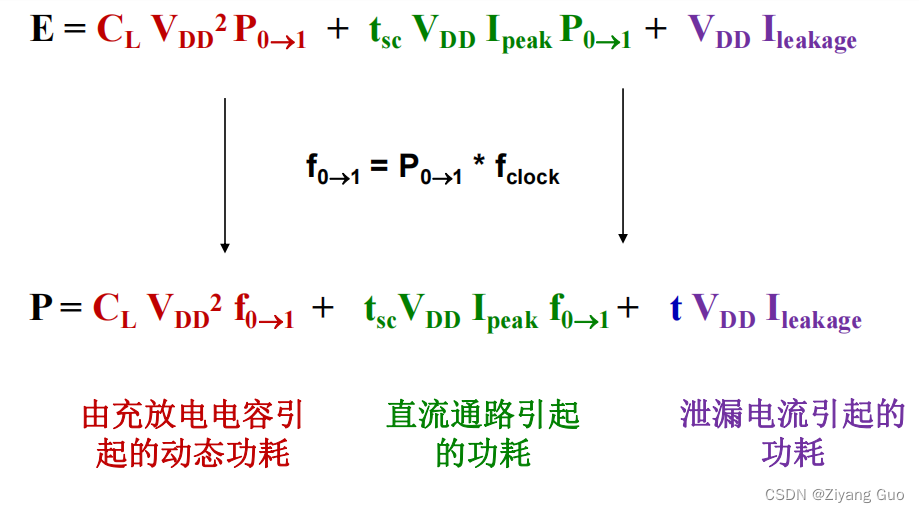

现在我们考虑CMOS反相器的动态功耗应该如何计算。我们用于计算的模型是这样的,MOS管是带有恒定电阻的开关,且NMOS和PMOS不会同时导通。在这个条件下,考察Vout从低到高CL被充电,Vout再从高到低CL被放电的过程,通过简单的积分计算可以得知,每完成一次这个充放电的过程,都需要这么多能量,考虑开关频率为f,即这个开关每秒通断f次,由此可以计算出这个反相器的动态功耗为

另外,最大可能的开关频率f满足T=1/f=2tp,它的上限由延时决定。

如果考虑NMOS和PMOS同时导通的时间,那么需要加上一个直流通路引起的功耗,它和tsc(同时导通的时间)、VDD、Ipeak(直流通路电流大小)、f(开关频率)都成正比。

如果考虑泄漏电流(也就是开关并没有完全闭合上)引起的功耗,那么这部分功耗就表示为t*VDD*I_leakage。

总消耗能量和总功耗可以用下面这个图来表示

f_clock是时钟频率,也是开关频率的上限,P0->1是在一个时钟周期内开关翻转的概率。

文章讨论了在设计CMOS反相器时如何平衡延时和驱动能力。通过数学分析,得出反相器尺寸的最优设计策略以最小化延时,同时也考虑了级数、面积和功耗的影响。动态功耗的计算涉及开关频率、充电放电过程以及泄漏电流等因素。文章强调在实际工程中,最佳方案需综合考虑多个因素,而不仅仅是最小化延时。

文章讨论了在设计CMOS反相器时如何平衡延时和驱动能力。通过数学分析,得出反相器尺寸的最优设计策略以最小化延时,同时也考虑了级数、面积和功耗的影响。动态功耗的计算涉及开关频率、充电放电过程以及泄漏电流等因素。文章强调在实际工程中,最佳方案需综合考虑多个因素,而不仅仅是最小化延时。

730

730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?