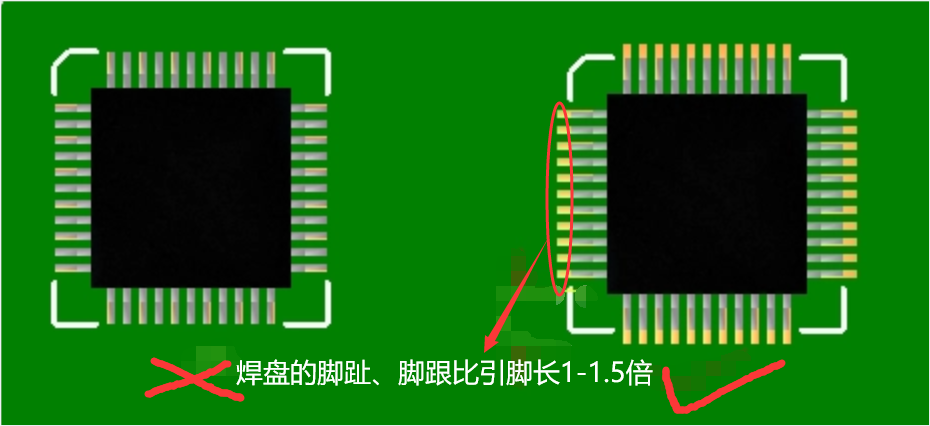

一、增长引脚焊盘

● 这种方式适用于QFP系列封装的元件。

在回流焊时,增长的引脚焊盘可以加强元件引脚的引力,有利于元件的居中对齐与定位;同时在波峰和手工焊接时,增长的引脚焊盘也可以起到偷锡的作用,具体要求如下:

1、 焊盘宽度与元器件引脚相同。

2、 焊盘长度为元器件引脚的1-1.5倍。

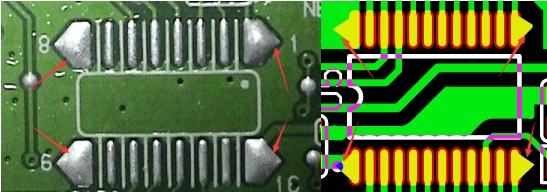

二、增加偷锡焊盘

● 这种方式适合用于SOP系列封装的元件。

在原有的封装基础上,增加一个边脚焊盘,来达到元件引脚不连焊的目的,具体要求如下:

1、 焊盘封装引脚间距小于1.27mm时,必须增加偷锡焊盘。与元器件引脚相同。

2、 偷锡焊盘形状、大小、类型应与其他引脚焊盘相同。

3、 偷锡焊盘与末尾焊盘的间距,应等同于封装的引脚间距。

4、 背面的偷锡焊盘,应加在PBA走向的下游方位。

5、 偷锡焊盘应与其相邻的末尾焊盘同一网络或悬空,不应与末尾焊盘有冲突,以免在偷锡焊盘与末尾焊盘连焊时,造成不同网络的短路。

6、 若偷锡焊盘位于元件外框丝印的内部或覆盖外框丝印,应对外框丝印进行调整,以使偷锡焊盘位于元件外框丝印之外,避免造成焊接错位。

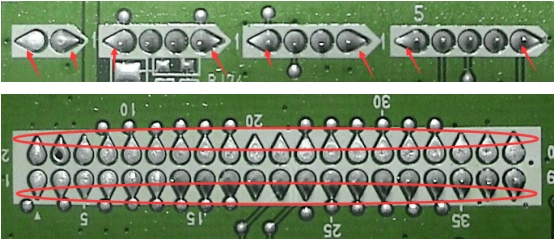

三、增加拖尾焊盘

● 这种方式适用于DIP、SIP、ZIP等系列封装的元件。

在原封装的基础上,将PBA走向的末尾焊盘背面更改为圆锥形,锥尖背离PBA走向,具体要求如下:

1、 封装引脚间距小于2.0mm时,必须增加拖尾焊盘。

2、 封装平行于PBA走向时,只在末尾引脚增加拖尾焊盘;封装垂直于PBA走向时,每间隔一个引脚增加一个拖尾焊盘。

在PCB设计中,偷锡焊盘的处理是确保焊接质量和一次性成功率的关键;通过增长引脚焊盘、增加偷锡焊盘和增加拖尾焊盘等方式,可以避免元件引脚连焊,提高焊接效果。

在处理过程中,需要根据具体元件的封装和焊接要求,选择合适的处理方式,且需要注意细节,以确保焊接效果最佳。

本文介绍了PCB设计中增长引脚焊盘、增加偷锡焊盘和拖尾焊盘的策略,以提升焊接质量和成功率,防止元件引脚连焊,强调了根据元件封装和焊接需求选择适当方法的重要性。

本文介绍了PCB设计中增长引脚焊盘、增加偷锡焊盘和拖尾焊盘的策略,以提升焊接质量和成功率,防止元件引脚连焊,强调了根据元件封装和焊接需求选择适当方法的重要性。

2324

2324

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?