SODIMM 简介

SODIMM 接口DDR3适配额外的内存条才能满足数据缓存的需求,这种需求一般用于高端项目,DDR3 SDRAM 常简称 DDR3, 是当今较为常见的一种储存器, 在计算机及嵌入式产品中得到广泛应用,特别是应用在涉及到大量数据交互的场合。

MIG配置流程

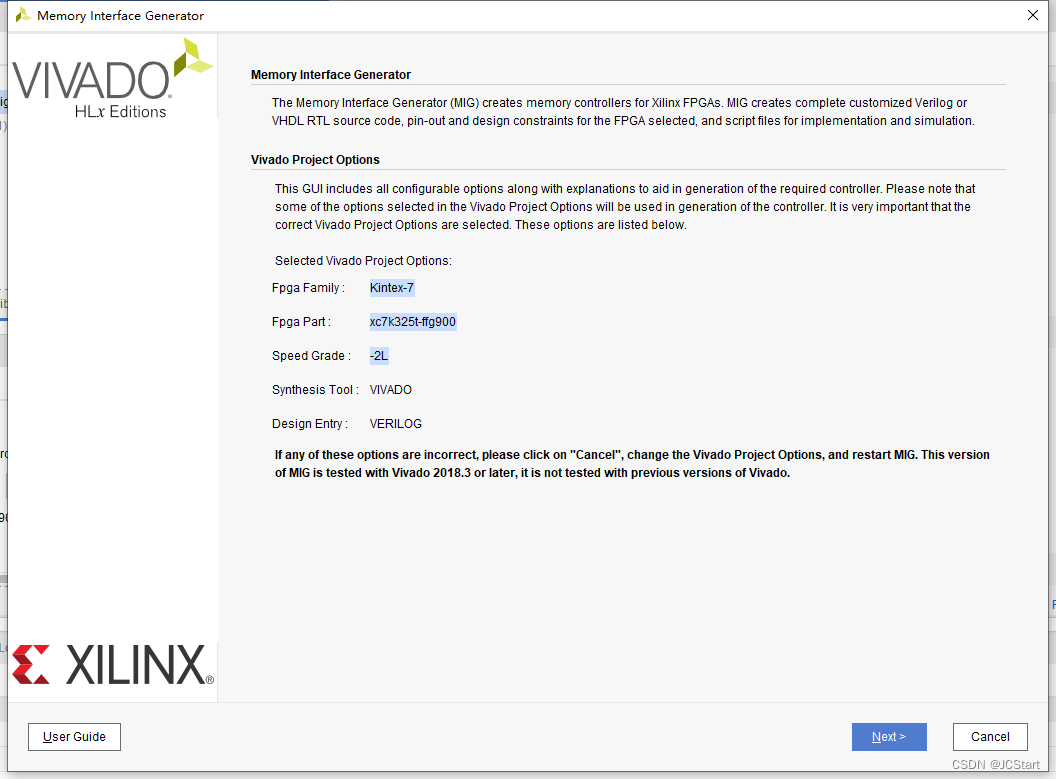

本文以XC7K325T-FFG900-2L为例,记录MIG的配置过程,进入IP配置界面后,第一个界面是 Memory Interface Generator 介绍页面, 如下图所示。默认的器件家族(FPGA Family)、器件 型号(FPGA Part)、速度等级(Speed Grade)、综合

工具(Synthesis Tool)和设计输入语言(Design Entry)都和创建工程是保持一致。

注意点

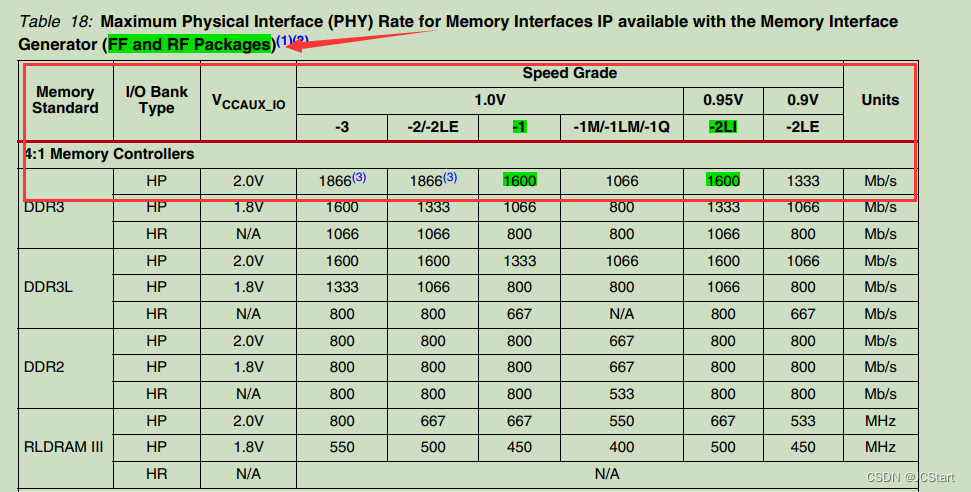

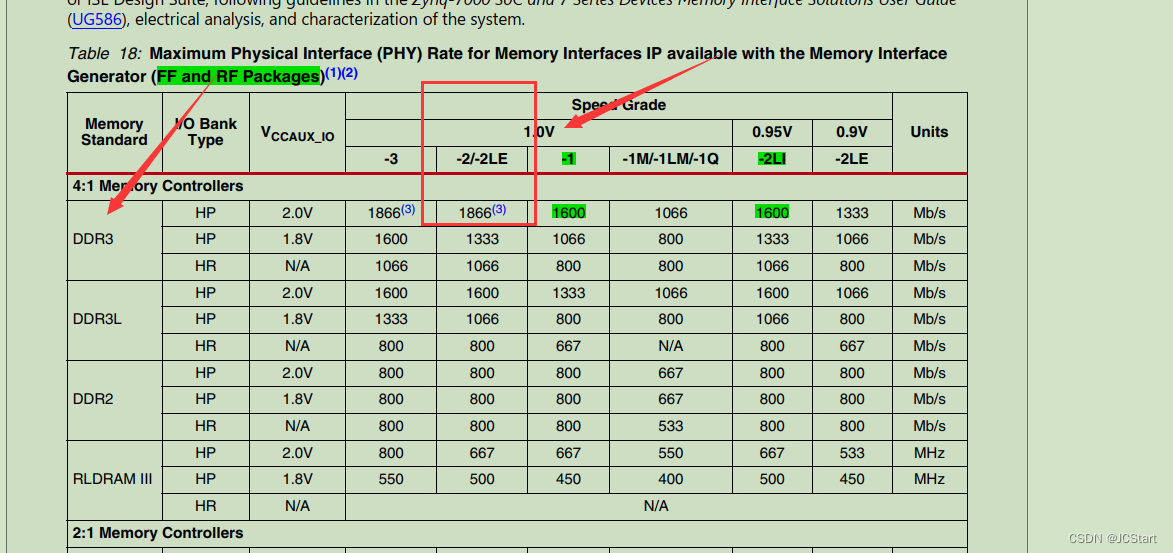

这里的速度等级和封装都要选准确,速度等级将会影响后续的可配置的最大速率,参考DS182

点击 Next 到 MIG Output Options 配置页面中, 如下图所示。 勾选“Create Design”,默认名称(Component Name)为“mig_7series_0”,用户可对其进行修改,这里保持默认。选择控制器数量(Number of Controllers)为 1,本次 MIG IP 的用户接口使用 AXI 协议接口,勾选 AXI4 Interface。

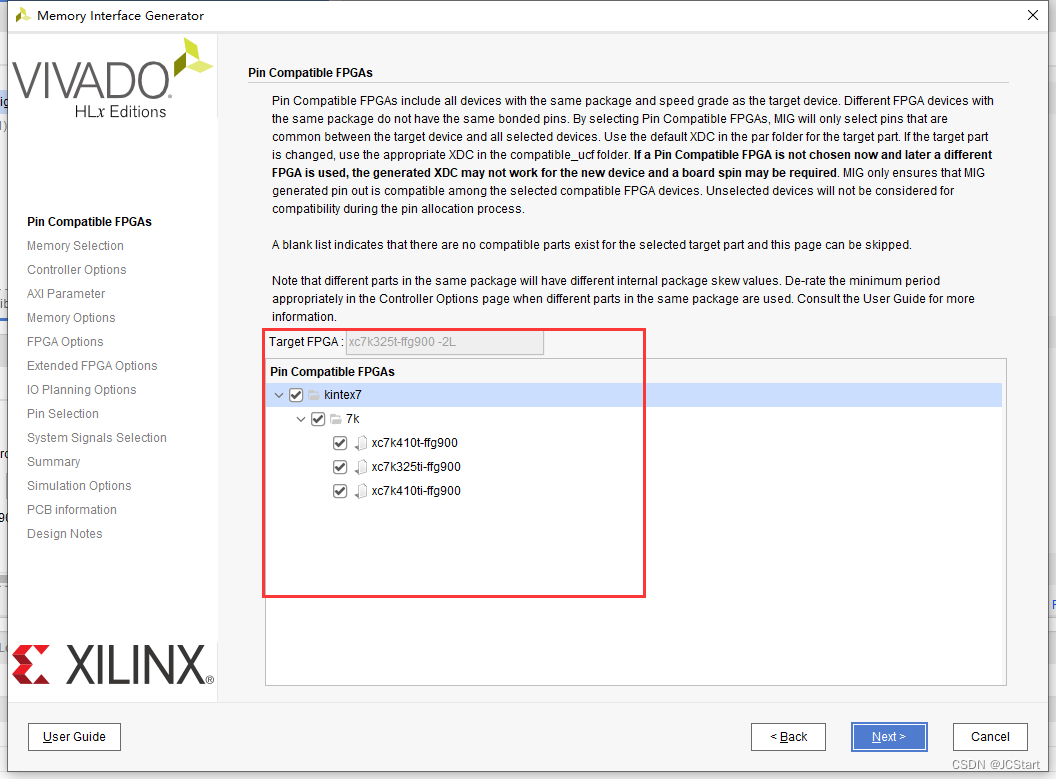

点击 Next 到 Pin Compatible FPGAs 配置页面,如下图所示该界面可用于配置选择和当前所设定的唯一器件型号做引脚兼容的其它 FPGA 型号。本次办卡设计需同时兼任XC7K410对此而言,这个功能是很实用的。

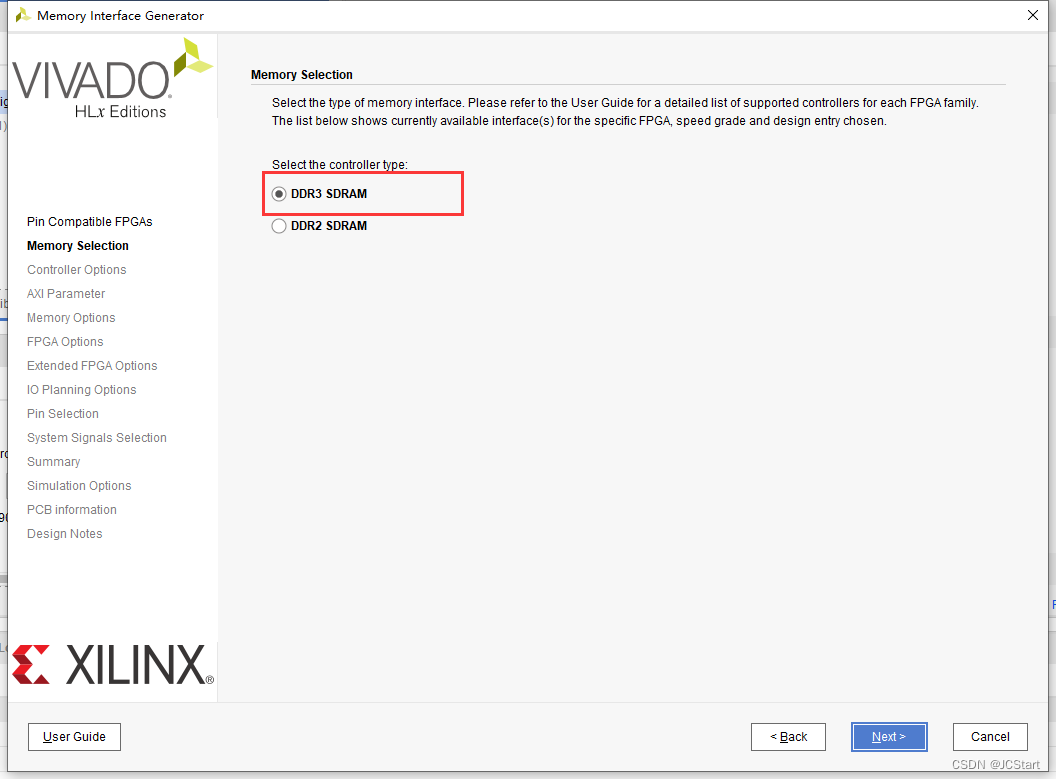

点击 Next 进入到如下图所示的 Memory Selection 配置页面,这里选择“DDR3 SDRAM” 即可。

SODIMM配置关键点

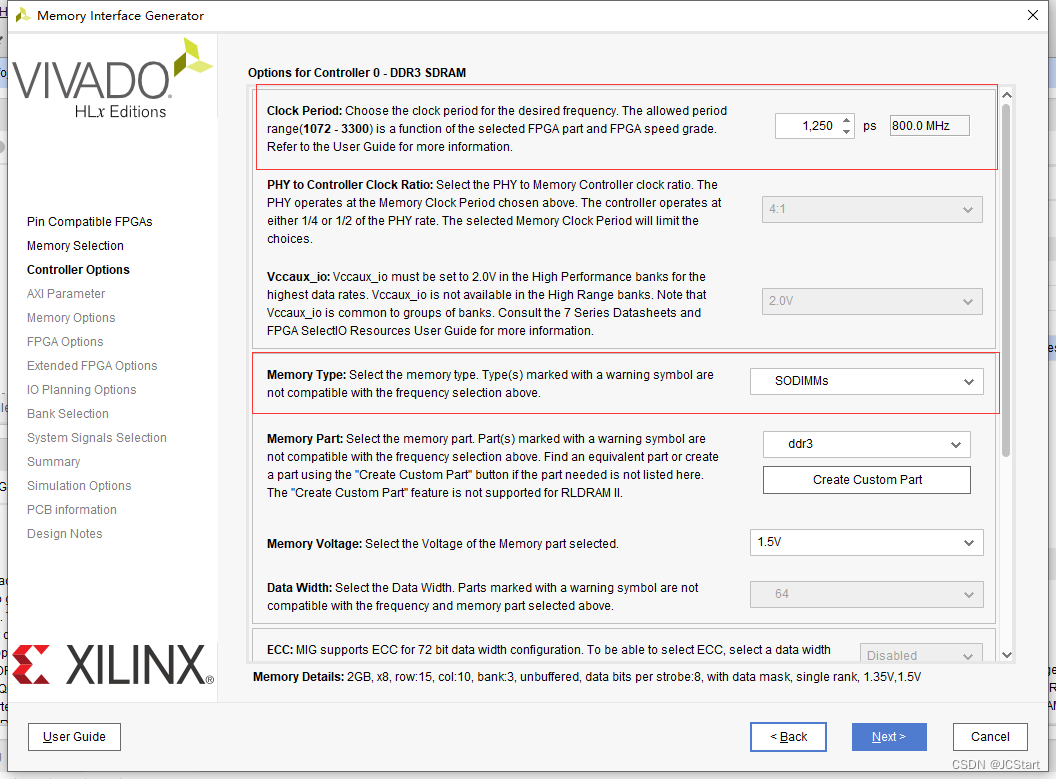

DDR3 存储器驱动的时钟周期(Clock Period)设置为 2500ps(即 400MHz), 这个时钟是用于 FPGA 输出给到 DDR 存储器时钟管脚的时钟。注意这里根据实际情况是有设置区间范围的,并非可以设置任意值,这里的区间范围为 2500~3300ps(即300~400MHz)这个区间范围是有讲究的。

本文使用的型号是XC7K325TFFG900-2L,对应的DDR3最大速率为1866Mb/s,

芯片速率等级是-2L,支持ddr3的最大速度是1866Mb/s,DDR3又是双边沿触发,所以最高支持1072ps,也就是933Mbs,这里将DDR3 存储器驱动的时钟周期(Clock Period)设置为 1250ps(即 800MHz)。

DDR3 存储器类型(Memory Type)为 SODIMM。

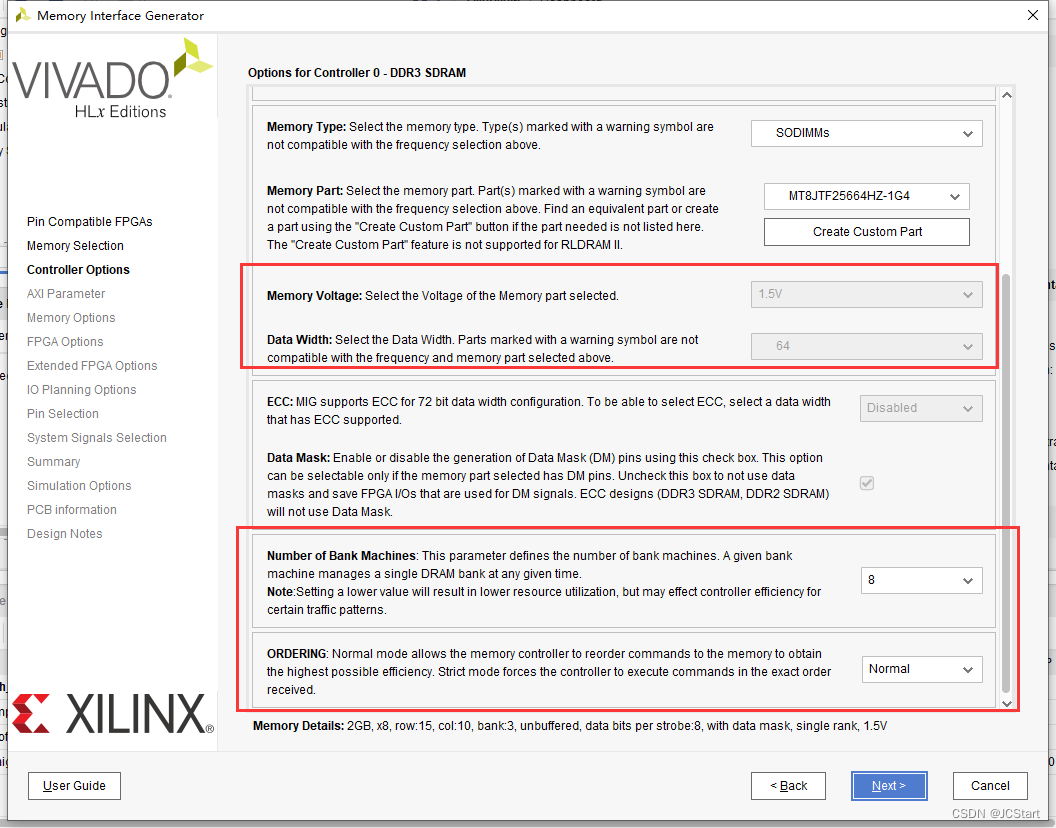

DDR3 存储器型号(Memory Part)为 MT41J2564HZ-1G6,这是开发板板载 DDR3存储器的实际型号。DDR3 存储器接口电压(Memory Voltage)为 1.5V。 DDR3 存储器位宽(Data Width)为 64,这里MIG已经默认了选择了DDR 控制器的 bank machines 个数设置,这里参数与 DDR3 物理 bank 个数并非是同一概念,设置上并非一定需要与 DDR3 物理 bank 个数保持一致(当然设置相同数量可以增加 DDR 控制器的效率和性能,但是会占用相对多的资源,时序上要求也相对要高。性能和资源上如何达到一个比较好的平衡,需要根据实际应用场景进行设置,有关详细的设置指导可参考文档 7 Series FPGAs Memory Interface Solutions)。

DDR 控制器调度命令的顺序的配置,当选择 strict 时,严格按照命令先后顺序执行;选择 normal 时,为了得到更高的效率,可能对命令重排序。我们选择normal 。

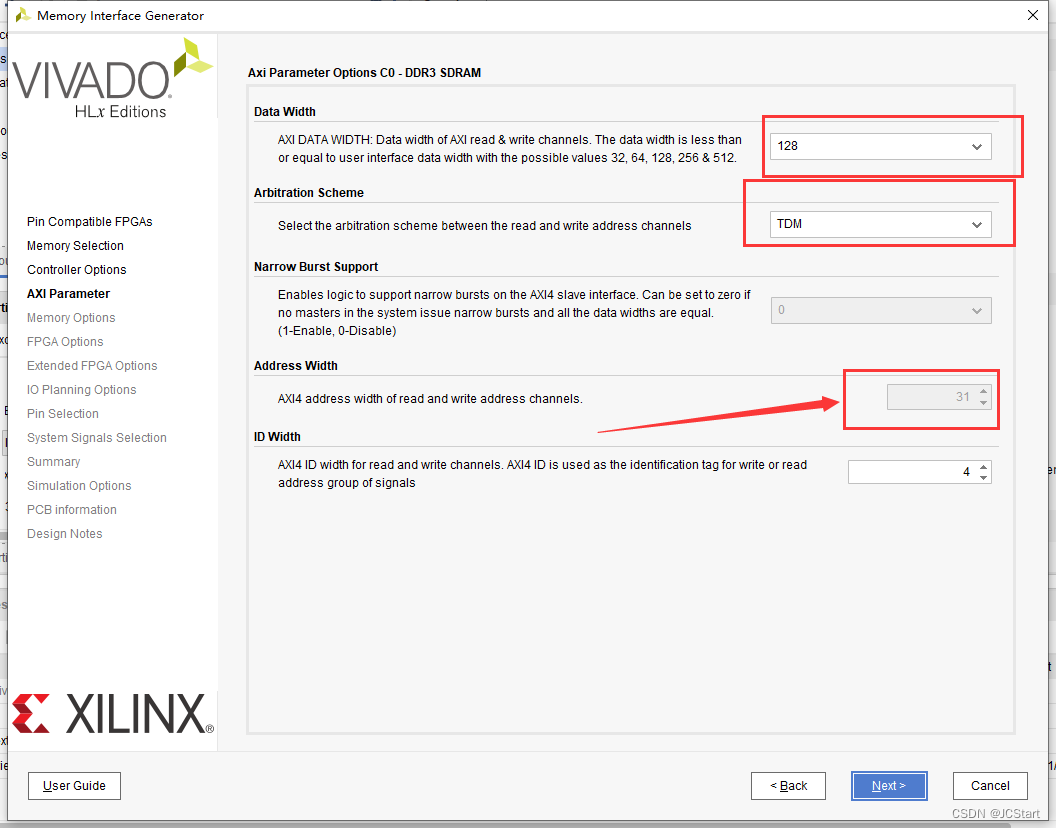

点击 Next 进入到如下图所示 AXI Parameter 配置页面。 该界面是对 AXI 接口相关参数

进行配置,具体配置如下。

(1) AXI 接口的数据位宽,设置为 128。

(2) DDR 控制器的仲裁机制,由于 AXI 接口读写通道是独立的,读写各有自己的地址通道,而储存器控制器只有一个地址总线,同一时刻只能进行读或写,这样就存在读/写优先级的问题,这里设置 TMD(Time Division Multiplexing),该设置读写优先级相同,读写交替进行。

(3) Narrow Burst 支持,设置 0,将其关闭。

(4) AXI 接口的地址位宽,自动根据 DDR3 内存生成的位宽,这里 AXI 地址对应的数据是以 1 字节进行计算的,不要与 DDR3 的地址和存储数据混淆。板载 DDR3 存储器存储空间 2GB (2GB = 2048MByte = 2^31 Byte,所以 AXI 的地址位宽为 31)。

(5) AXI 读/写通道的 ID 宽度。 ID 是用来标识读/写响应和读/写数据的一致性。

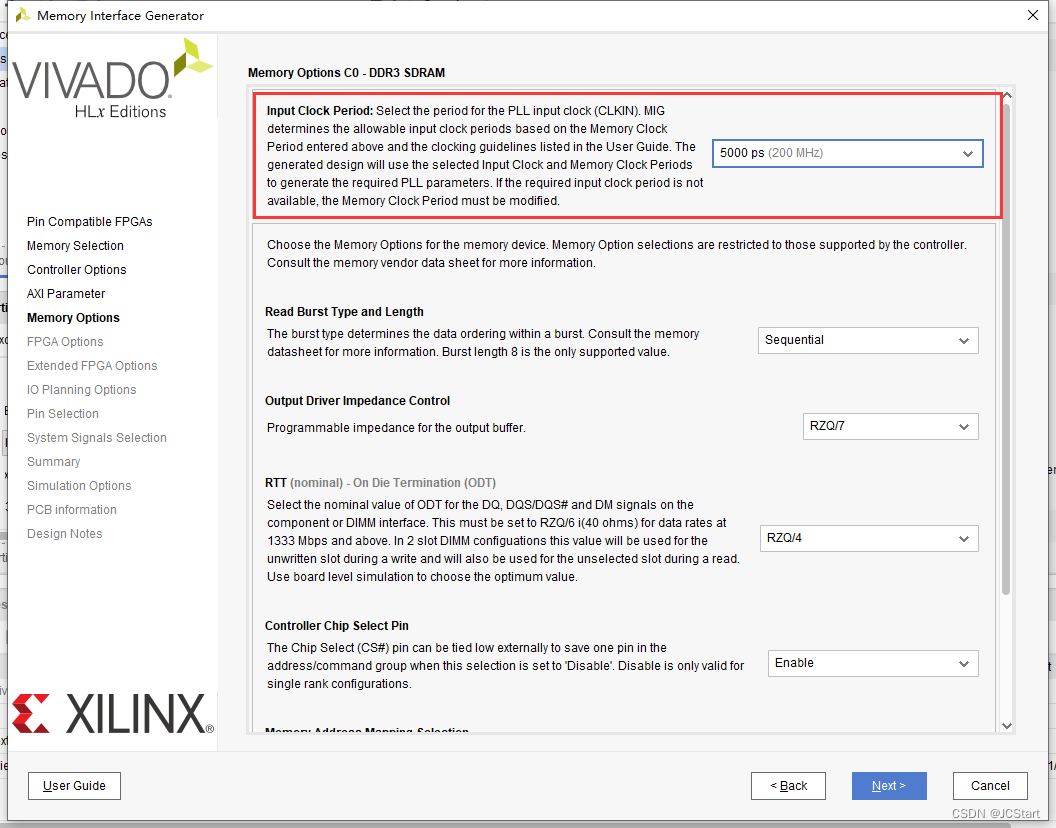

输入系统时钟频率设置, 这个时钟是提供给 MIG IP 的时钟。

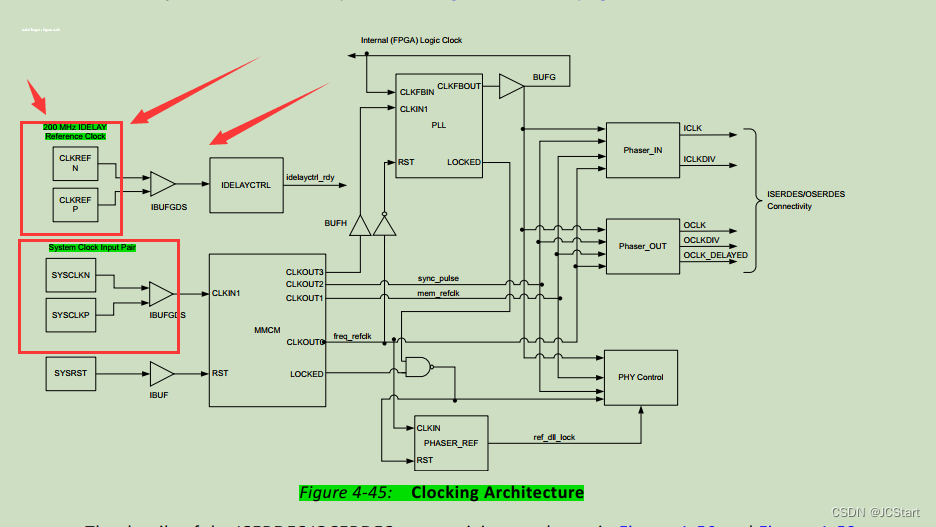

如下图所示为 MIG IP 内部关于时钟的结构图,可以看到 MIG IP 里面有一个时钟锁相环,系统时钟是这个时钟锁相环的输入时钟,锁相环会根据这里的输入时钟自动产生 MIG IP 内部各种所需的时钟。所以这里的时钟频率的设置没有固定的要求,下拉框中的各种频率值都可以选择。这里考虑到 MIG IP 输入还需要一个 200M 的 IDELAYReference Clock 时钟,为了将两个时钟共用一个输入时钟,

将这里的系统时钟周期(Input Clock Period) 配置选择为 5000ps(200MHz)。

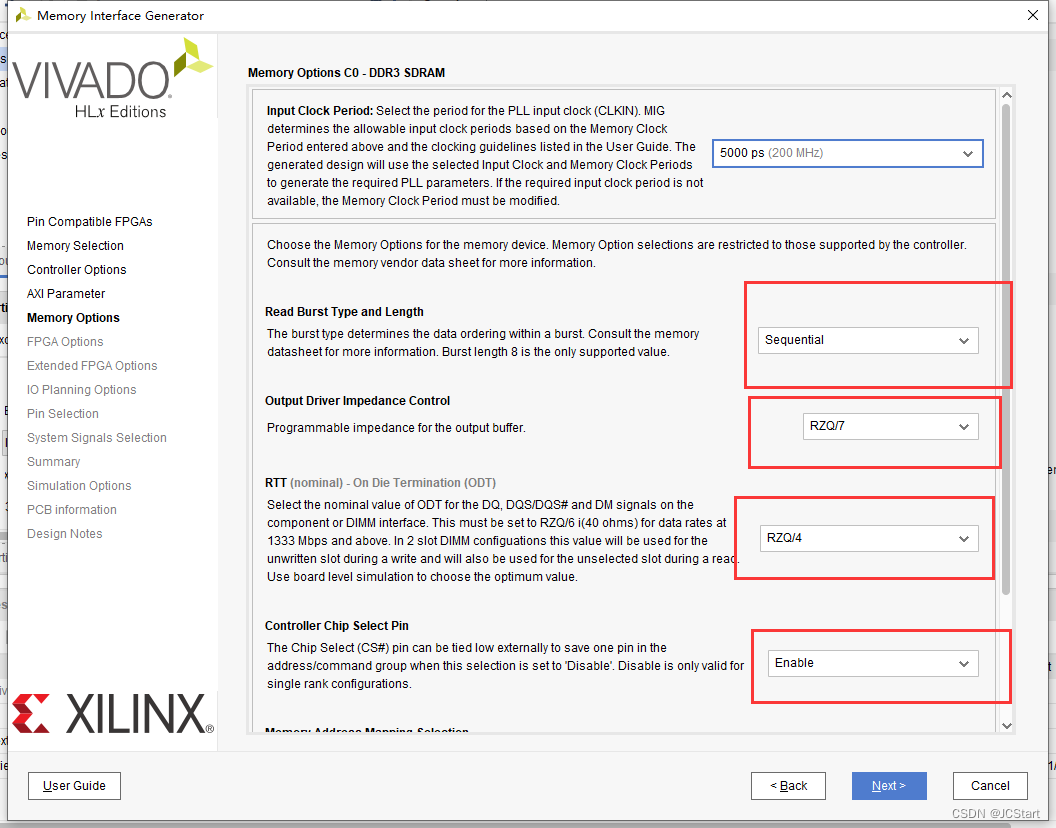

突发读类型和长度(Read Burst Type and Length)设置为顺序读写 Sequential。输出驱动阻抗控制(Output Drive Impedace Control)选择 R ZQ/7。片上终端(On Die Termination)设置为 R ZQ/4片选信号(Controller Chip Select Pin)设置为 Enable,即使用该引脚,实际开发板的DDR3 的 CS 信号有连接到 FPGA 管脚,所以这里需要使用该引脚。如果硬件上 DDR3管脚未连接到 FPGA,那么这里就可以设置为 Disable。DDR 和 AXI 总线之间的地址映射存储器

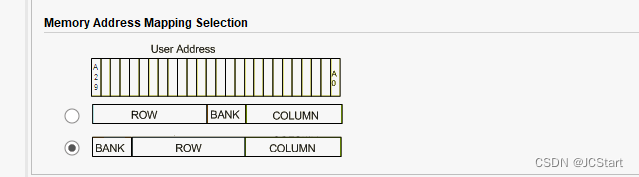

地址映射选择( Memory Address MappingSelection)。默认选择后者。BANK_ROW_COLUMN: 寻址方式选择。本实验选择第二种,即 BANK-ROW-COLUMN 的形式,这是一种最常规的 DDR3 寻址方式,即要指定某个地址,先指定 bank,再指定行,最后指定列,这样就确定了一个具体地址。一般来说这样寻址方式有利于降低功耗,但是读写性能(效率)上不如“ROW_BANK_COLUMN”。 配置完成点击“Next”。

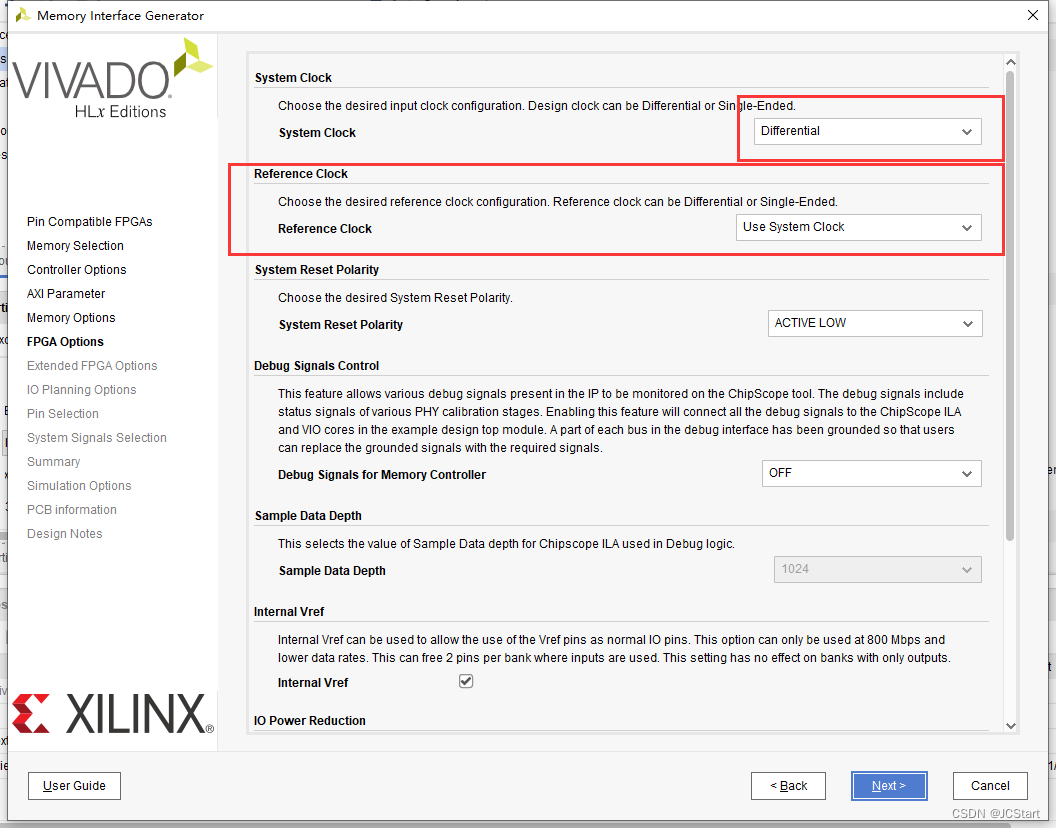

系统时钟(System Clock): 这里的系统 200M 时钟直接由200M差分晶振提供,不由管脚输入,选择Differential(差分输入),如果实际由FPGA提供 200MHz 时钟,也可以选择 No Buffer

参考时钟(Reference Clock):该时钟需要频率为 200MHz 时钟,由于在前面配置中将系统时钟设置为 200MHz,所以可以选择 Use System Clock,这样就可以将两个输入时钟合并一个共用的 200MH 输入。如果前面的系统时钟设置的不是 200MHz 这里配置选项就没有“Use System Clock”可选,只能由管脚端口输入时钟或者 FPGA 内部产

生这个 200MHz 时钟。

(3) 系统复位极性(System Reset Polarity): 选择 ACTIVE LOW。

(4) 存储器控制器的调试信号(Debug Signal for Memory Controller)选择 OFF。

(5) 勾选 internal Verf。

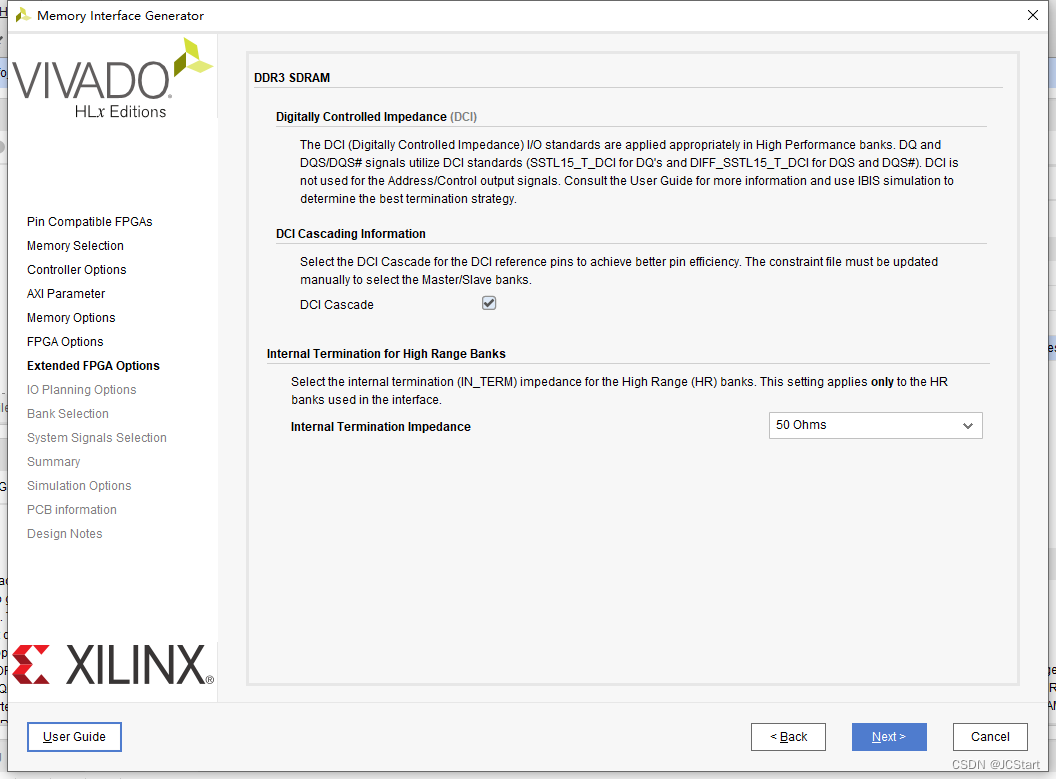

Next 进入到如下图所示的 Extended FPGA Option 配置页面中,设定内部终端阻抗(Internal Termination Impedance)为 50 Ohm。

IP Core中设置启用DCI Cascade功能,IP中功能描述:“Select the DCI Cascade for the DCI reference pins to achieve better pin efficiency. The constraint file must be updated manually to select the Master/Slave banks”。

在约束中添加“set_property DCI_CASCADE {32 34} [get_iobanks 33]”(基于K7系列),将这三个bank的数控电阻级联,以保证MIG初始化完成,若不加此约束,对于双边沿800M的配置可能初始化信号一直不拉高

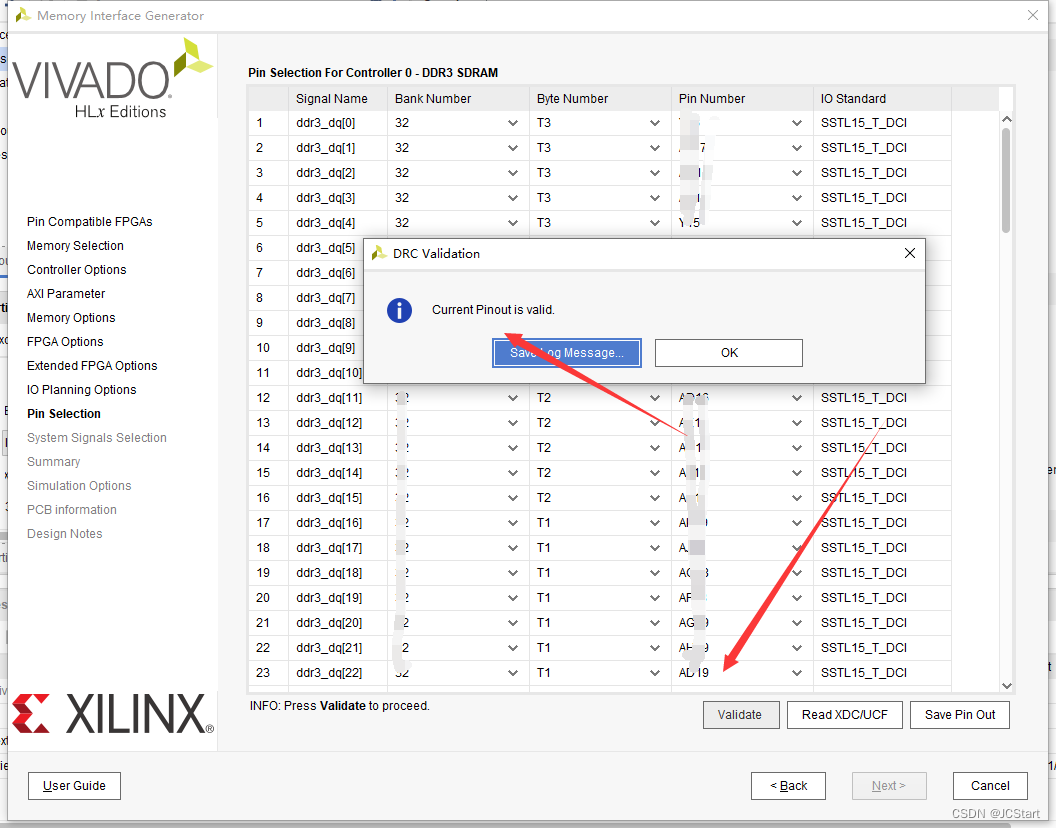

Next 进入到如下图所示的 Pin Selection 配置页面中,所有 DDR3 存储器相关的引脚定义引脚号(Pin Number)以及 IO 电平标准(IO Standard) 的配置,需要和原理图连接相一致。这里有 2 中配置方式,其中一种配置方式是采用手动输入的方式,该种方式下只需要对配置界面中 Pin Number 那一列根据原理图或提供的管脚分配表选择相应的管脚即可。在选择设置完后, Bank Number 和 Byte Number 会自动填充对应的配置。手动输入模式下,IO Standard 不需要手动输入配置。

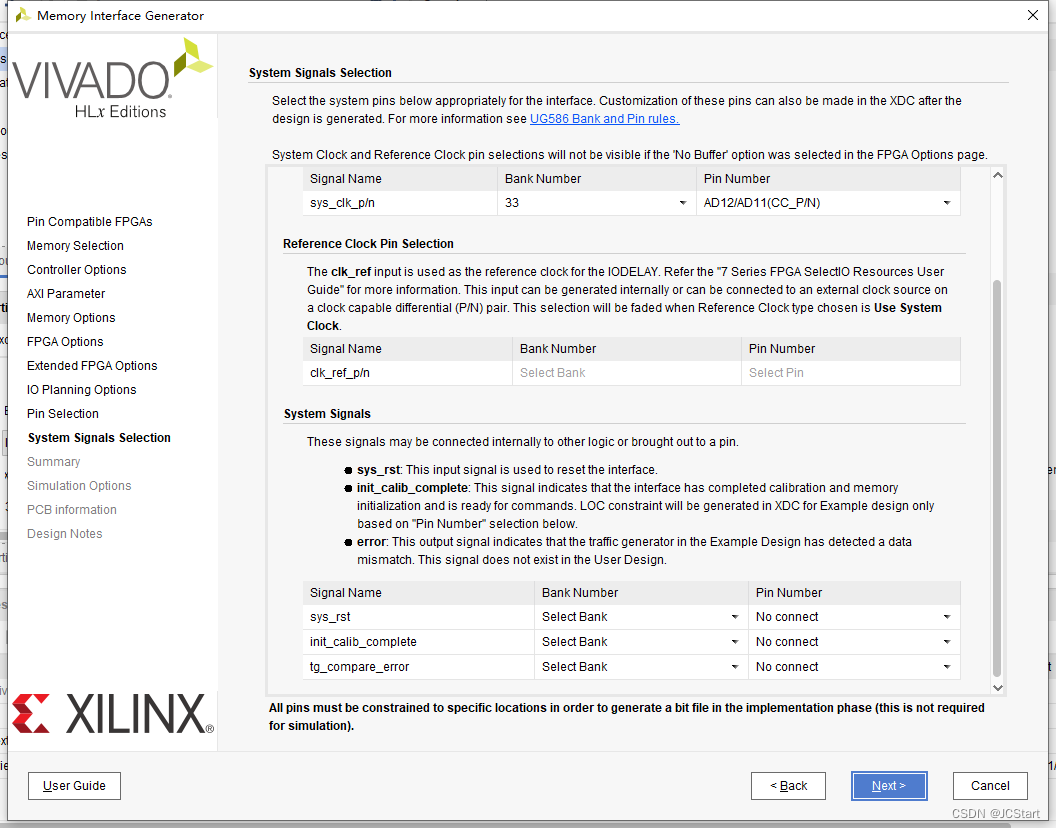

点击 Next 进入到如下图所示的 System Signals Selection 页面,该页面无需配置,默认

即可。

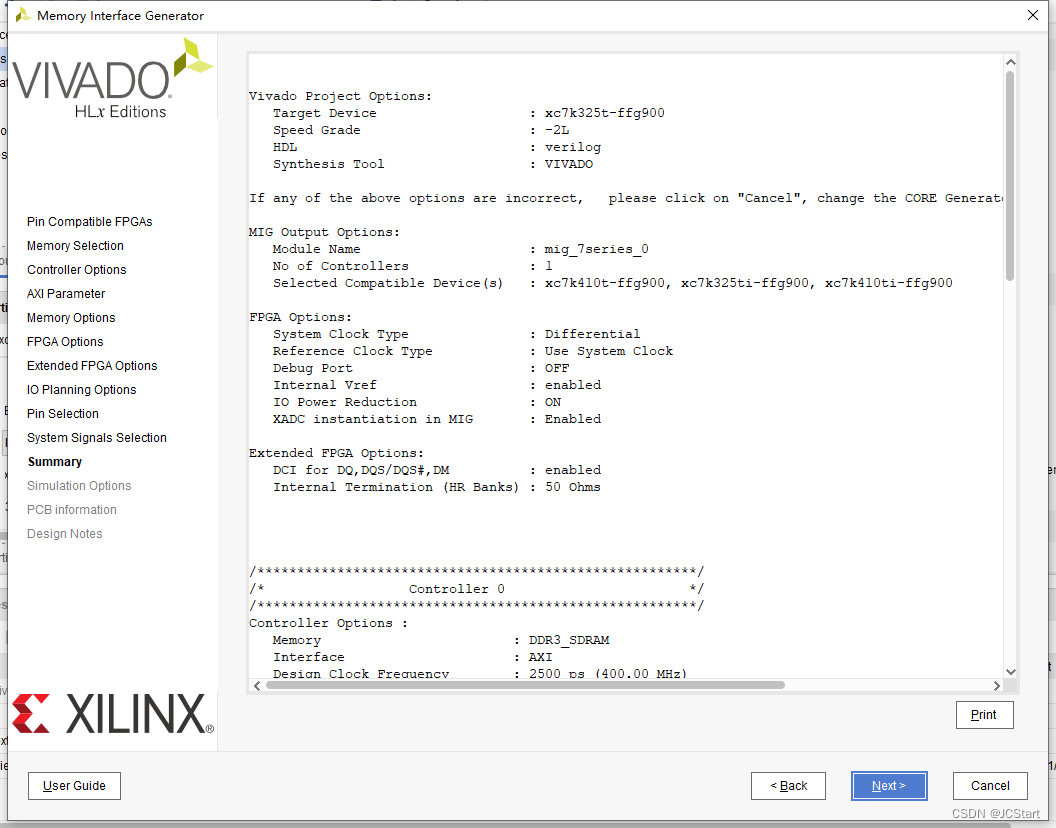

配置界面总结如下,即完成了MIG对SODIMM的配置

配置界面总结如下,即完成了MIG对SODIMM的配置

文章阐述了SODIMMDDR3在项目中的应用和MIG配置步骤,涉及速度等级、接口选择、时钟周期调整等内容,旨在帮助读者理解高级内存配置技巧。

文章阐述了SODIMMDDR3在项目中的应用和MIG配置步骤,涉及速度等级、接口选择、时钟周期调整等内容,旨在帮助读者理解高级内存配置技巧。

3005

3005

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?