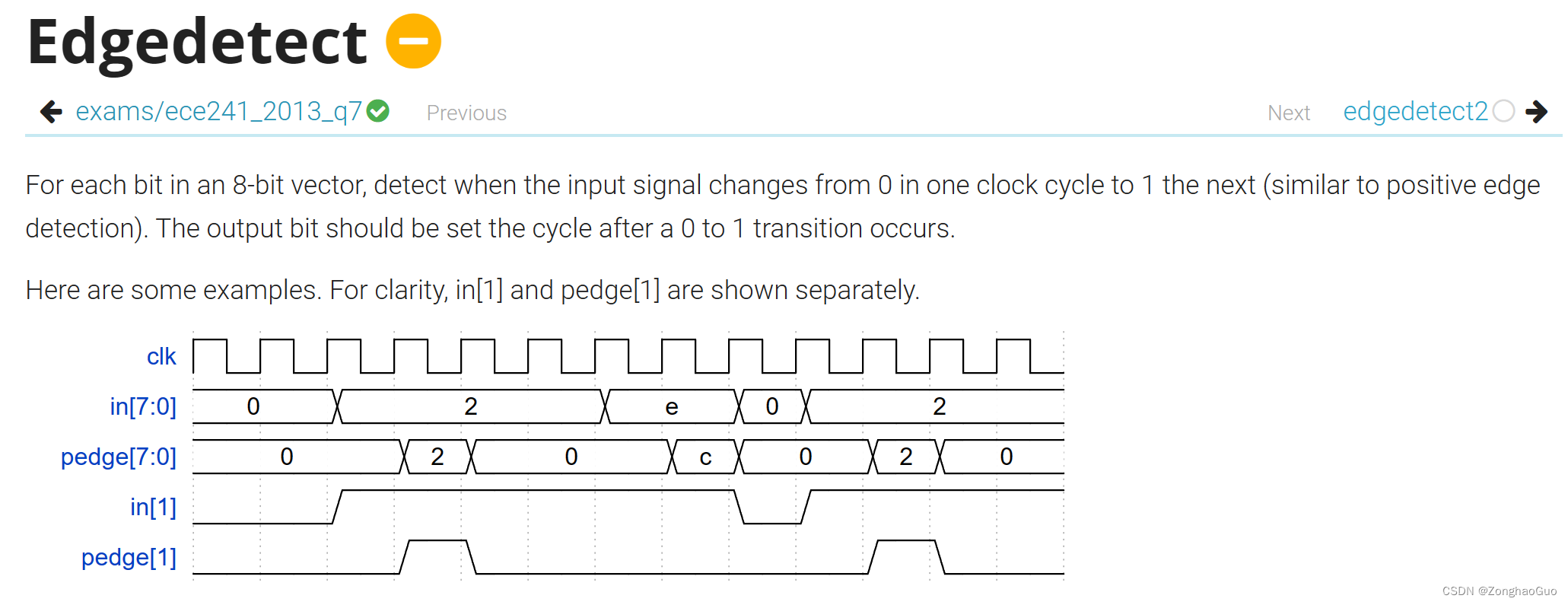

Edgedetect

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0] in_state;

always @(posedge clk)

begin

in_state<=in;

pedge = in&~in_state;

end

endmodule

分析:利用了非阻塞赋值在时钟周期末赋值的特性,其次,计算上升沿的位置,首先当前时刻得是1,上一时刻得是0,因此才有pedge = in&~in_state. 并且会在一个周期后清楚上升沿所在位。

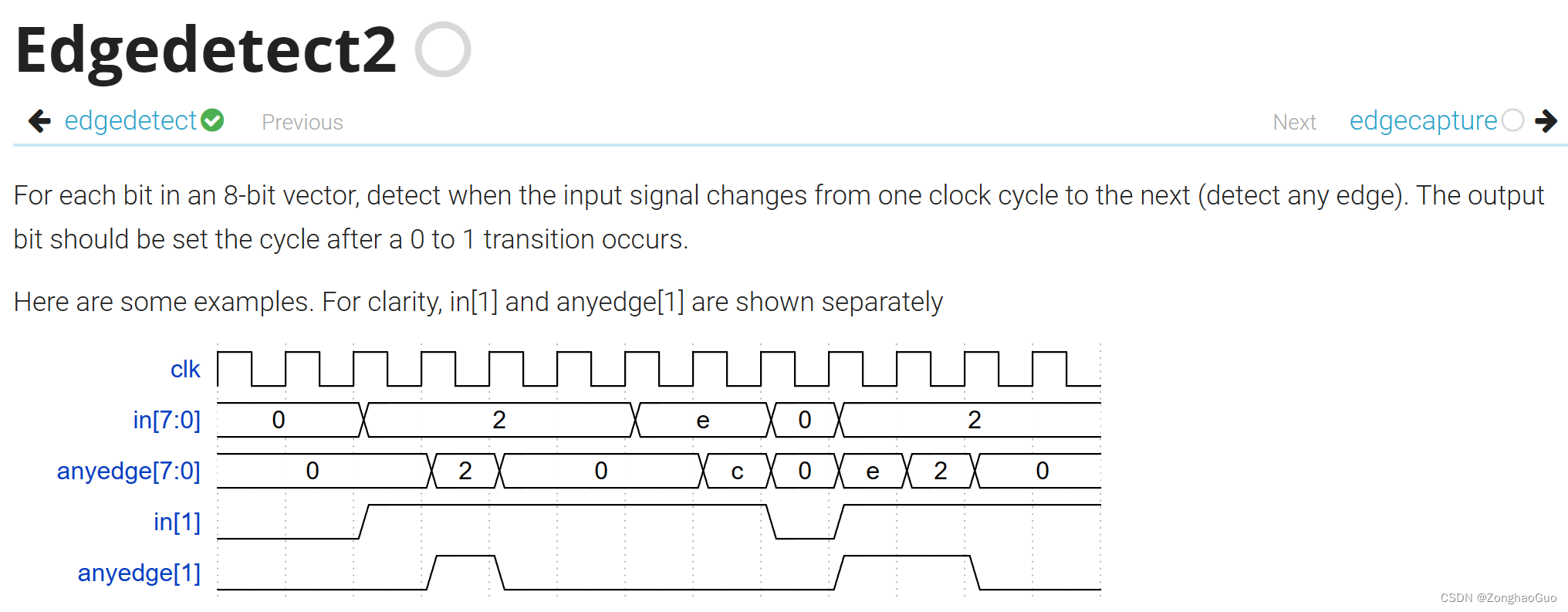

Edgedetect2

与Edgedetect1不同的是,此题是检测数据变化的任意边缘。因此只需要使用异或门即可

module top_module (

input clk,

input [7:0] in,

output [7:0] anyedge

);

reg [7:0] in_state;

always @(posedge clk)

begin

in_state<=in;

anyedge <= in^in_state;

end

endmodule

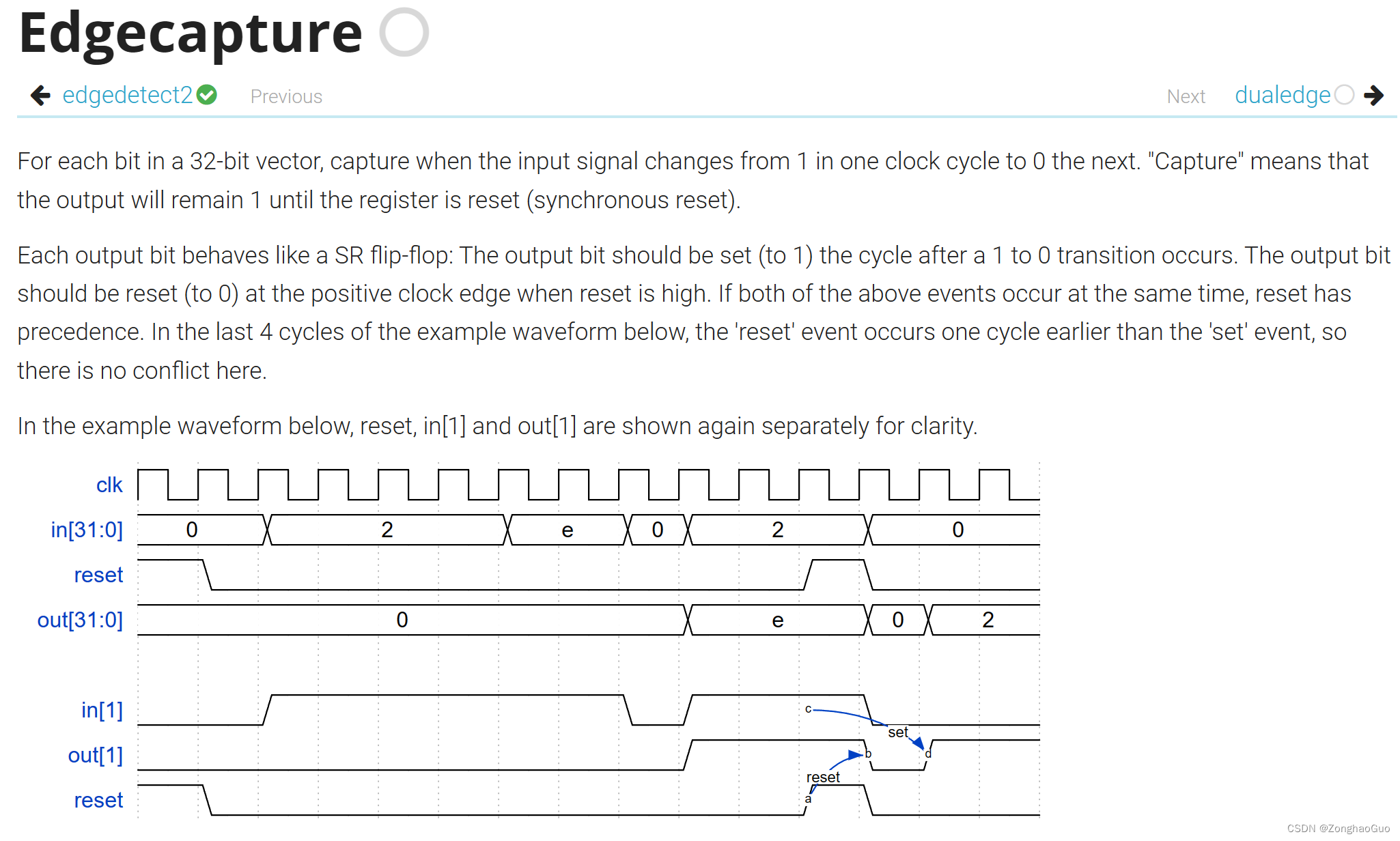

Edgecapture

低电平捕获,此问题需要注意两个细节

1,在捕获低电平后要一直维持捕获状态

需要如何做才能保持呢?答:与上一时刻的输出状态进行,按位或操作。因为一旦捕获,输出位即为高电平,与高电平按位或即可保持。

2,当reset复位操作进行时,应同时记录输入状态,因此需要两个always赋值操作。

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] pre_in;

always @(posedge clk)

pre_in <= in;//无论是否进行低电平捕获,实时记录输入值

always @(posedge clk)

if(reset)

out <= 32'd0;

else

out <= (pre_in & ~in) | out;//与上一时刻的输出按位或,以保持状态

endmodule

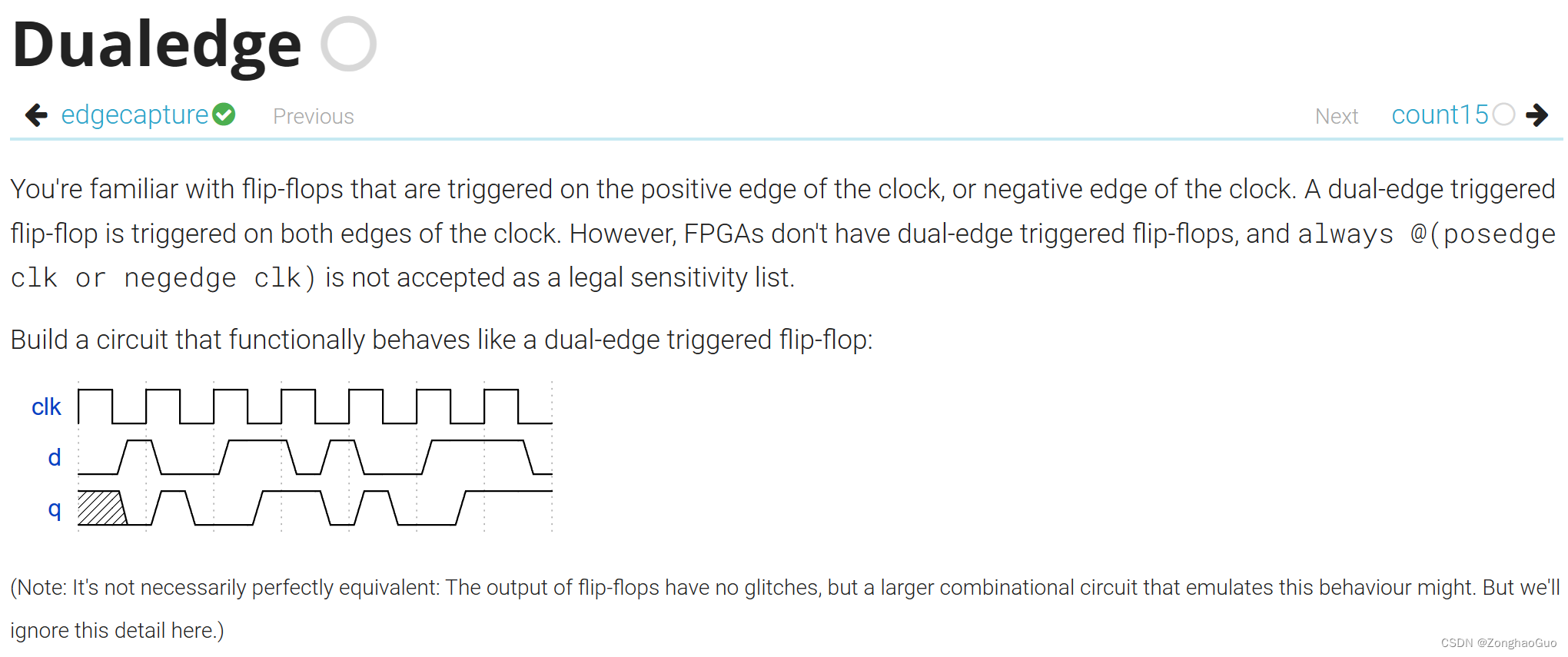

Dualedge

module top_module(

input clk,

input d,

output q);

reg p, n;

// A positive-edge triggered flip-flop

always @(posedge clk)

p <= d ^ n;

// A negative-edge triggered flip-flop

always @(negedge clk)

n <= d ^ p;

// Why does this work?

// After posedge clk, p changes to d^n. Thus q = (p^n) = (d^n^n) = d.

// After negedge clk, n changes to d^p. Thus q = (p^n) = (p^d^p) = d.

// At each (positive or negative) clock edge, p and n FFs alternately

// load a value that will cancel out the other and cause the new value of d to remain.

assign q = p ^ n;

// Can't synthesize this.

/*always @(posedge clk, negedge clk) begin

q <= d;

end*/

endmodule

Q: 给我分析一下这个运算q = (p^n) = (d^n^n) = d

A:这个表达式中使用了三个变量:p、n和d。让我们逐步分析这个运算。

首先,我们有一个操作符^n,表示按位异或(XOR)操作。这意味着对于两个二进制位的比较,如果两个位不同,则结果为1;如果两个位相同,则结果为0。

接下来,表达式中的d^n^n可以被简化为d^0,因为任何值与0进行异或操作都会保持不变。

在这种情况下,d^0等于d本身。换句话说,对于任何二进制数d,与0进行异或操作的结果仍然是d。

因此,根据这个运算,我们可以得出结论:q等于d。无论p和n的值如何,最终的结果都是d。

Q:再给我分析一下这个运算q = (p^n) = (p^d^p) = d

A:根据给定的表达式,我们有q = (p^n)。其中,^ 表示按位异或(XOR)操作。

现在,我们要用等价的方式重写这个表达式。根据异或操作的性质,abc 可以被解释为 a^(b^c) 或 (a^b)^c。这意味着我们可以对这个表达式进行括号的重组,而不改变结果。

所以,我们可以重写 q = (p^n) 为 q = (p^d^p)。在这个表达式中,我们仍然使用了异或操作,并且括号的位置发生了变化。

接下来,我们要重新审视括号内的表达式 (p^d^p)。

根据异或操作的性质,a^a 的结果总是等于 0。因此,p^p 的结果是 0。我们可以将表达式 (p^d^p) 简化为 (0^d) 或者简单地写为 d。

所以,根据这个运算,我们可以得出结论:q 等于 d,无论 p 和 d 的值如何,最终的结果都是 d。

Count15

这儿使用阻塞赋值和非阻塞赋值结果都一样。?

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @(posedge clk)

begin

if(reset==1|q==4'b1111)

q<=0;//q=0;

else

q<=q+1; //q=q+1;

end

endmodule

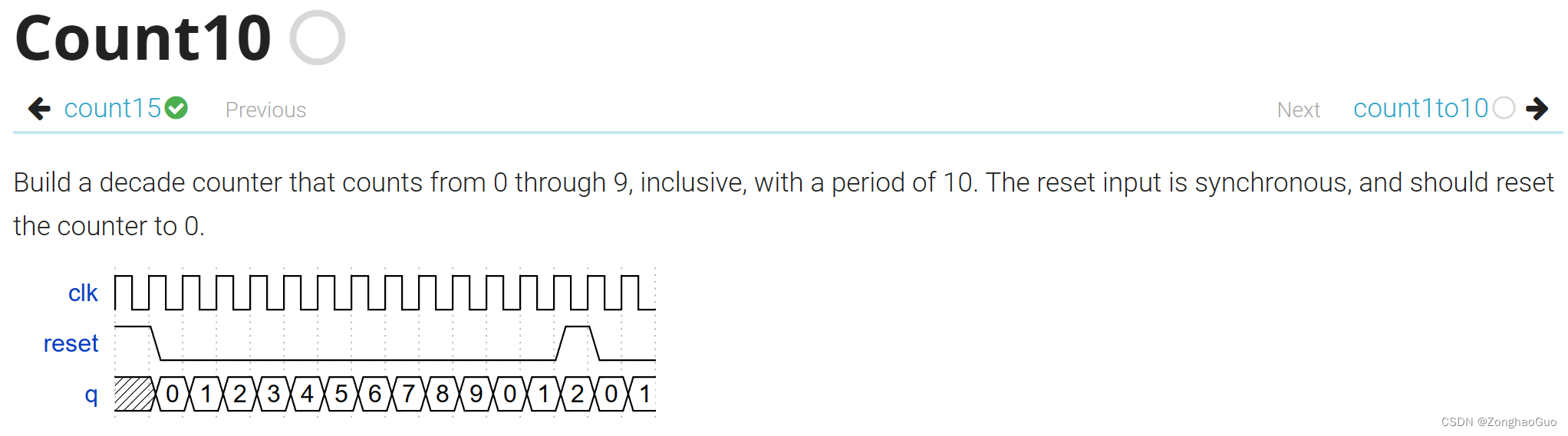

Count10

与16进制没啥区别,就是置零条件改成q=4'b1001

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @(posedge clk)

begin

if(reset==1|q==4'b1001)//与16进制相比唯一的改动

q=0;

else

q=q+1;//且按理说都应该使用非阻塞赋值,因为q为rag类型

end

endmodule

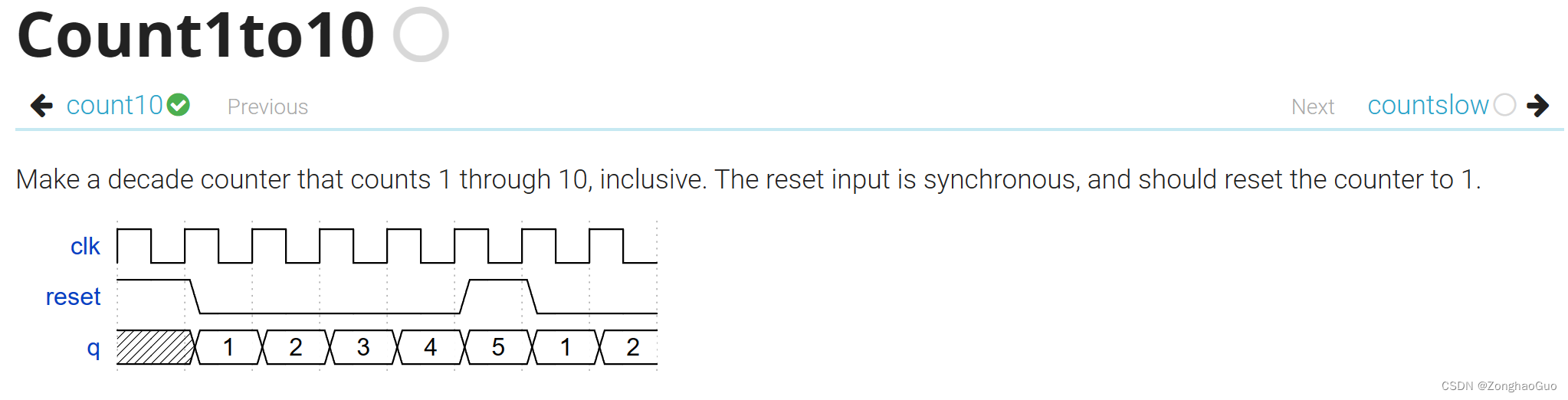

Count1to10

和前几个题没啥区别,只是从1记到10

module top_module (

input clk,

input reset,

output [3:0] q);

always @(posedge clk)

begin

if(reset==1|q==4'b1010)

q<=1;

else

q<=q+1;

end

endmodule

Countslow

module top_module (

input clk,

input slowena,

input reset,

output [3:0] q);

always @(posedge clk)

begin

if(reset==1)

q=0;

else if(slowena == 1)

begin

q=q+1;

if(q==10)

begin

q=0;

end

else

q=q;

end

else

q=q;

end

endmodule

代码分析:利用了阻塞赋值的特点,这样剑走偏锋了,虽然也能测试通过,但总归不是正途。下面展示利用非阻塞赋值完成测试的代码:

module top_module (

input clk,

input slowena,

input reset,

output [3:0] q);

always @(posedge clk)

begin

if(reset==1)

q=4'd0;

else if(slowena == 1)

begin

if(q==4'd9)

begin

q<=4'd0;

end

else

q<=q+1;

end

end

endmodule

代码分析:假设当前q=9,当下一个slowena为1时,才会将q置零。也就是说第10个slowena 到来时才会将q置零。

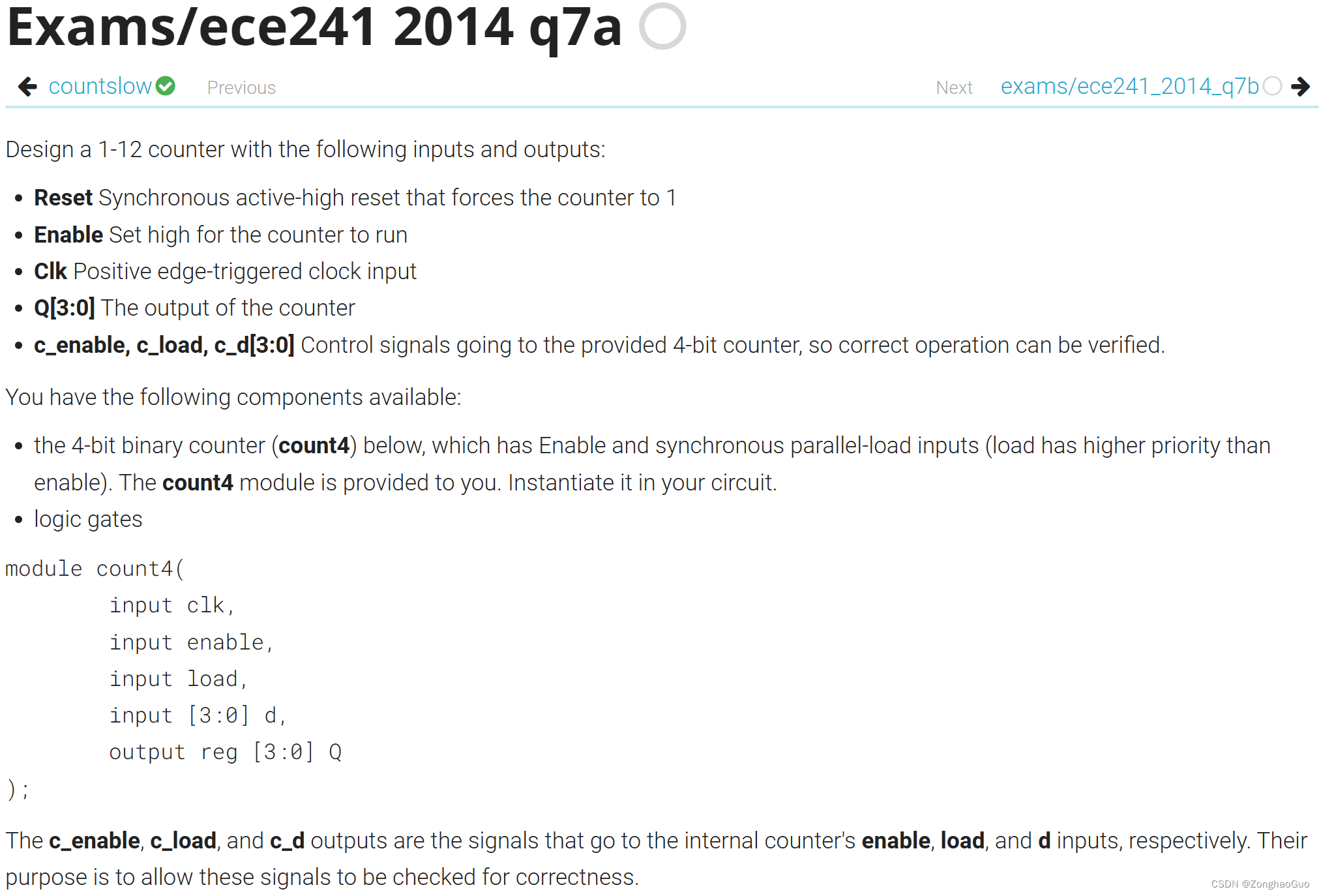

Exams/ece241 2014 q7a

需求分析:

1.系统已经提供了一个计数器,我们需要在reset=1时重加载计数器load=1

2.需要在计数器记满时,重加载计数器即load=1且重加载为1.为什么是1呢?

因为此计数器计数范围为1-12.

3.我们再看一下系统提供的module count4模块

module count4(

input clk,//不多解释 时钟

input enable,//记数使能 run使能

input load,//重加载使能

input [3:0] d,//重加载数 inatial 此题中 inatial d=1

output reg [3:0] Q

);

分析了上述功能需求那么理解起来下面的代码也就非常轻松了

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

);

assign c_enable = enable;

assign c_load = reset || ((Q == 4'd12) && (enable == 1'b1));

assign c_d = c_load ? 4'd1 : 4'dx;

count4 instance1(.clk(clk), .enable(c_enable), .load(c_load), .d(c_d), .Q(Q));

endmodule

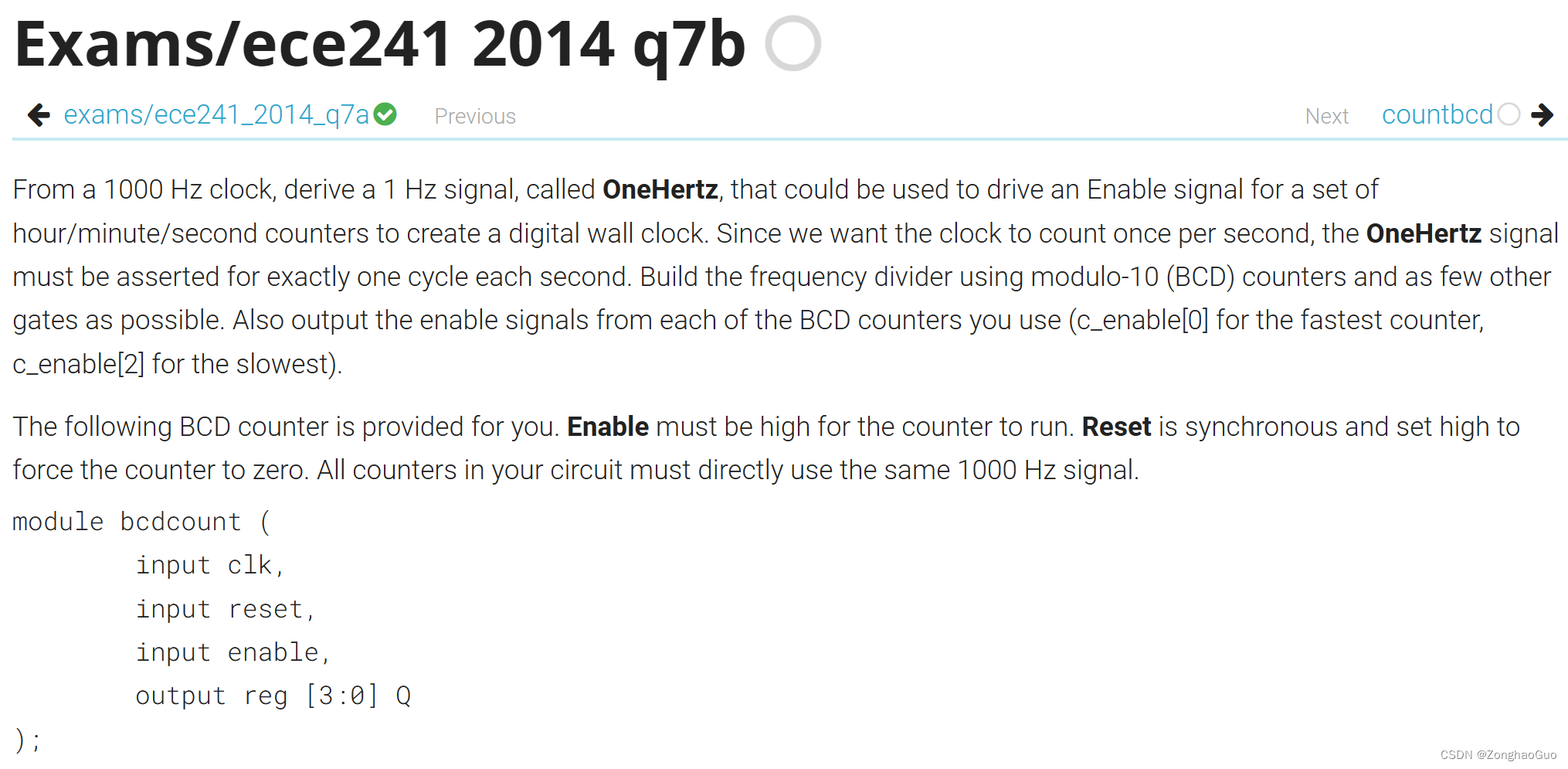

Exams/ece241 2014 q7b

翻译:从一个1000 Hz的时钟中,派生出一个1 Hz的信号,称为OneHertz,用于驱动一组小时/分钟/秒计数器,以创建一个数字墙钟。由于我们希望时钟每秒计数一次,所以OneHertz信号必须每秒钟的一个周期内被置为高电平。使用模-10(BCD)计数器构建频率分频器,并尽量使用较少的其他门电路。同时,输出你使用的每个BCD计数器的使能信号(最快计数器的c_enable[0],最慢计数器的c_enable[2])。以下是提供给你的BCD计数器。使能必须为高电平,计数器才能运行。复位信号是同步的,当置为高电平时,将强制计数器归零。你的电路中的所有计数器必须直接使用相同的1000 Hz信号。

需求分析:就是构建一个分频器,将1000hz的频率降低为1Hz.并且系统提供了bcd计数器,可以记录16个数。这样的话使用三个BCD计数器,每个计数器重加载数位9,即记录0-9,10个数,这样三个bcd计数器就可以实现1000倍分频。

需要注意的是BCDcounter是一个十进制计数器,因此它只能计数0-9在第十个clk到来时,就会清零,此时第一个计数器和第二个计数器同时启动,在第10个clk上升沿到来后计数器同时输出0,同理,当第一个第二个计数器同时到达9后,第三个计数器启动,然后三个计数器同时计数,知道计数器123均为9,此时代表进行了1000个时钟周期,

module top_module (

input clk,

input reset,

output OneHertz,

output [2:0] c_enable

); //

/*

代码分析:为什么always @(*) begin中用的是*而不是posedge呢

因为:真正与clk相连接的是计数器,需要用到时钟线,而top_module只是进行了reset信号的发生,以及判断是否使能下一个计数器,与时钟线相关的均在计数器中

疑问:当第三个计数器全都记满之后会发生什么呢?

按理说,所有计数器应该从新计数,先启动第一个计数器,再启动第二个计数器,再启动第三个计数器,让我们看看代码分析一下是这样的吗。

答:还真是,再计数完成1000次计数后,此时c_enable[0] = 1'b1;再次运行,计数器1启动,而计数器q0==4'd9为假,故执行代码 c_enable[1] = 1'b0;计数器2不启动,因此计数器3也不会启动,开始新一轮计数。

*/

reg [3:0] q0,q1,q2;

always @(*) begin

if(reset) begin

c_enable <= 3'b000;//若reset则三个计数器的使能全为0,即不使能

end

else begin

c_enable[0] = 1'b1;//启动第一个计数器

if(q0==4'd9)

c_enable[1] = 1'b1;

else

c_enable[1] = 1'b0;

if(q1==4'd9 && q0==4'd9)

c_enable[2] = 1'b1;

else

c_enable[2] = 1'b0;

end

end

assign OneHertz = (q2==4'd9 && q1==4'd9 && q0==4'd9);

bcdcount counter0 (.clk(clk), .reset(reset), .enable(c_enable[0]),.Q(q0));

bcdcount counter1 (.clk(clk), .reset(reset), .enable(c_enable[1]),.Q(q1));

bcdcount counter2 (.clk(clk), .reset(reset), .enable(c_enable[2]),.Q(q2));

endmodule

Countbcd

问题分析:其实就是构建一个十进制计数器

代码分析:需要注意的是需要自己先构造一个十进制加法器,然后实例化4个decade_cnt ,其次思考为什么是q[3:0]==8的时候 ena[1] <= 1’b1

其实答案也很明显:下面这段代码使用了两个 posedge clk,从 q 0 = 8 q_{0}=8 q0=8->ena=1需要一个时钟周期,从ena=1-> q 1 = 1 q_{1}=1 q1=1又需要一个时钟周期,因此要想在两个周期后 q 1 = 1 q_{1}=1 q1=1,需要在 q 0 = 8 q_{0}=8 q0=8时就启动ena=1

与之相比第二段代码就可以在 q 0 = 9 q_{0}=9 q0=9的时候启动高位计数器,因为没有发出启动指令的这个步骤,它的高位计数器启动直接读取地位计数器的值,只需要一个周期即可完成启动和+1的代码。

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

always @(posedge clk) begin

if (reset)

ena <= 3'b0;

else begin

if (q[3:0]==4'd8)//需要思考的是为什么在q[3:0]==8的时候 ena[1] <= 1'b1 答案是:由于使用了两个posedge clk,

ena[1] <= 1'b1;//则下个周期会是00 而不是10 所以要提前计数一个周期

else

ena[1] <= 1'b0;

if (q[3:0]==4'd8 && q[7:4]==4'd9)

ena[2] <= 1'b1;

else

ena[2] <= 1'b0;

if (q[3:0]==4'd8 && q[7:4]==4'd9 &&q[11:8]==4'd9)

ena[3] <= 1'b1;

else

ena[3] <= 1'b0;

end

end

decade_cnt cnt0(clk,reset,1'b1,q[3:0]);

decade_cnt cnt1(clk,reset,ena[1],q[7:4]);

decade_cnt cnt2(clk,reset,ena[2],q[11:8]);

decade_cnt cnt3(clk,reset,ena[3],q[15:12]);

endmodule

module decade_cnt (

input clk,

input reset,

input enable,

output [3:0] q

);

always @(posedge clk) begin

if (reset)

q <= 4'b0;

else if (enable) begin

if (q==4'd9)

q <= 4'b0;

else

q <= q+1'b1;

end

else

q <= q;

end

endmodule

与上述代码相比此代码就简单易懂许多,因为只使用了一个

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

//one

count Inst1_count

(

.clk(clk),

.reset(reset),

.ena(1'b1),

.q(q[3:0])

);

//ten

count Inst2_count

(

.clk(clk),

.reset(reset),

.ena(q[3:0] == 4'd9),

.q(q[7:4])

);

//hundred

count Inst3_count

(

.clk(clk),

.reset(reset),

.ena(q[7:4] == 4'd9 && q[3:0] == 4'd9),

.q(q[11:8])

);

//thousand

count Inst4_count

(

.clk(clk),

.reset(reset),

.ena(q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9),

.q(q[15:12])

);

//用来表示进位

assign ena = {q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9, q[7:4] == 4'd9 && q[3:0] == 4'd9, q[3:0] == 4'd9};

endmodule

module count

(

input clk,

input reset,

input ena,

output reg[3:0] q

);

always @ (posedge clk)

begin

if(reset)

q <= 4'b0;

else if (ena)

begin

if(q == 4'd9)

q <= 4'd0;

else

q <= q + 1'b1;

end

end

endmodule

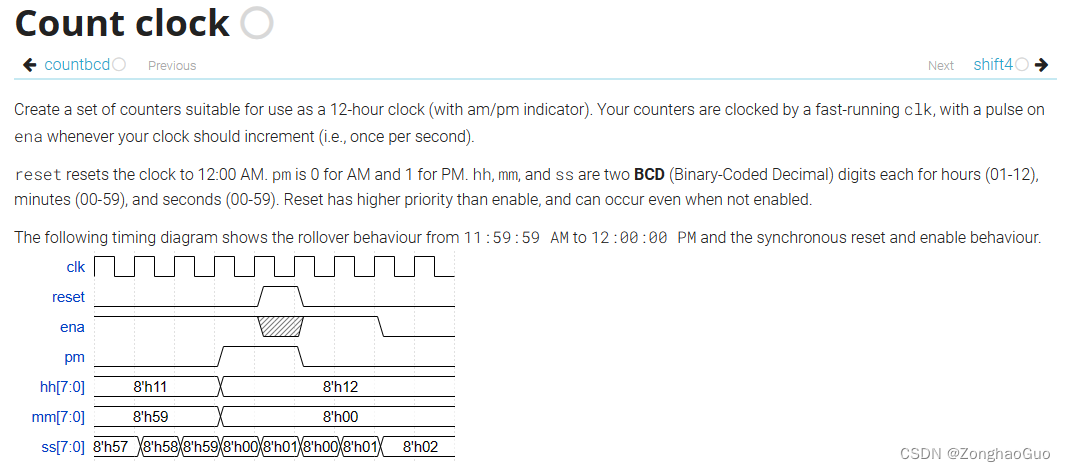

Count clock

不得不说这个题有点难度

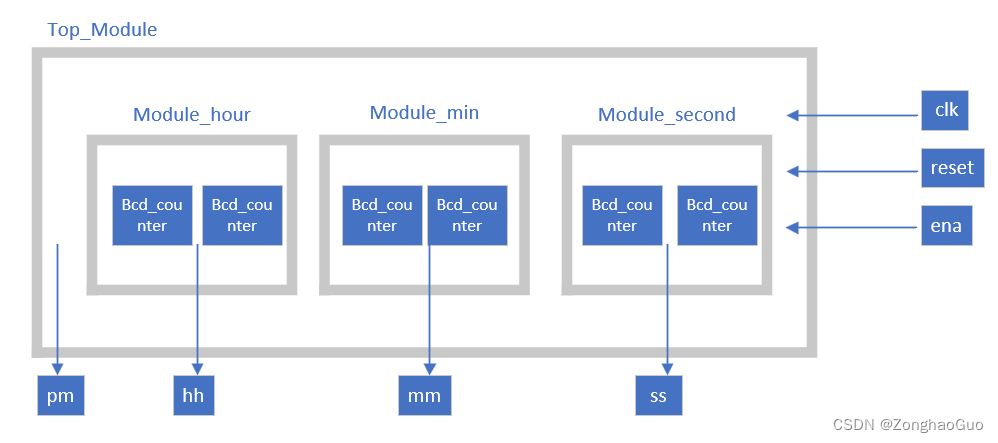

下面就是我的大体思路,秒分时模块各由两个BCD模块构成,分别组成个位和十位

看了详细解答思路和我是一致的,但他在细节处理上比我更好。

让我们看看代码:

module top_module(

input clk,

input reset,

input ena,

output reg pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss

);

wire ss_en,mm_en,hh_en;

assign ss_en = ena;

assign mm_en = ss_en&(ss == 8'h59);

assign hh_en = mm_en&(mm == 8'h59);

mm_ss u0_mm_ss(clk,reset,ss_en,ss);

mm_ss u1_mm_ss(clk,reset,mm_en,mm);

hh u_hh(clk,reset,hh_en,hh);

always@(posedge clk)begin

if(reset)

pm <= 1'b0;

else begin

if((hh == 8'h11)&(mm == 8'h59)&(ss == 8'h59)) //当12:00:00翻转pm

pm <= ~pm;

else

pm <= pm;

end

end

endmodule

//时模块

module hh(

input clk ,

input reset,

input en ,

output [7:0] hh

);

wire [3:0] counter1,counter0;

assign hh = {counter1,counter0};

h0_bcdcounter u_h0_bcdcounter(clk,reset,en,counter1,counter0);

h1_bcdcounter u_h1_bcdcounter(clk,reset,(en&((hh==8'h12)|(counter0==4'h9))),counter1);//当九点或十二点使能来时,翻转时十位;

endmodule

//分秒模块

module mm_ss(

input clk ,

input reset,

input en ,

output [7:0] mm_ss

);

wire [3:0] counter1,counter0;

assign mm_ss = {counter1,counter0};

bcdcounter u0_bcdcounter(clk,reset,en,4'h0,4'h9,counter0);

bcdcounter u1_bcdcounter(clk,reset,(en&(counter0==4'h9)),4'h0,4'h5,counter1);

endmodule

//这个BCD计数器的设计是我认为的亮点之一,尤其是增加了重加载输入,input [3:0] loadtnum,可以有效的通过外部调节循环数值

//bcd码计数

module bcdcounter(

input clk ,

input reset ,

input en ,

input [3:0] resetnum, //这里设置本来想时也可以例化这个,结果发现不可以

input [3:0] loadtnum,

output reg [3:0] counter

);

always@(posedge clk)begin

if(reset)

counter <=resetnum;

else begin

if(en)begin

if(counter == loadtnum)

counter <= 4'h0;

else

counter <= counter + 1'b1;

end

else

counter <= counter;

end

end

endmodule

//时个位

module h0_bcdcounter(

input clk ,

input reset ,

input en ,

input [3:0] h1 ,

output reg [3:0] counter

);

always@(posedge clk)begin

if(reset)

counter <=4'h2;

else begin

if(en)begin

if(counter == 4'h9)

counter <= 4'h0;

else if((h1==4'h1)&(counter == 4'h2)) //当12点使能来时,将时个位置1

counter <= 4'h1;

else

counter <= counter + 1'b1;

end

else

counter <= counter;

end

end

endmodule

//时十位

module h1_bcdcounter(

input clk ,

input reset ,

input en ,

output reg [3:0] counter

);

always@(posedge clk)begin

if(reset)

counter <=4'h1;

else begin

if(en)begin

if(counter == 4'h1)

counter <= 4'h0;

else

counter <= counter + 1'b1;

end

else

counter <= counter;

end

end

endmodule

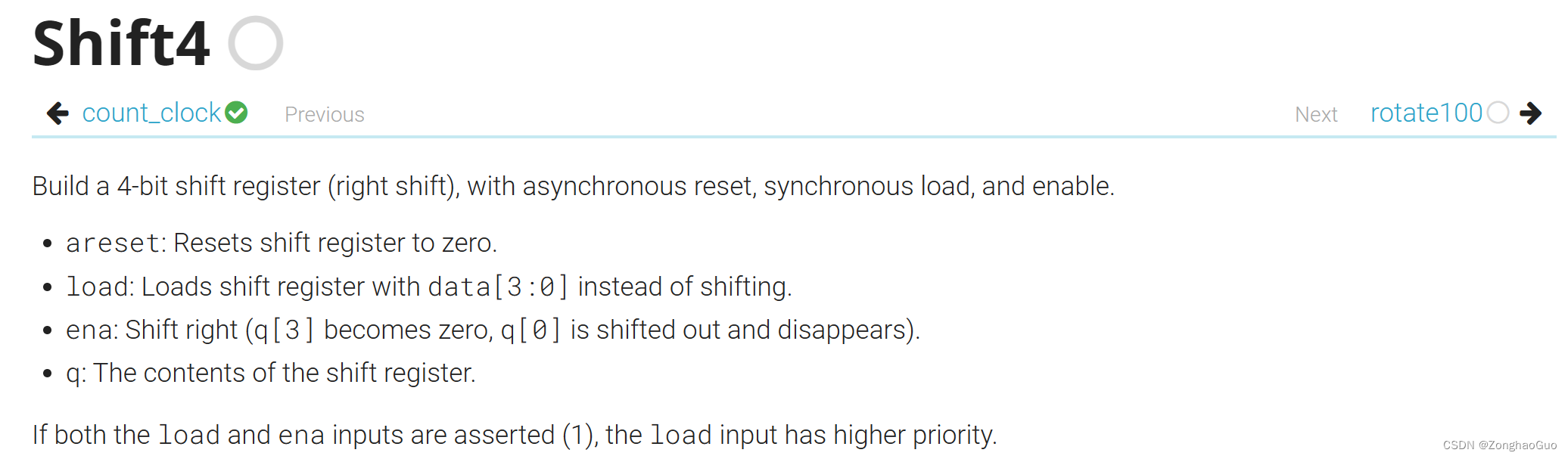

Shift4

这个题比较简单,就是构建一个4位的移位寄存器

构建一个4位移位寄存器(向右移位),具有异步复位、同步加载和使能功能。

areset:将移位寄存器复位为零。

load:用数据[3:0]加载寄存器,而不进行移位。

ena:向右移位(q[3]变为零,q[0]被移出并消失)。

q:移位寄存器的内容。

如果load和ena输入都为1,则load输入具有较高的优先级。

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always@(posedge clk or posedge areset)begin

if(areset==1)

q<=4'b0000;

else if(load && ena)

q <= data;

else if(load==1)

q <= data;

else if(ena==1)

q <= {1'b0, q[3:1]};

end

endmodule

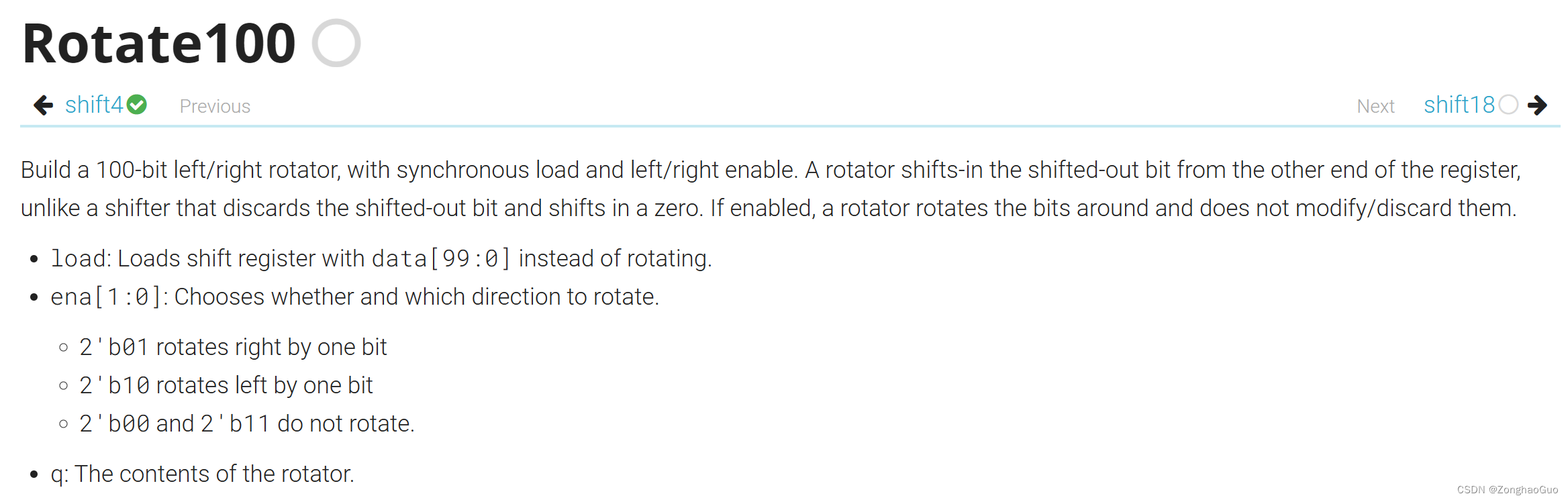

Rotate100

这个题也非常简单,直接上代码

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always@(posedge clk)begin

if(load==1)

q<=data;

else if(ena==2'b01)

q <= {q[0],q[99:1]};

else if(ena==2'b10)

q <= {q[98:0],q[99]};

else if(ena==2'b00|ena==2'b11)

q <= q;

end

endmodule

Shift18

这个题呢,很简单,但是我一开始犯了一个小错误,

一开始用的或运算符ena==1|amount==2'b00,那这不是开玩笑吗,当时肯定是想别的了

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always@(posedge clk)begin

if(load==1)

q<=data;

else if(ena==1&amount==2'b00)//左移1位

q <= {q[62:0],1'b0};

else if(ena==1&amount==2'b01)//左移8位

q <= {q[55:0],{8{1'b0}}};

else if(ena==1&amount==2'b10)//右移1位

q <= {q[63],q[63:1]};

else if(ena==1&amount==2'b11)//右移8位

q <= {{8{q[63]}},q[63:8]};

end

endmodule

Lfsr5

确实,本质上就是一个移位寄存器,只不过某些触发器的输入不是上一级的输出,而是和其他触发器进行了异或操作。

复习:任何数与0异或则为它本身,与1异或则为取反操作

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg [4:0] q

);

always@(posedge clk) begin

if(reset) q <= 5'h1;

else begin

q[4] <= q[0];

q[3] <= q[4];

q[2] <= q[3]^q[0];

q[1] <= q[2];

q[0] <= q[1];

q <= {q[0],q[4],q[3]^q[0],q[2:1]};

end

end

endmodule

Mt2015 lfsr

我服了,本来很简单的一道题,几分钟完事,可我把r_in(SW[0])前面的点给遗忘了。想了好长时间,感觉逻辑也没问题,服了。

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

//实例化三个带二路选择器的D触发器

dfft ins0(.clk(KEY[0]), .L(KEY[1]), .r_in(SW[0]), .q_in(LEDR[2]), .Q(LEDR[0]));

dfft ins1(.clk(KEY[0]), .L(KEY[1]), .r_in(SW[1]), .q_in(LEDR[0]),.Q(LEDR[1]));

dfft ins2(.clk(KEY[0]), .L(KEY[1]), .r_in(SW[2]), .q_in(LEDR[1]^LEDR[2]),.Q(LEDR[2]));

endmodule

module dfft(

input clk,

input L,

input r_in,

input q_in,

output reg Q);

always @(posedge clk)

begin

if(L == 1'b0)

Q<=q_in;

else

Q<=r_in;

end

endmodule

Lfsr32

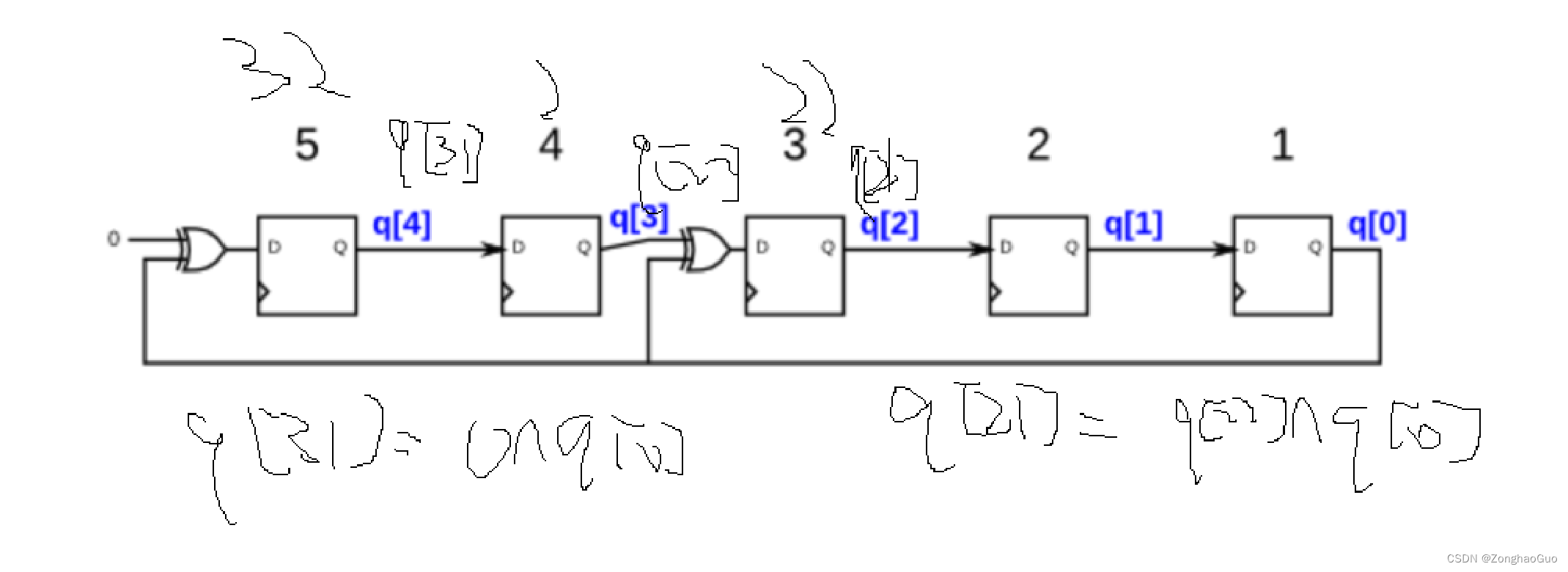

题目分析:如果触发器以下图这种方式命名的话,也就是说在触发器1,2,22,32前方各有一个异或门与q[0]相异或。那也就很好理解了,q[31]<=q[0]^0, q[21]=q[22]^0

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output [31:0] q

);

always@(posedge clk)begin

if(reset) q<=32'd1;

else q<={q[0]^1'b0,q[31:23],q[0]^q[22],q[21:3],q[0]^q[2],q[0]^q[1]};//每来一个时钟周期做一下这种运算

end

endmodule

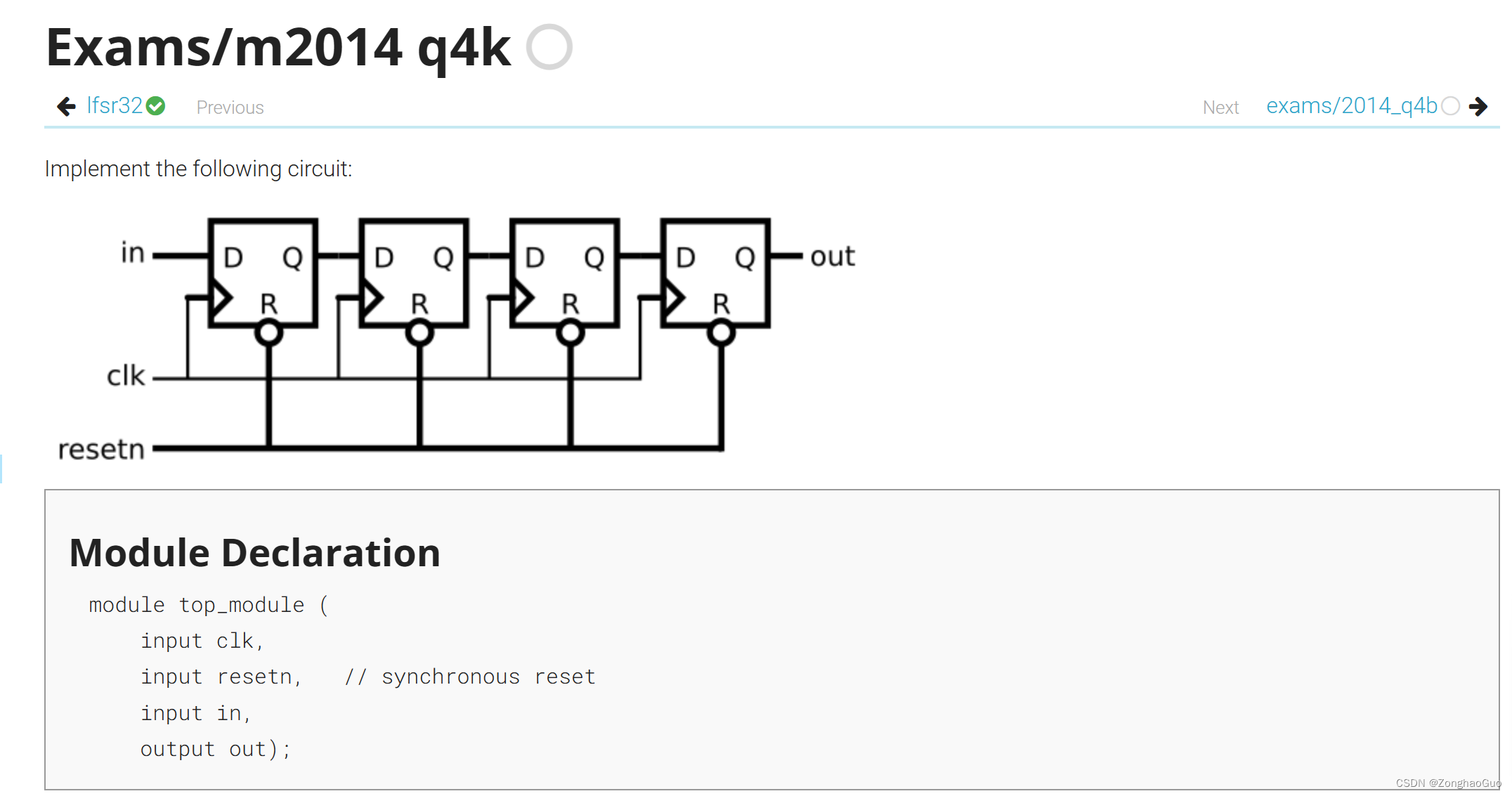

Exams/m2014 q4k

module top_module (

input clk,

input resetn, // synchronous reset

input in,

output out);

reg q0,q1,q2,q3;

//实例化4个带复位的D触发器

dfft ins4(

.clk(clk),

.rin(in),

.reset(resetn),

.Q(q3));

dfft ins3(

.clk(clk),

.rin(q3),

.reset(resetn),

.Q(q2));

dfft ins2(

.clk(clk),

.rin(q2),

.reset(resetn),

.Q(q1));

dfft ins1(

.clk(clk),

.rin(q1),

.reset(resetn),

.Q(q0));

assign out = q0;

endmodule

module dfft(

input clk,

input reset,

input rin,

output reg Q);

always @(posedge clk)

begin

if(reset == 1'b0)

Q<=0;

else

Q<=rin;

end

endmodule

Exams/2014 q4b

这个题也非常EASY,需要注意的是实例化module一定要使用它自带的名字。

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

);

wire out4, out3, out2, out1;

//实例化4个带选择器的D触发器

MUXDFF ins4(

.clk(KEY[0]),

.w(KEY[3]),

.R(SW[3]),

.E(KEY[1]),

.L(KEY[2]),

.Q(out4));

MUXDFF ins3(

.clk(KEY[0]),

.w(out4),

.R(SW[2]),

.E(KEY[1]),

.L(KEY[2]),

.Q(out3));

MUXDFF ins2(

.clk(KEY[0]),

.w(out3),

.R(SW[1]),

.E(KEY[1]),

.L(KEY[2]),

.Q(out2));

MUXDFF ins1(

.clk(KEY[0]),

.w(out2),

.R(SW[0]),

.E(KEY[1]),

.L(KEY[2]),

.Q(out1));

assign LEDR = {out4, out3, out2, out1};

endmodule

module MUXDFF(

input clk,

input w,

input R,

input E,

input L,

output Q

);

wire out1,out2;

assign out1 = (E==0) ? Q:w;

assign out2 = (L==0) ? out1:R;

always @(posedge clk)

begin

Q=out2;

end

endmodule

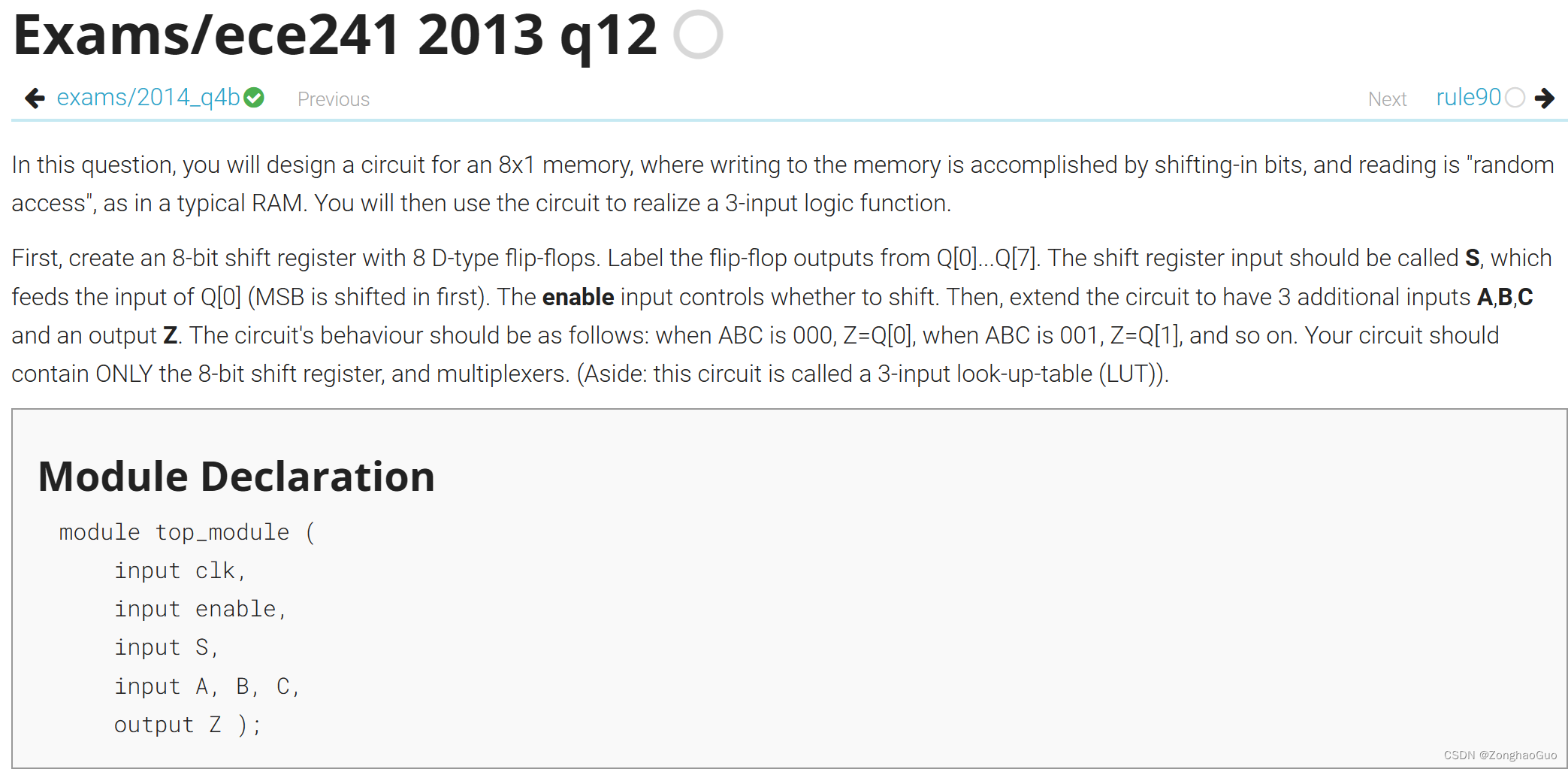

3-input look-up-table (LUT)

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output Z );

reg [7:0] q;

always @(posedge clk)begin

if(enable==1'b1)

q<={q[6:0],S};

else

begin

q<=q;

end

end

always @(*)begin

Z<=q[A*4+B*2+C*1];

end

endmodule

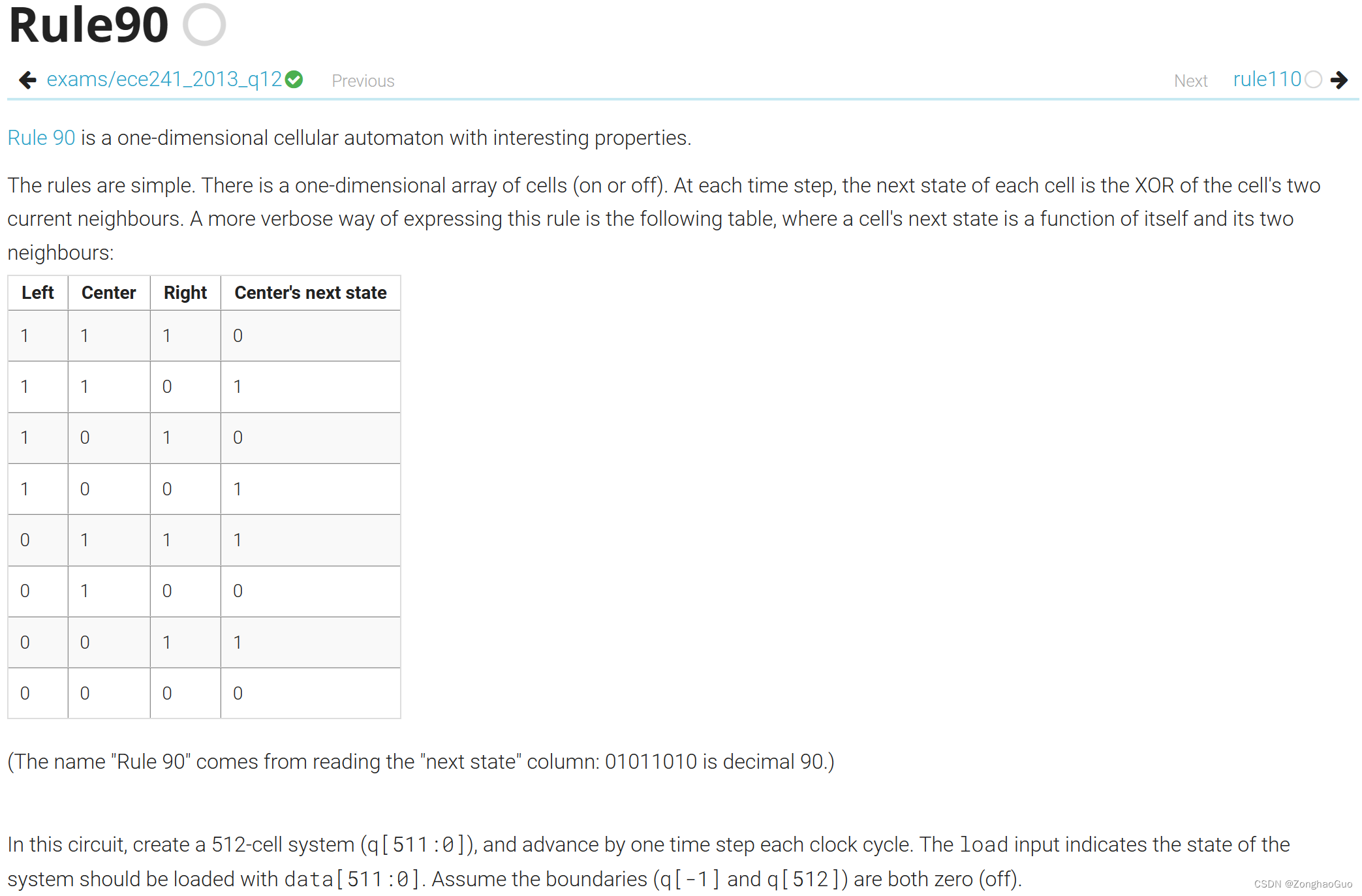

Rule90

module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q );

always @(posedge clk)begin

if(load==1'b1)

q<=data;

else begin

q[511]<=0^q[510];

q[0]<=0^q[1];

for(integer i=1;i<511;i=i+1)begin

q[i]<=q[i-1]^q[i+1];

end

end

end

endmodule

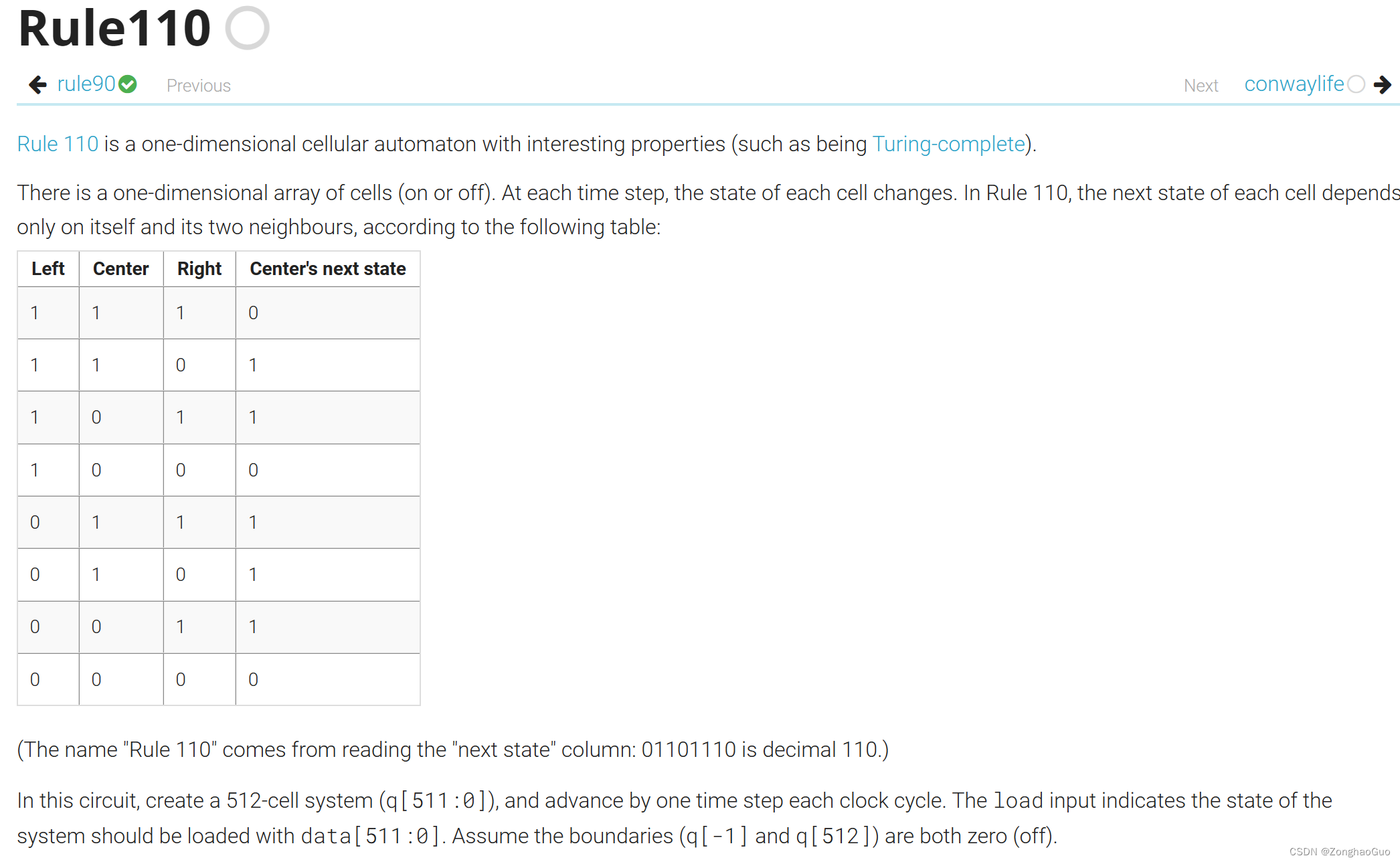

Rule110

手到擒来,太强了我【狗头】

module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q );

always @(posedge clk)begin

if(load==1'b1)

q<=data;

else begin

if((0*4+q[511]*2+q[510]*1)==0|(0*4+q[511]*2+q[510]*1)==7|(0*4+q[511]*2+q[510]*1)==4)

q[511]<=0;

else

q[511]<=1;

if((q[1]*4+q[0]*2+0*1)==0|(q[1]*4+q[0]*2+0*1)==7|(q[1]*4+q[0]*2+0*1)==4)

q[0]<=0;

else

q[0]<=1;

for(integer i=1;i<511;i=i+1)begin

if((q[i+1]*4+q[i]*2+q[i-1]*1)==0|(q[i+1]*4+q[i]*2+q[i-1]*1)==7|(q[i+1]*4+q[i]*2+q[i-1]*1)==4)

q[i]<=0;

else

q[i]<=1;

end

end

end

endmodule

Conwaylife

这题没啥难度,就是费点功夫,现在时不我待,等有机会了回来看看

happy happy happy happy happy

happy happy happy happy happy

null

2249

2249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?