基于fpga的czt(chirp-z)算法实现,频谱细化算法,fpga硬件实现,平台vivado,verilog

随着计算机科学的不断发展,硬件加速算法变得越来越受到关注。特别是在信号处理领域,频谱细化算法是许多任务的关键组成部分。然而,软件实现的频谱细化算法存在计算速度慢、功耗高等问题,难以满足实时应用需求。因此,基于FPGA的硬件加速算法成为许多工程师的选择。

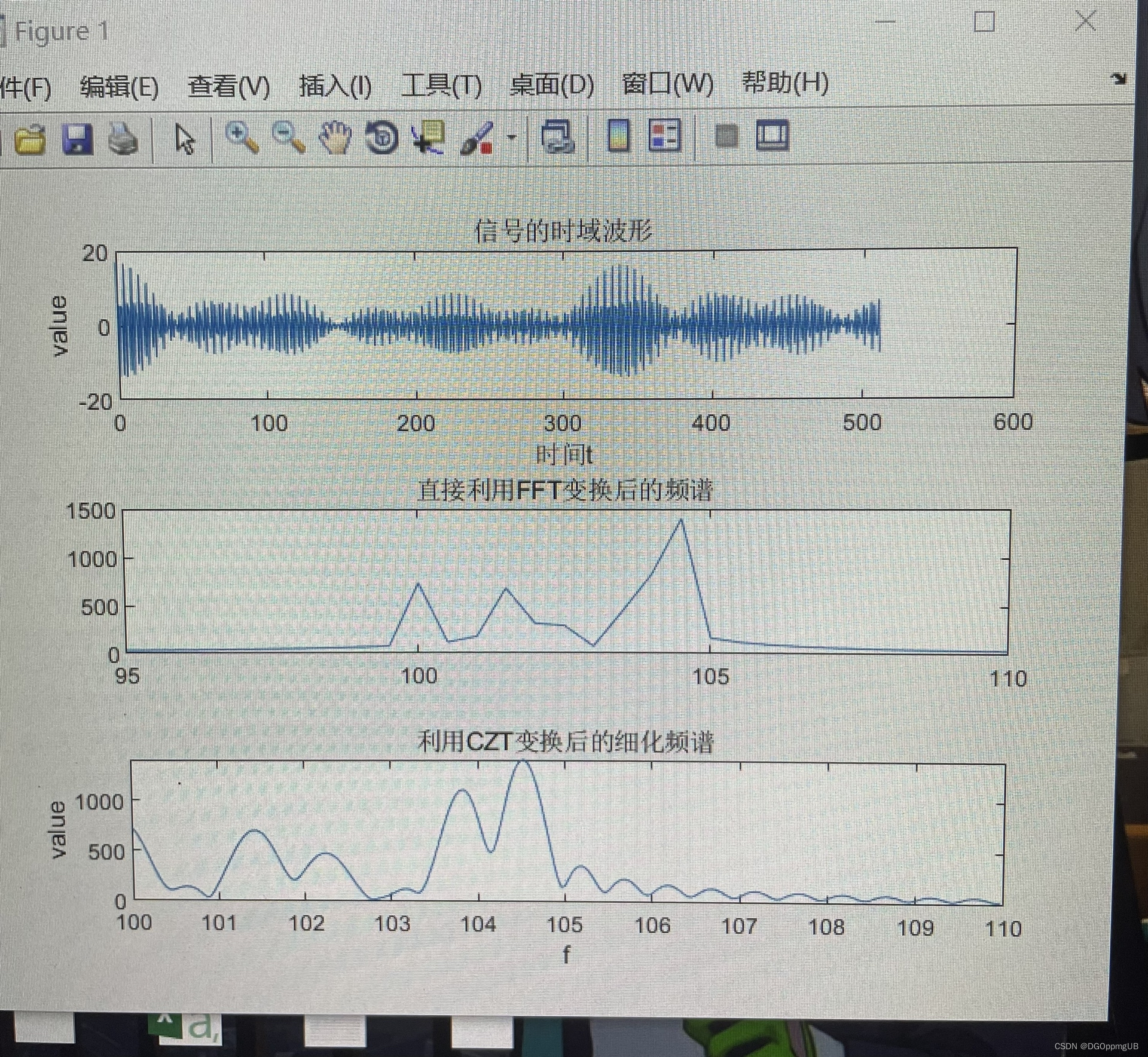

本文将讲述基于FPGA的CZT(Chirp-Z)算法实现的频谱细化算法。其中,CZT算法是一种常用的频谱分析算法,常用于信号处理、雷达和通信等领域。该算法通过对时域序列进行DFT计算,得到其频域信息。与传统的DFT算法不同,CZT算法通过引入Chirp信号,使得算法的计算量大幅减少,计算速度更快。

在本文中,我们将重点介绍CZT算法在FPGA硬件实现中的优化。使用Verilog语言实现,并基于平台Vivado进行开发。为了实现高效的算法,我们采用了流水线和并行化等技术。同时,我们还对算法进行了优化,如通过共享数据和缓存数据等方式来减少功耗和计算量。

为了验证算法的性能和精度,我们对比了软件算法和FPGA硬件算法的计算时间和精度。实验结果表明,基于FPGA的CZT算法实现比常规软件实现快数倍,同时计算精度也得到了保证。这种算法实现的优势在于其高效性和可扩展性,适用于需要高速信号处理的各种场景。

总之,本文介绍了基于FPGA的CZT算法在频谱细化算法中的应用。通过对硬件实现进行优化,我们实现了高效的算法,并通过实验验证了其性能和精度。这种算法实现具有广泛的应用前景,可以满足各种实时信号处理需求。

相关代码,程序地址:http://lanzouw.top/674150387969.html

本文探讨了基于FPGA的CZT算法在频谱细化中的应用,通过Vivado平台的Verilog实现,利用流水线和并行化技术优化,实现实时高速处理且保持高精度。实验结果证实了FPGA硬件的显著优势。

本文探讨了基于FPGA的CZT算法在频谱细化中的应用,通过Vivado平台的Verilog实现,利用流水线和并行化技术优化,实现实时高速处理且保持高精度。实验结果证实了FPGA硬件的显著优势。

816

816

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?