一、PCB走线阻抗及模型介绍

走线阻抗:相对参考层(地),信号受到的阻力称为特征阻抗(走线阻抗)。

均匀传输线:导线上任意处横截面都相同,这种线称为均匀传输线。所有高速互联都必须设计成均匀传输线!不允许有地平面割裂。

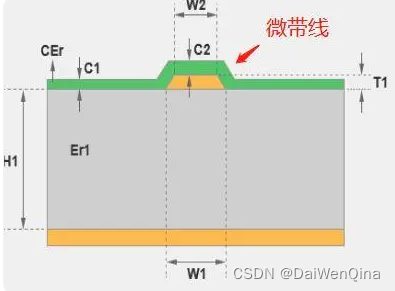

微带线:表底层走线,是指电介质基板顶部的带状导体,基板下方有接地平面。

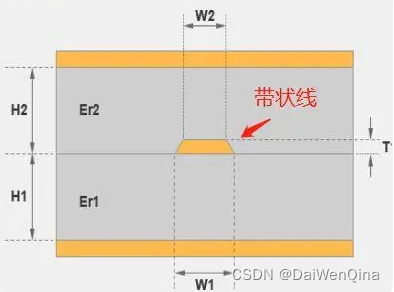

带状线:内层走线,指嵌入电介质基层内,并夹在两个接地平面之间的“带状“导体。

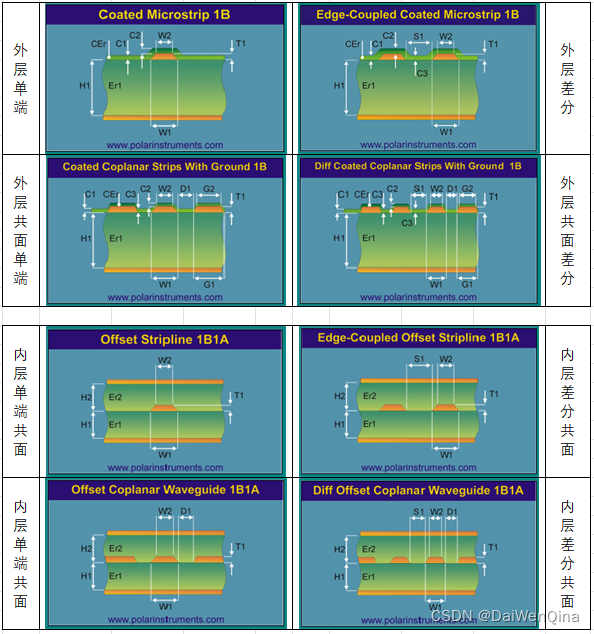

常见阻抗模型:

微带线VS带状线:

微带线制造简单,所需板层少(2、4层),但其顶部开放线场,有较强的辐射损耗和准TEM传输模式。

带状线完全包含在导电结构内,表现出真正的TEM传输模式,尽管制造昂贵和复杂(6、8层及以上),但对高速信号友好 。

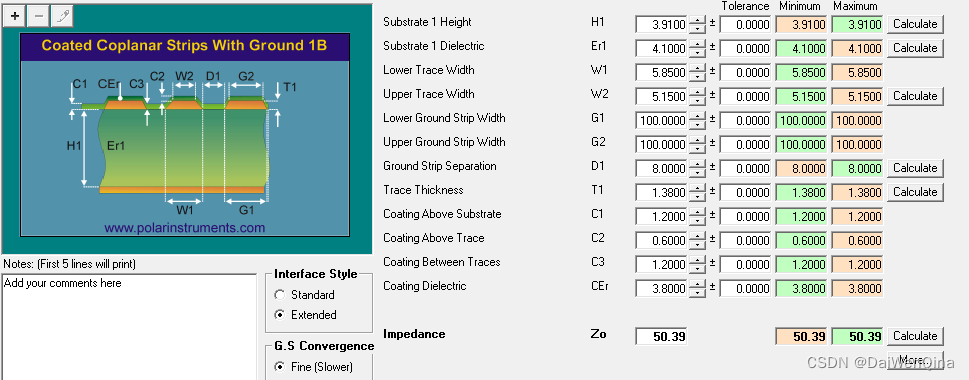

以下是根据板厂经验参数值:

阻焊油墨厚度参数(油墨介电常数3.8)

| 基材上阻焊油墨厚度C1 | 铜面上阻焊油墨厚度C2 | 导线间的阻焊油墨厚度C3 |

| 1.2mil | 0.6mil | 1.2mil |

| 线顶宽度W2=W1-0.7mil | ||

二、四层计算实例:

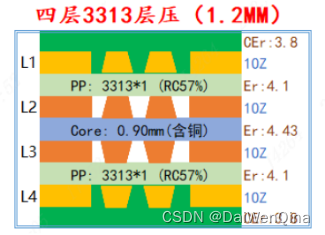

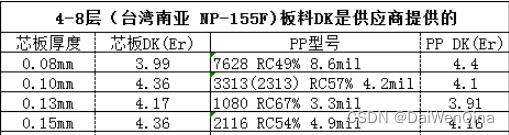

我们取3313层叠结构PP介质er值4.1(不同型号压合的pp是不同er值的,要注意!)

FR-4芯板的介质DK值取4.2-4.8(一般取4.5)。

Pp介质的引入是为了粘合板芯与层,DK随厚度浓度影响。4.2-4.5

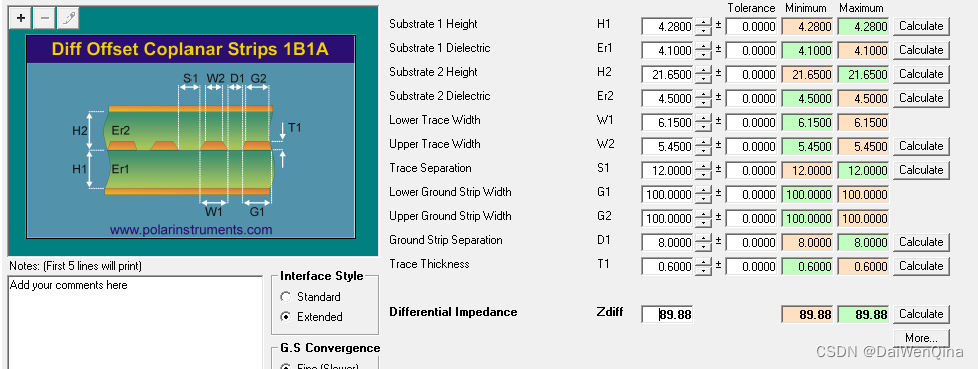

通过以上信息,进入Si9000进行验证。选择合适的参考模型与立创阻抗参数计算比较吻合。

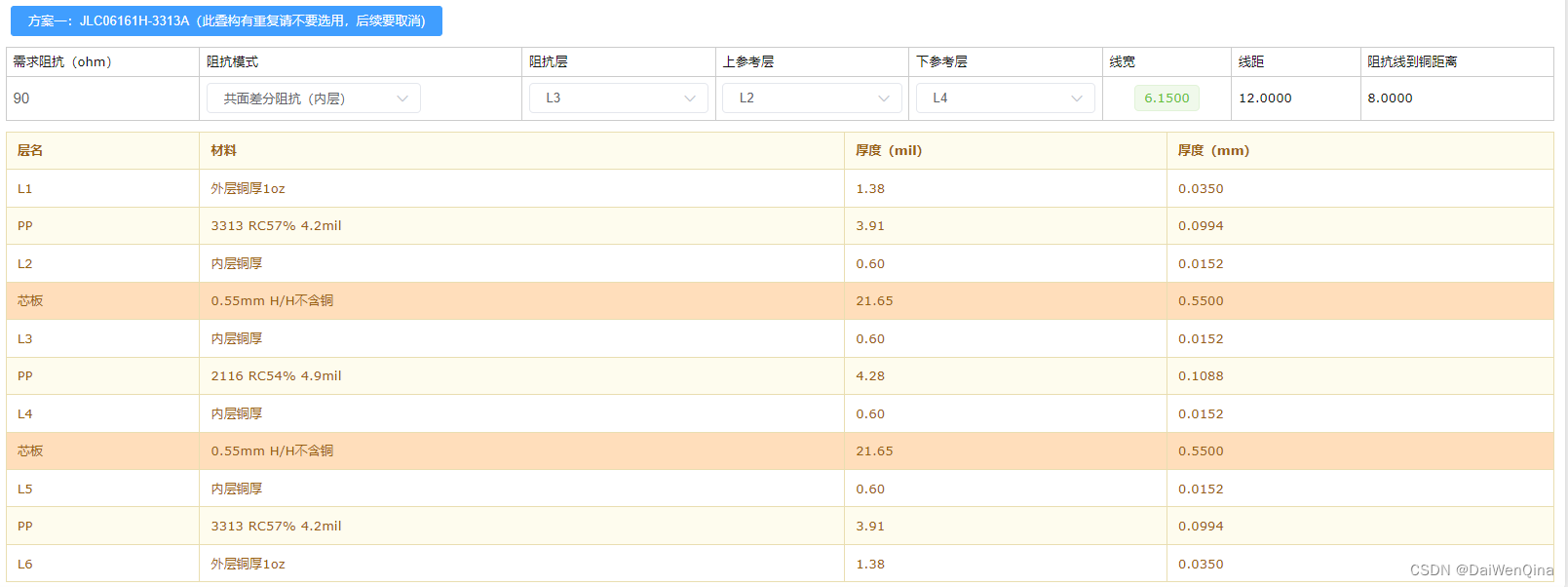

三、六层计算实例:

下面介绍一下6层走线的基本布局层叠结构以及阻抗计算。

| 层数 | 结构式1 | 结构式2 | 结构式3 |

| 第一层(顶层) | Top | Top | Top |

| 第二层 | Signal | Gnd | Gnd |

| 第三层 | Gnd | Signal | Signal |

| 第四层 | Power | Signal | Gnd |

| 第五层 | Signal | Power | Power |

| 第六层(底层) | Bottom | Bottom | Bottom |

1.结构形式1

结构形式1组成:有4个信号层,1个GND层,1个电源层。

这种结构电源层/GND层采用小间距结构,可以提供较低的电源阻抗,这个低阻抗特性可以改善电源的退耦效果。第1层和第6层是较差的布线层,不适合放射频能量的走线。第2层是最好的布线层,靠近GND层,可以放射频能量的线条。第5层也可以作为其他风险高的布线层,第1层和第二层,第5层和第6层采用交叉布线。

2.结构形式2

结构形式2组成:4个信号层,1个电源层,1个GND层。

这种结构电源层与GND层有两个信号层,电源层与GND层不存在任何退耦作用,第3层是最好的布线层,第1层,第4层,第6层是可布线层。这种层间安排布线层阻抗低,可以满足信号完整性要求,另外参考平面层对射频也有屏蔽作用。

2.结构形式3

结构形式3组成:3个信号层,1个电源层,2个GND层。

当有太多的印制线条布放,但又无法安排4个布线层时,可以采用这种结构形式。在这个结构形式,将一个信号层变成GND层可以获得较低的传输线阻抗。第2层和第3层采用小间距的结构,可以提供较低的电源阻抗,这个低阻抗特性可以改善电源的退耦效果。第4层是最好的布线层,时钟等高风险的线条必须在第3层,这一层构造上形成同轴传输线结构,可以保证信号完整性和对EMI能量进行抑制。顶层是次好的布线层,底层是可布线层。

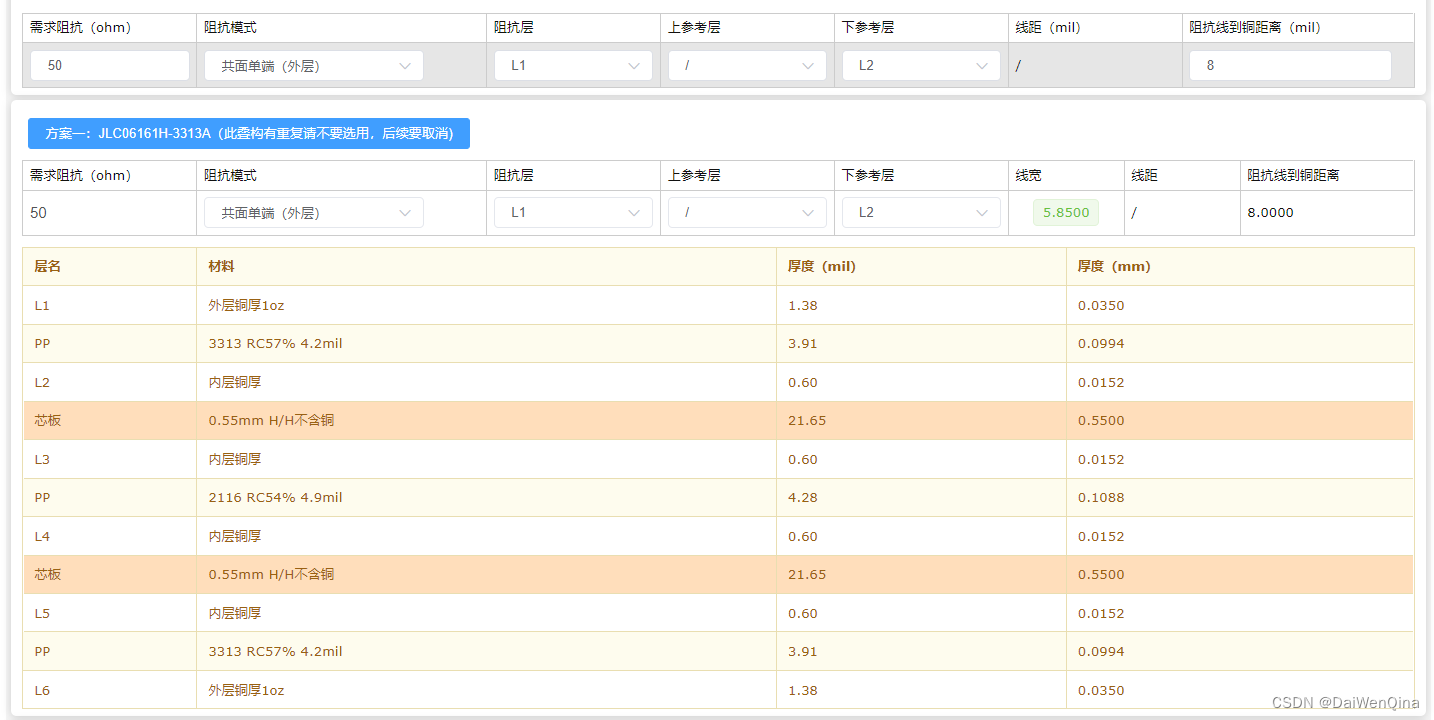

以结构三为例,走Top层共面单端50Ω,与与立创阻抗参数计算比较吻合

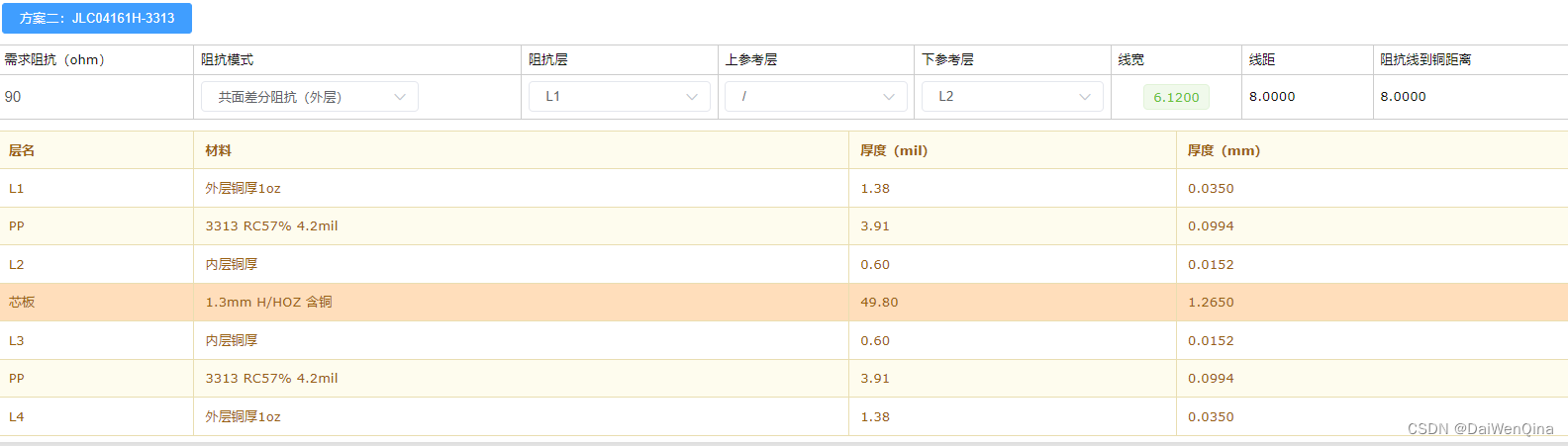

结构三第3层走线,共面差分带状线90Ω,取合适的模型与立创阻抗参数计算比较吻合

4742

4742

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?