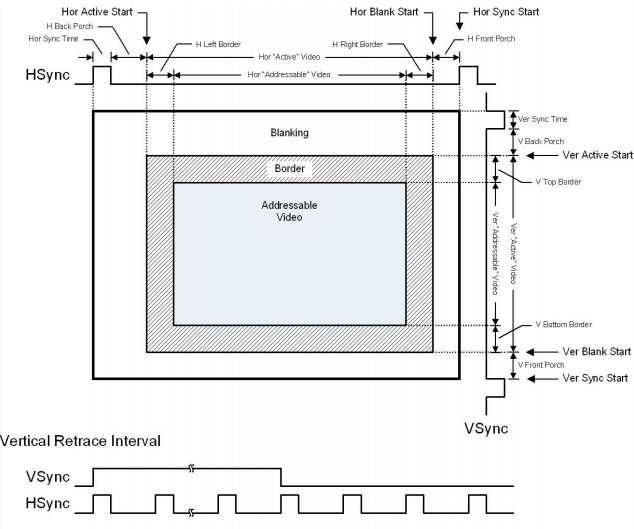

引言:在像素领域处理hsync,vsync,active,以及rgb888并行数据。因为Display Monitor Timing标准,控制信号(hsync/vsync/active)以及数据rgb888之间存在着某种特定的关系,其关系大体如下图所示:

图1 : Hsync Vsync Active 与像素之间的关系

在实际使用的过程中,像素数据需要经过buffer来缓存,逻辑设计经常使用FIFO做数据缓存,而FIFO对像素数据是有延迟的。为了达到hsync vsync与像素数据的同步,并不适合将控制信号也通过FIFO,合适的方法是将控制信号延时固定的时钟节拍,就需要有控制延时N(N>=1)个时钟节拍的逻辑控制。

下面就介绍一些关于固定时钟节拍的延时RTL实现。

方法一:触发器

当N<=2的,适合用D触发器做时钟节拍延时,这样最简便,也节省相应的逻辑资源。

input d,

output q,

input clk,

input rst_n

reg q_t;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

q_t <= 1'b0;

else

q_t <= d;

end

assign

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

480

480

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?