在图像拼接的工程中,前端相机生成图像数据,需要对图像数据进行缓存后,再根据后端标准的HDMI时序输出图像数据。在这个过程中,因为前端相机的时钟与后端HDMI输出的时钟是不相同的,为了使输出的图像没有像素丢失,所以需要将相机图像先进行缓存,然后输出。对于高清图像,一帧图像所占用的存储空间比较大,单独依靠Xilinx器件内部的RAM是无法完成工作的,因为FPGA内部的RAM在级联以后对于布局布线过程是一个极大的挑战。为了避免布局布线所带来的问题,这就需要在整体的项目设计中引入DDR3来进行数据的缓存。

开发平台

硬件平台:KC705 MT8JTF12864HZ

软件平台:ISE14.7 / Vivado 2015.4 modelsim 10.2

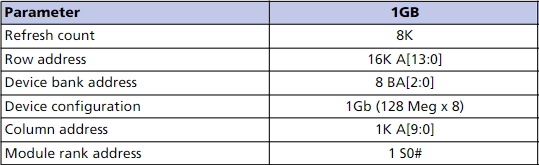

KC705开发板上所带的内存条为总存储大小为1GB的内存条,其地址空间参数如下如所示:

那么总的存储容量1GB是如何计算出来的呢?

从上图可以看出,该内存条总共包含1个RANK(S0#),8个BANK(BA[2:0]),在每一个BANK中,对应的行地址总数为16K(A[13:0]),列地址总数为1K

本文介绍了在图像拼接工程中利用DDR3进行数据缓存的必要性,以及在Xilinx KC705开发板上,基于MIG IP Core进行DDR3设计的过程。详细讲解了开发平台、DDR3内存参数、MIG IP Core的配置,并阐述了如何建立Modelsim仿真平台进行DDR3的测试与验证。

本文介绍了在图像拼接工程中利用DDR3进行数据缓存的必要性,以及在Xilinx KC705开发板上,基于MIG IP Core进行DDR3设计的过程。详细讲解了开发平台、DDR3内存参数、MIG IP Core的配置,并阐述了如何建立Modelsim仿真平台进行DDR3的测试与验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2407

2407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?