ModelSim是Mentor的子公司Medel Technology的一个出色的Verilog HDL/VHDL 混合仿真软件,它属于编译型仿真器(进行仿真前必须对HDL源码进行编译),方针速度快,功能强。

下面简单介绍一下ModelSim仿真实例教程。以BCD码加法器为例。

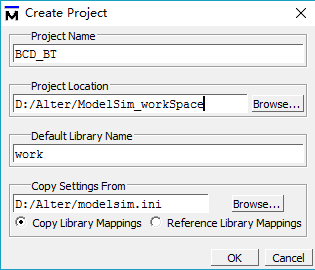

1、 启动ModelSim

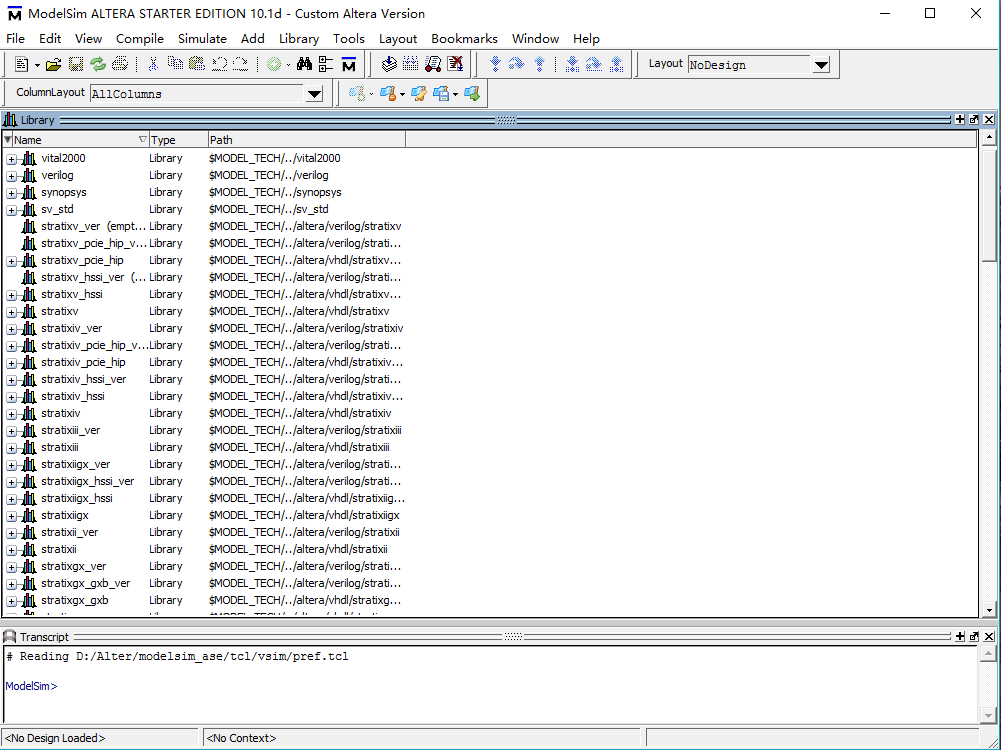

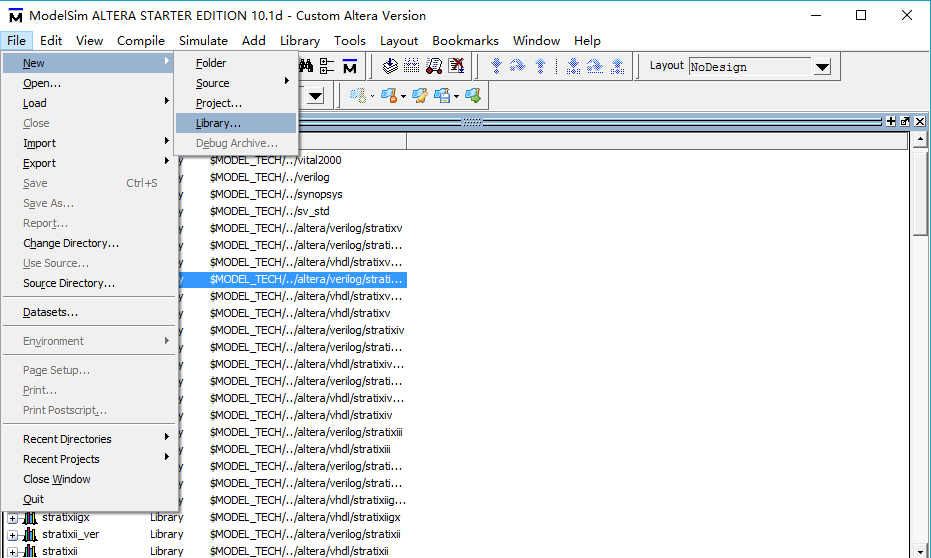

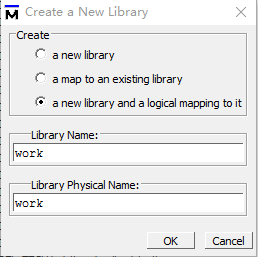

2、首次运行ModelSim时,在建立project 前,需要先建立一个工作库(library),一般将这个library命名为work,project一般都是在这个work下面工作的。

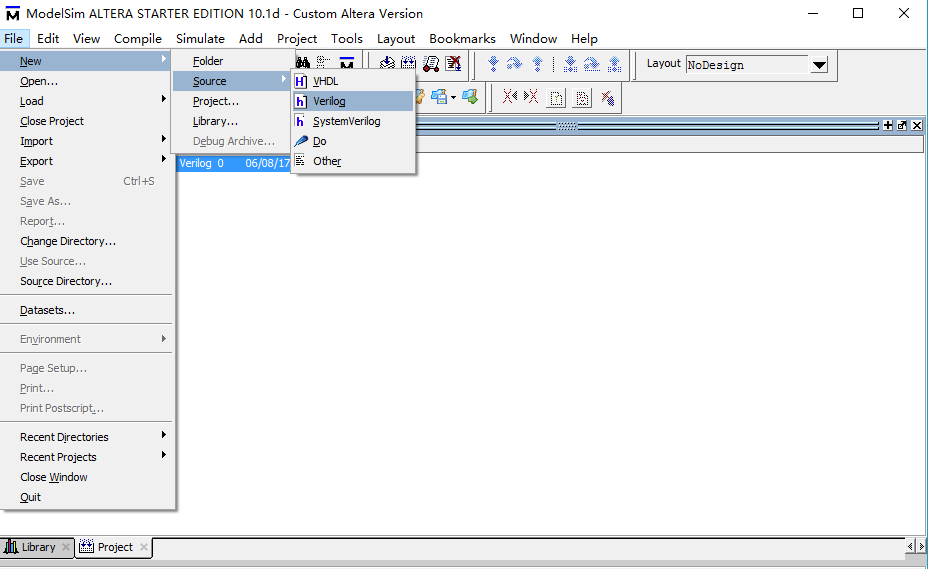

File\new\library,弹出对话框是否创建work library,点击OK创建成功。

创建界面如下图:

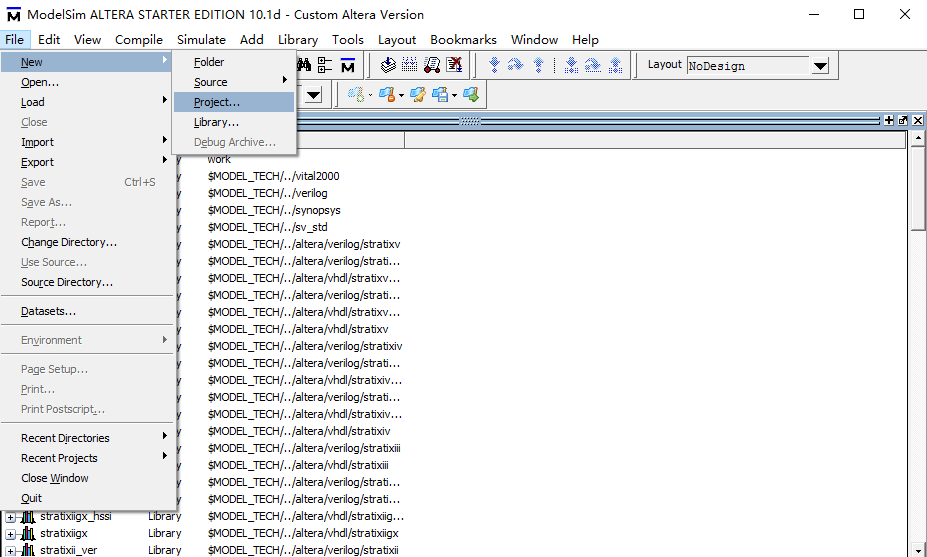

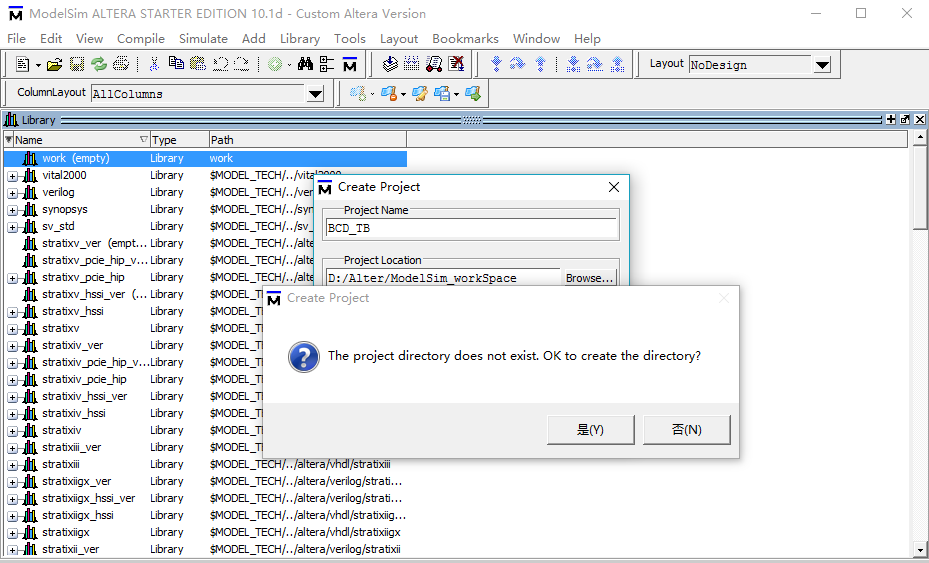

3、新建工程 File\new\project ,点击OK创建成功。

创建界面如下图:

注意 ProjectLocation 为项目存储位置,自定义创建项目存储位置文件夹为 ModelSim_workSpace ,若文件夹已存在则直接保存,若不存在,则按提示 creat 目标文件夹即可。

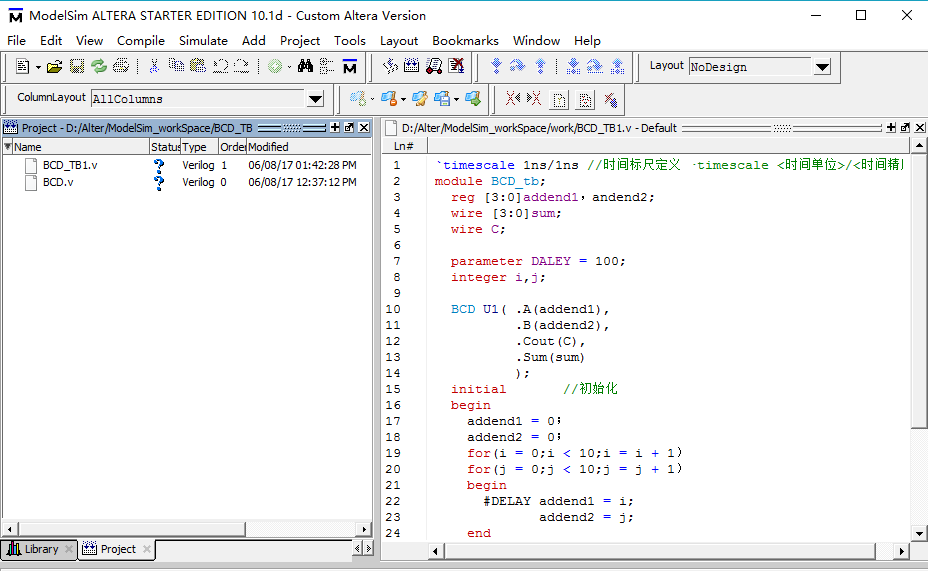

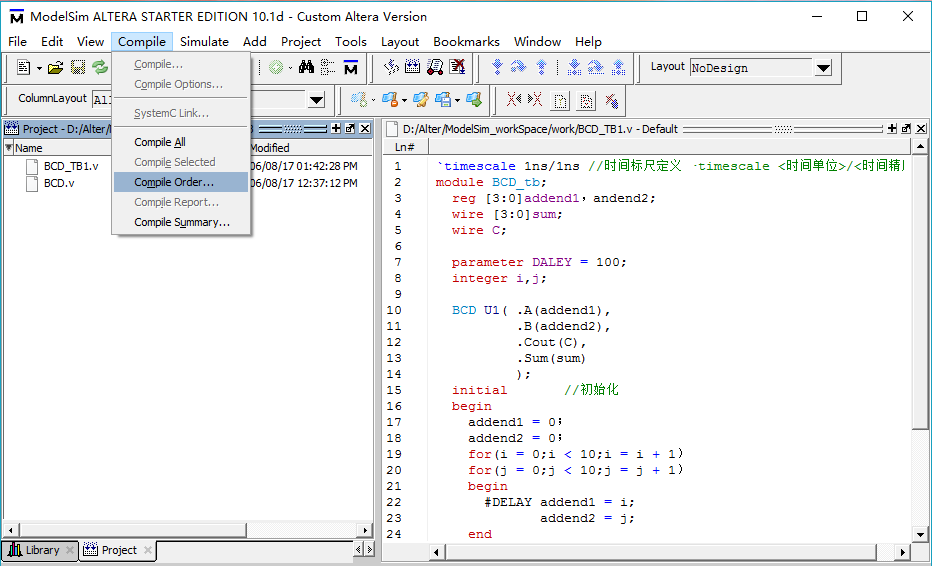

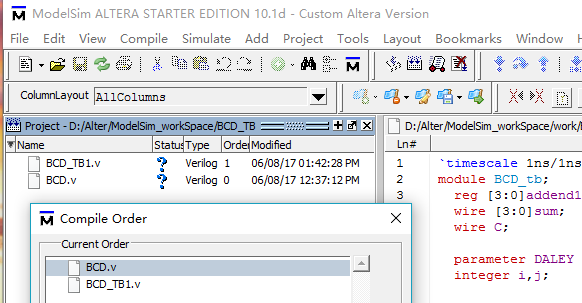

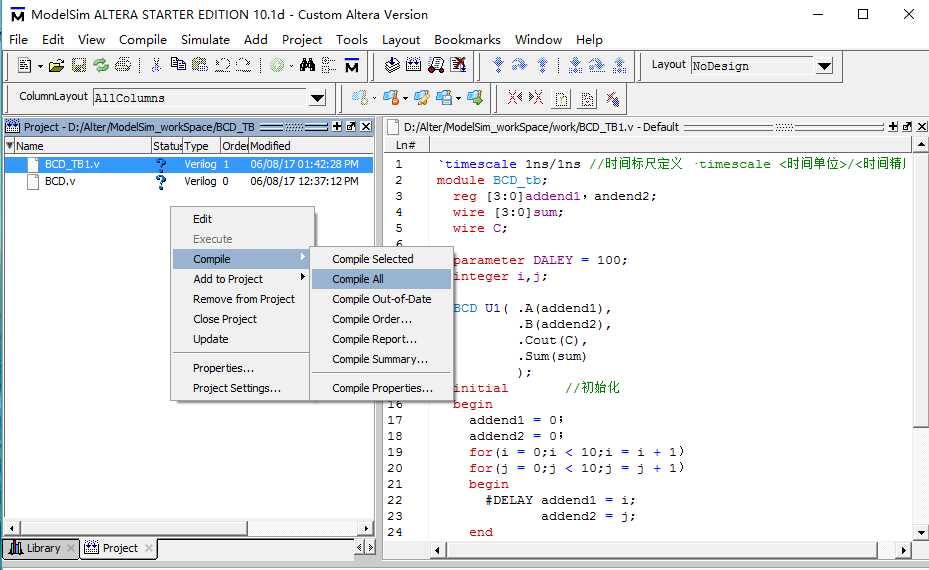

4、创建工程。

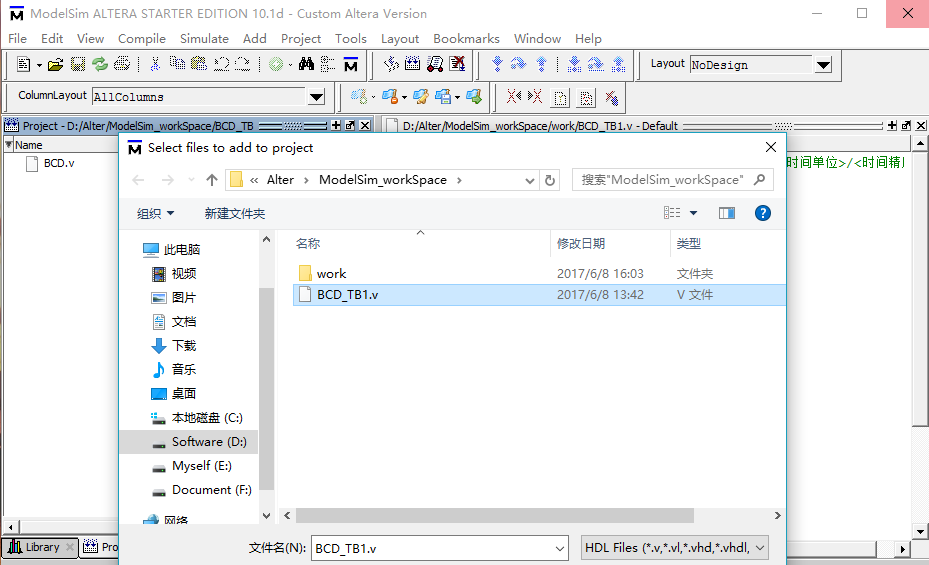

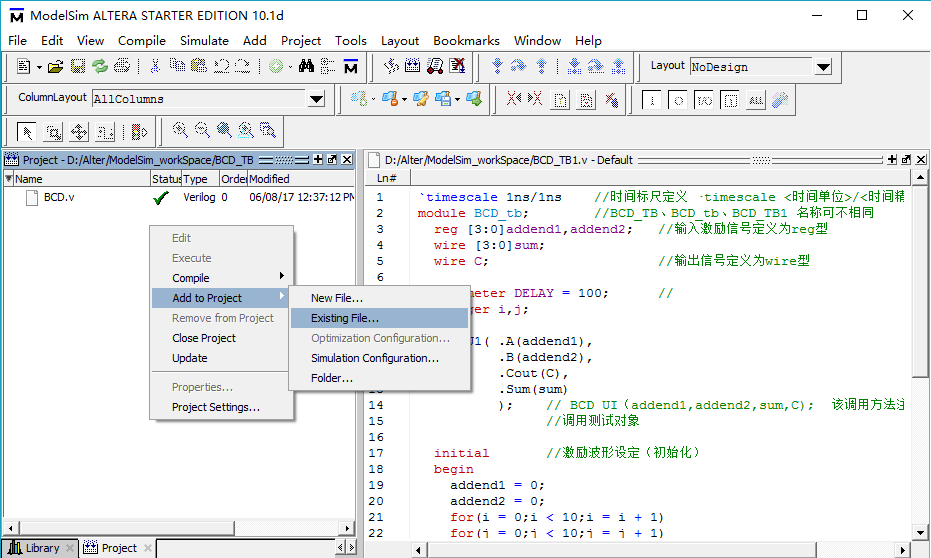

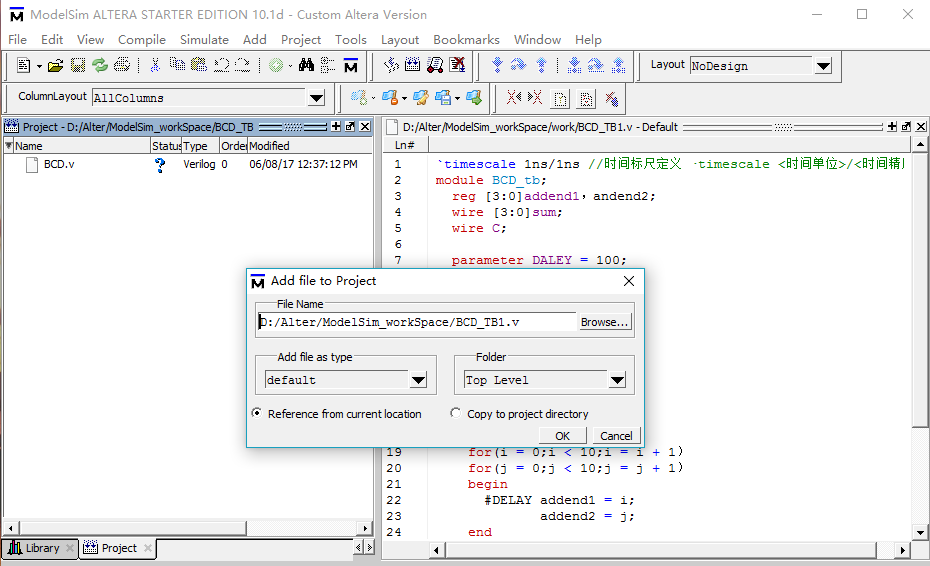

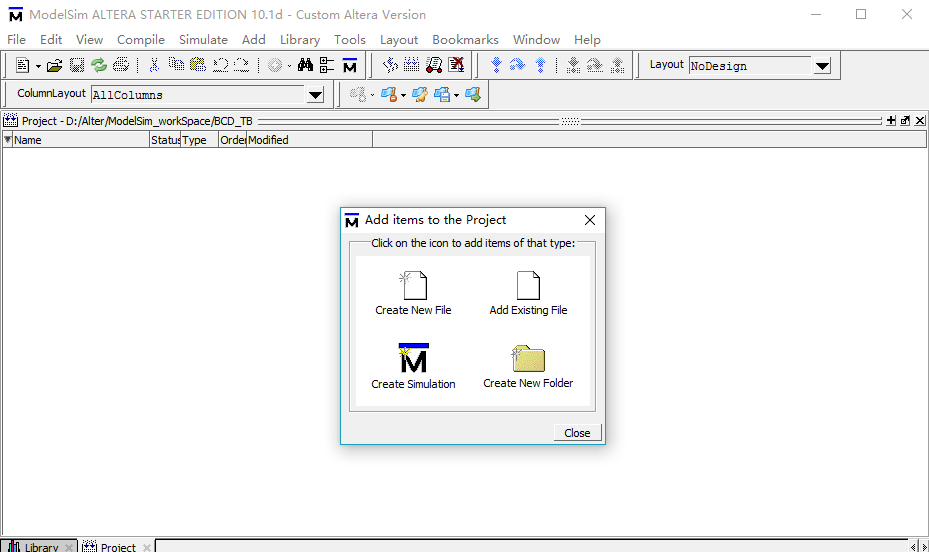

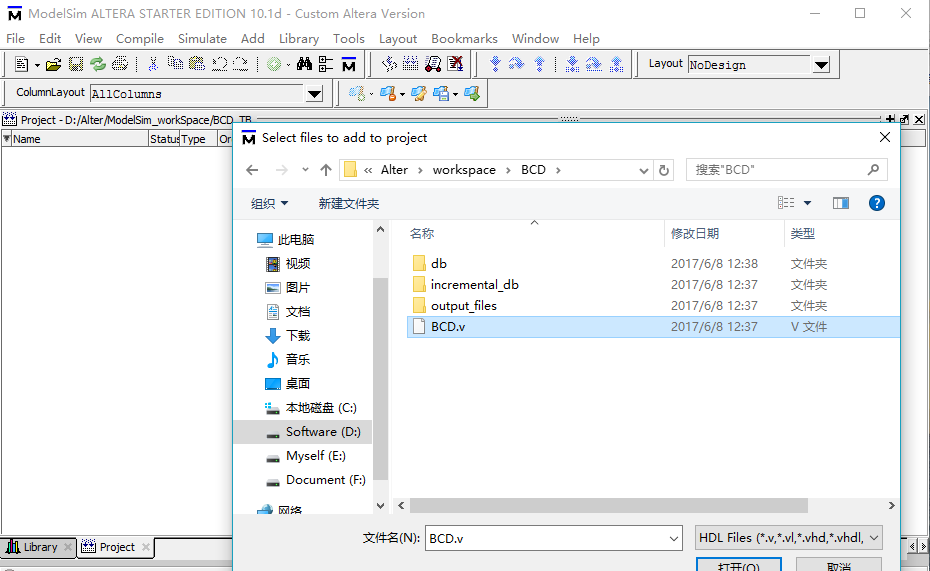

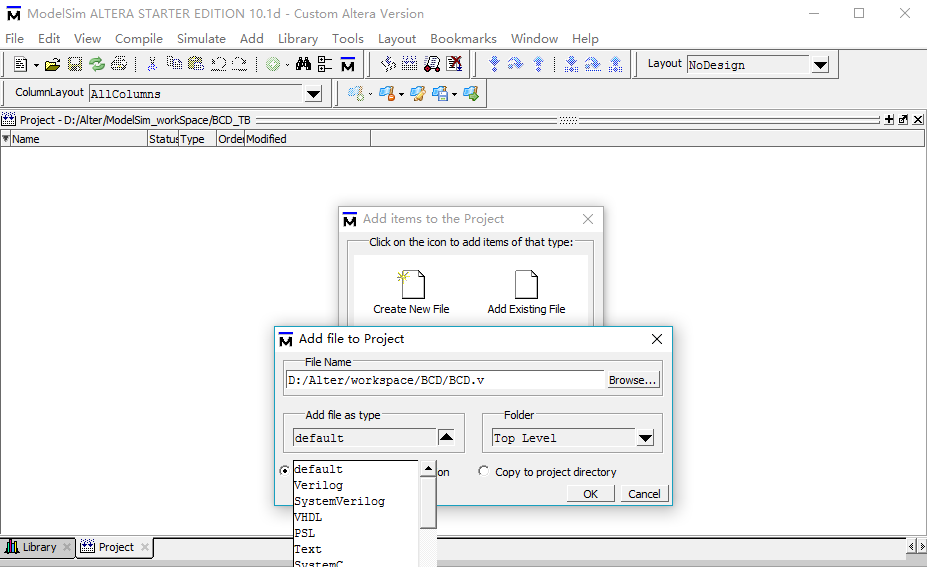

4.1 导入工程测试文件。以BCD码加法器源码为方针文件,直接从quartus II 的workspace中导入代码,即Add Existing File(添加已存在文件)

如下图:

注意:界面中Reference... & Copy... 两项,前者便于修改和调试代码,老司机可选;后者是直接将BCD.v 复制到 ModelSim_workSpace(ModelSim工作区)里面,初学者可选

BCD码加法器源码如下: 分别使用assign 和 always 语句描述。

module BCD(A,B,Sum,Cout);

input [3:0]A,B;

output [3:0]Sum;

output Cout;

// reg [3:0]Sum;

// reg Cout;

wire [4:0]Temp;

assign Temp = A + B;

assign {Cout , Sum} = (Temp > 9 )? Temp +6 : Temp;

/* always@(A or B)

begin

{Cout , Sum} = A + B;

if({Cout , Sum} > 9 )

{Cout , Sum} = {Cout , Sum} + 6;

end

*/

endmodule

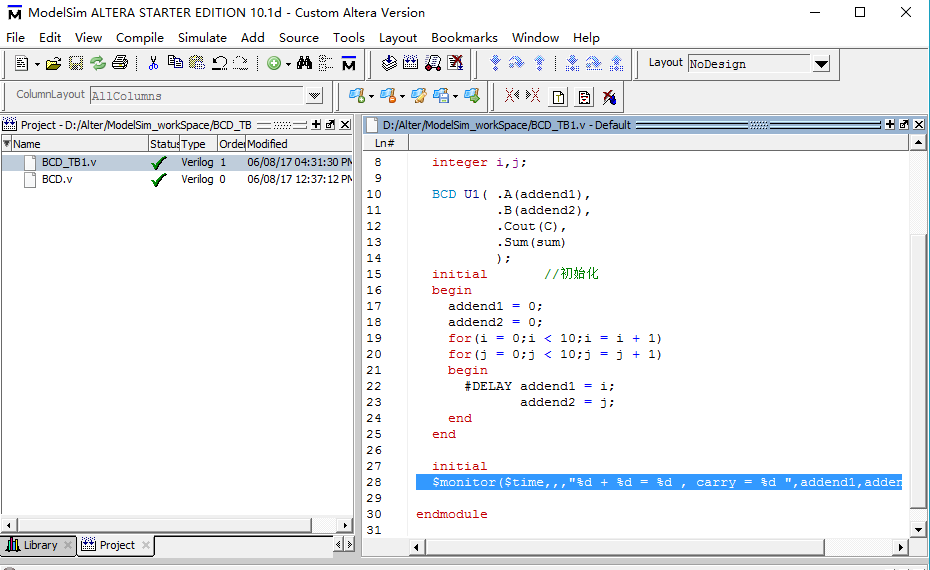

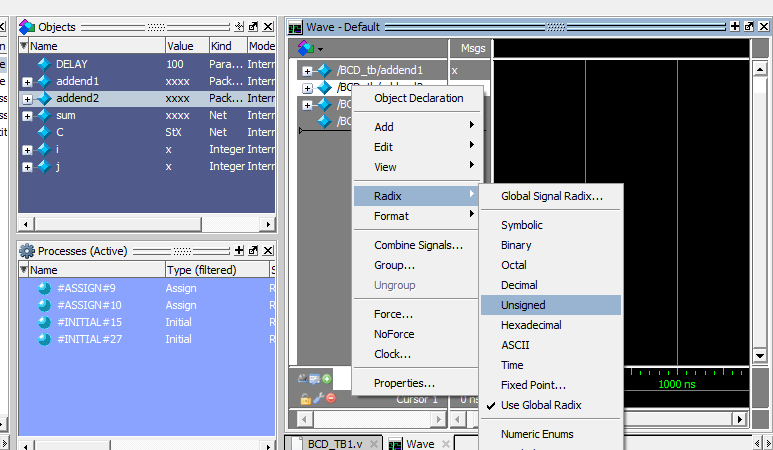

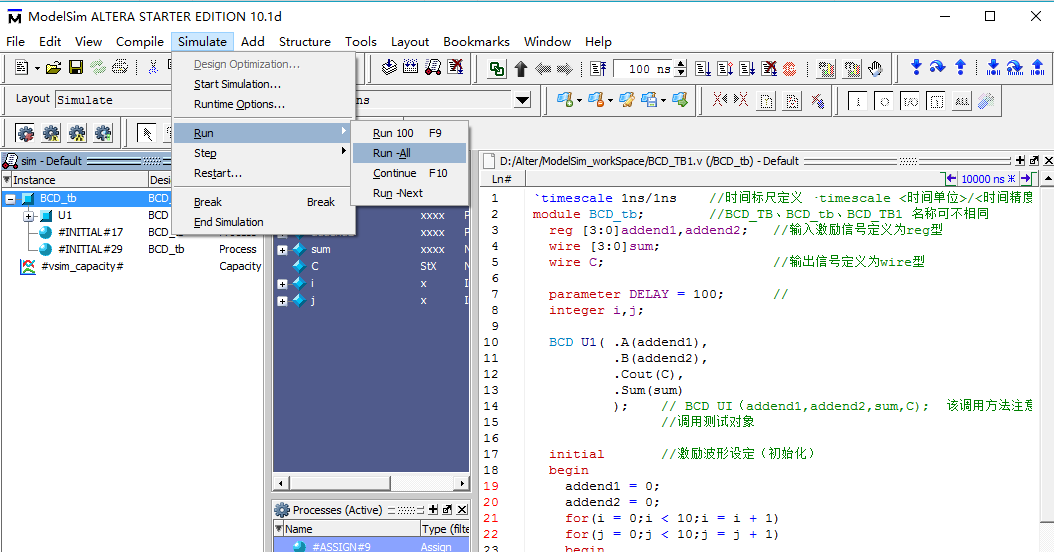

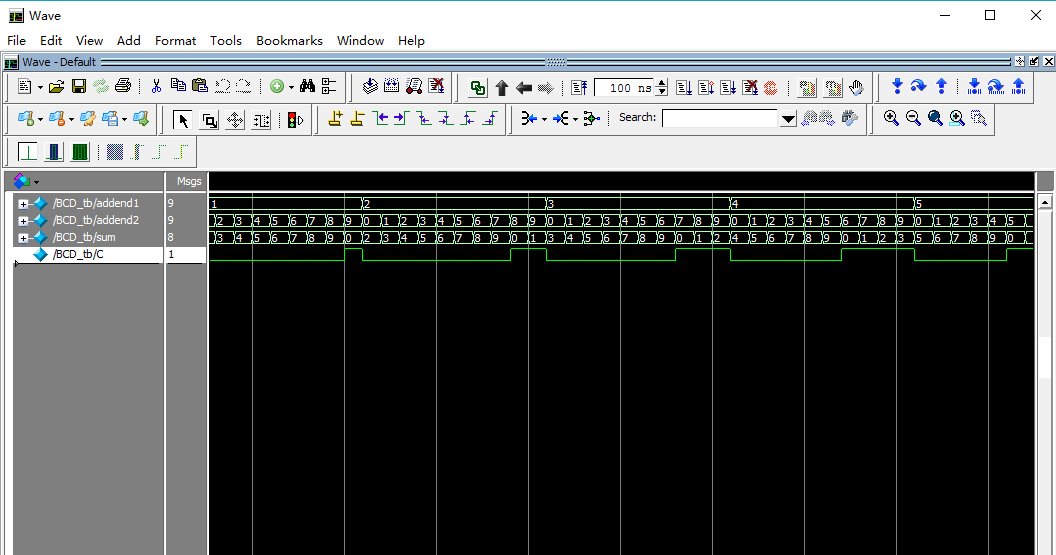

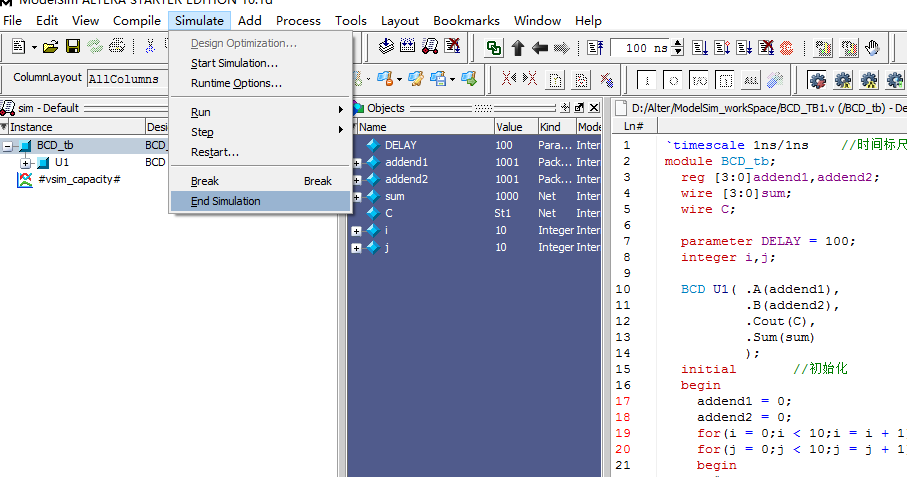

`timescale 1ns/1ns //时间标尺定义 ·timescale <时间单位>/<时间精度>

module BCD_tb; //BCD_TB、BCD_tb、BCD_TB1 名称可不相同

reg [3:0]addend1,addend2; //输入激励信号定义为reg型

wire [3:0]sum;

wire C; //输出信号定义为wire型

parameter DELAY = 100; //

integer i,j;

BCD U1( .A(addend1),

.B(addend2),

.Cout(C),

.Sum(sum)

); // BCD UI(addend1,addend2,sum,C); 该调用方法注意顺序不能颠倒

//调用测试对象

initial //激励波形设定(初始化)

begin

addend1 = 0;

addend2 = 0;

for(i = 0;i < 10;i = i + 1)

for(j = 0;j < 10;j = j + 1)

begin

#DELAY addend1 = i;

addend2 = j;

end

end

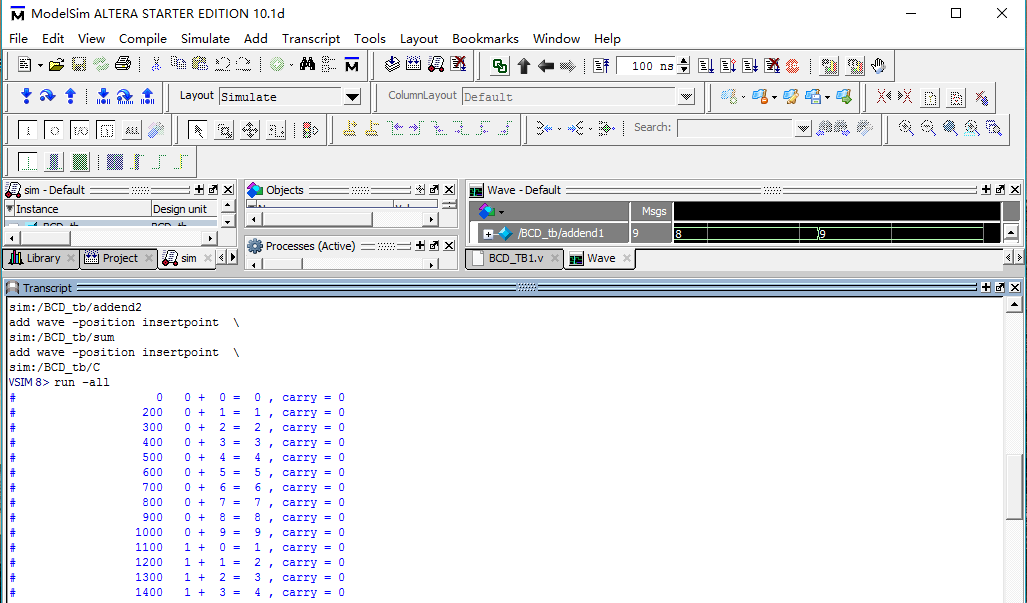

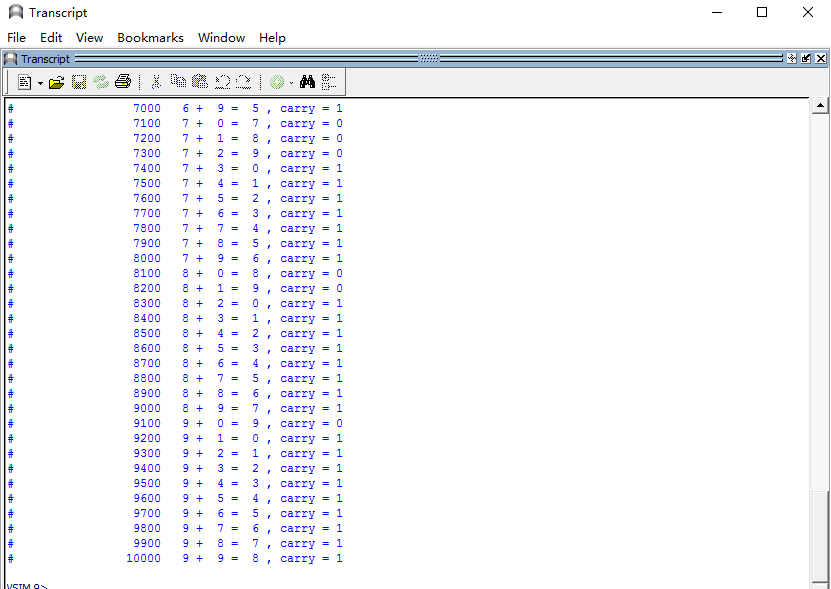

initial

$monitor($time,,,"%d + %d = %d , carry = %d ",addend1,addend2,sum,C);

//输出格式定义

//$monitor("格式控制符“,输出变量名列表);

/* ===>每次信号的值发生变化,都会激活该语句,并显示当前仿真时间

可看作一个持续监控器,可在transcript下查看wave的仿真结果。 */

endmodule

/

/

1886

1886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?