大家都知道阻抗不连续会造成传输线的信号反射,但是信号反射却不仅仅只是由阻抗不连续造成的,其实很多PCB走线不规范的设计也会引起传输线信号的反射。

信号互连中的分支

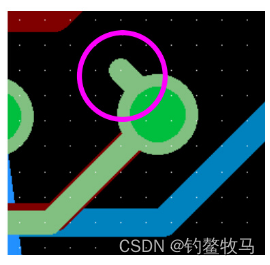

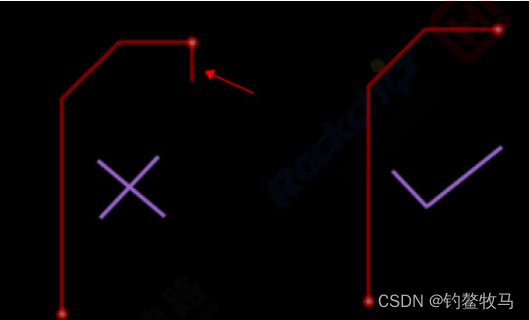

举个很简单的例子,有的工程师在设计PCB 布线过程中,总会不小心多出一些布线线头,如下图1所示,还有一些硬件工程师为了一些兼容设计,也会出现潜在一些开路的线头的风险,当然有经验的硬件和Layout工程师是基本上不会犯这种错误的。

以上所提到的这些线头通常就叫做短桩线或者残桩线(亦或叫Stub线),这种线头一般是不允许出现的,多余的线头会产生天线辐射效应,严重的会引起信号反射,最终出现信号完整性问题, 除了Stub线之外,经常还可以看到stub孔等,接下来我将介绍一些常见的stub给大家认识。

Stub示意:

|

|

|

| 1、断线头 | 2、测试点的添加 |

|

|

|

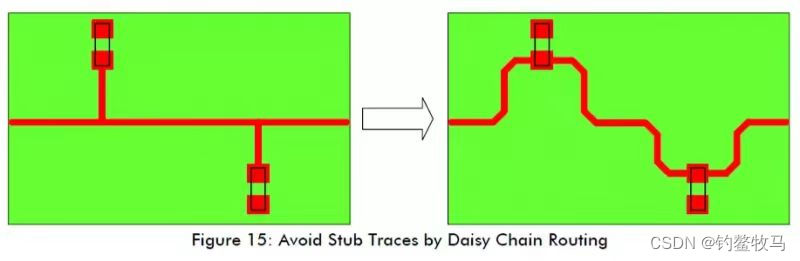

| 3、多余走线 | 4、走线拓扑上的分支 |

| ||||

| 5、过孔的残桩 | ||||

|

|

| |||

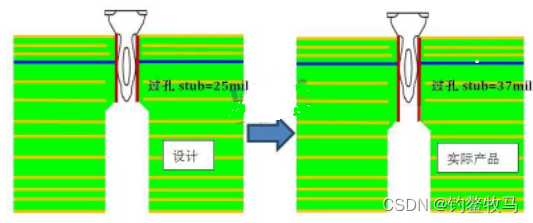

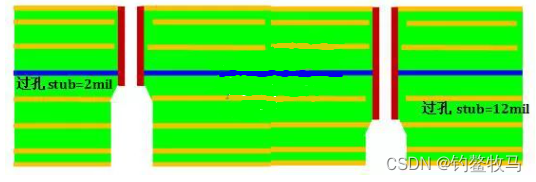

| 6、连接器背钻残留 | 7、板厂背钻工艺导致stub | |||

|

|

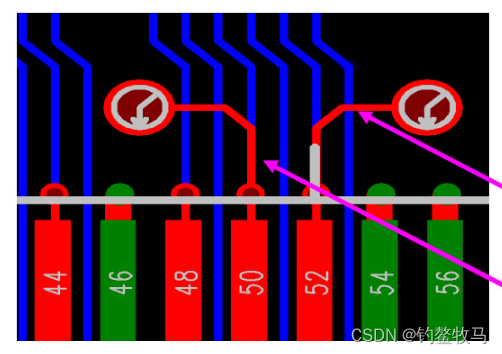

| 8、插装器件布线选择和焊接导致stub |

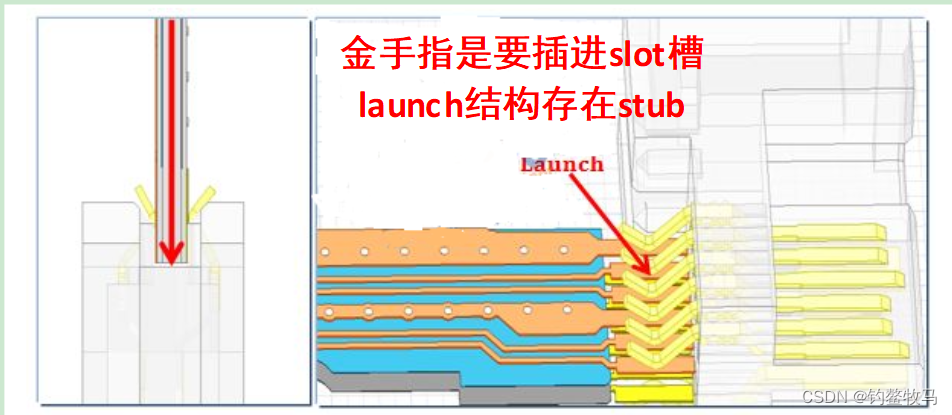

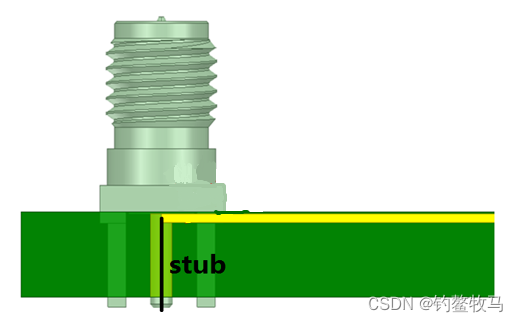

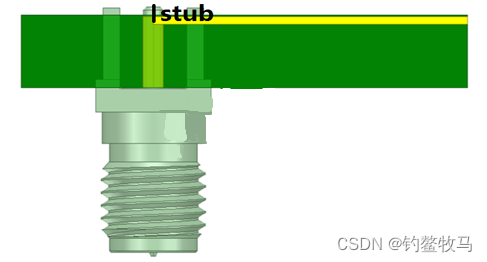

9、金手指Launch具有stub

|

|

| 10、DDR地址时钟等拓扑导致的stub |

|

|

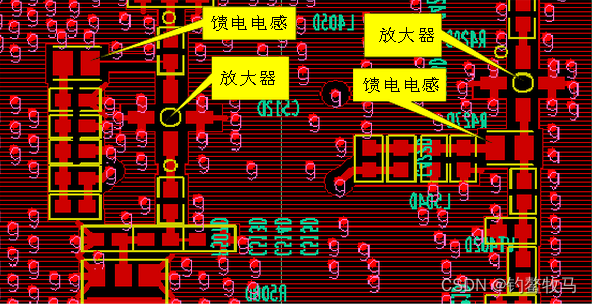

| 11、偏置电路布局拓扑导致的stub |

Stub的影响:

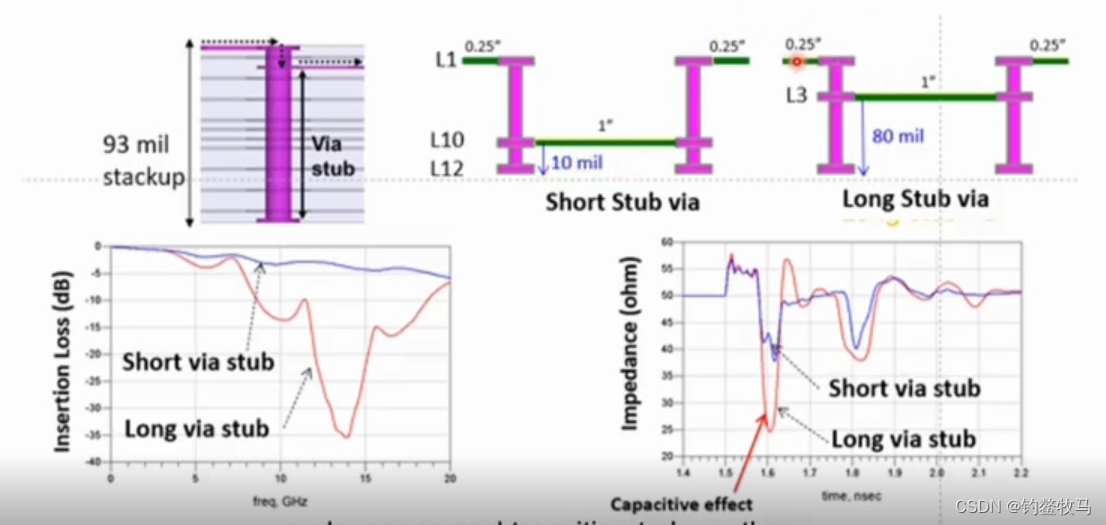

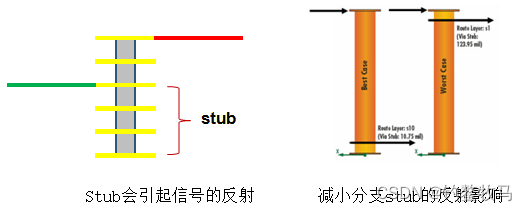

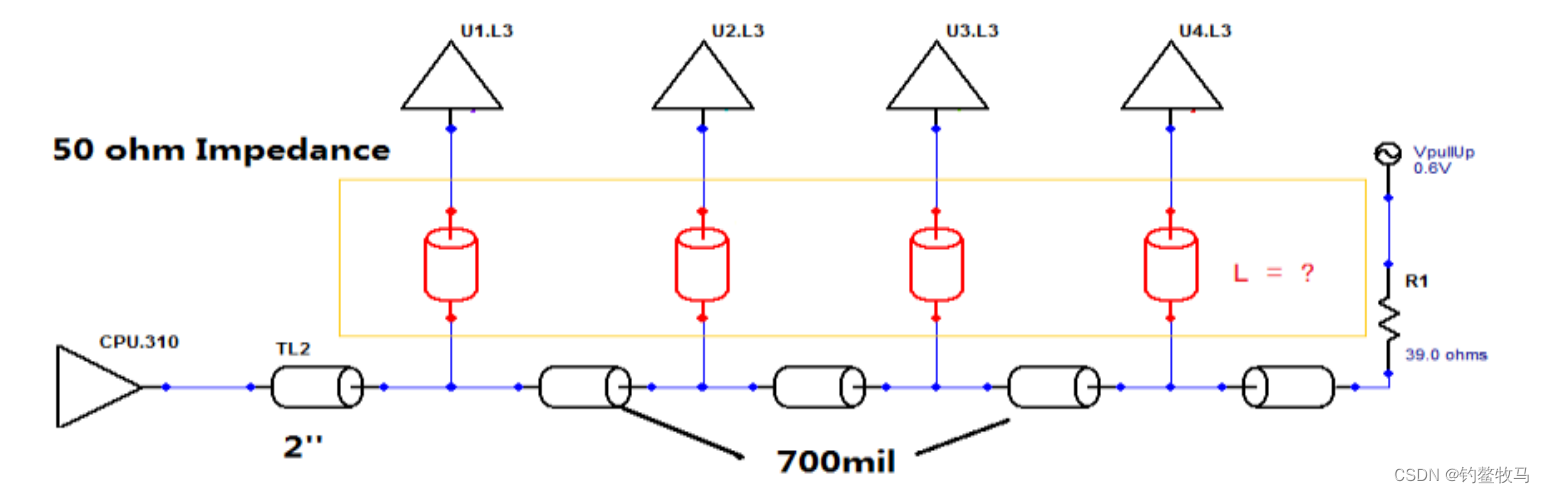

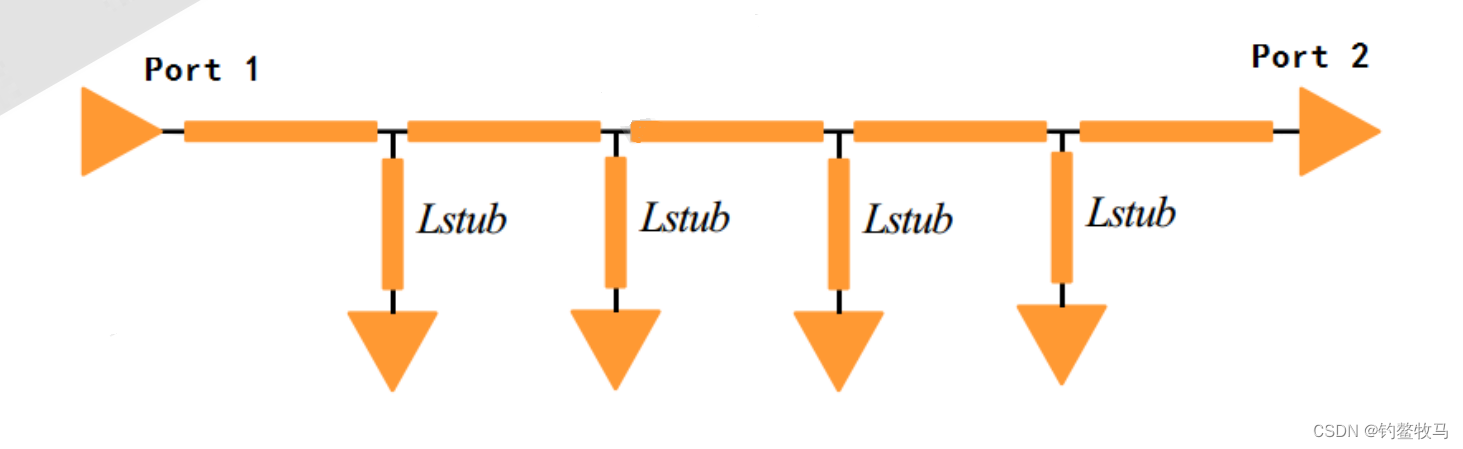

- Stub会导致容性效应,从而导致阻抗偏低,影响信道的阻抗一致性。Stub越长,阻抗掉的越低。为什么会这样?传输线瞬态阻抗计算公式为Z=√(L/C)。就是信号感知的电感与电容的比值再开根号。因为分叉处的传输线与主线之间是并联关系,Stub就像并联在传输线上的小电容,Stub越长,电容量越大,阻抗也就越低。当然,如果是多分支结构的分支较多,每个分叉处都存在阻抗不连续,信号会在Stub之间来回反射,如图所示,所以分析起来比较复杂。

2.Stub的容性效应会将上升沿变缓,某些时候有利于信号的传输,比如DDRX的地址线主线。(需仿真确认)。

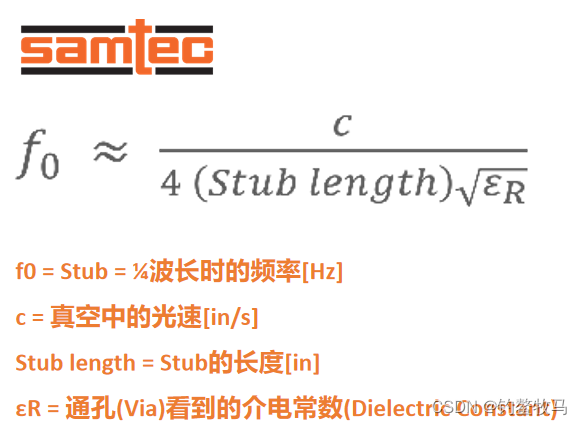

3.Stub长度等于1/4信号波长的频率时影响最为严重,公式如下图,虽然f0是影响最显著的频率,但早在这个频率之前,通孔Stub就开始降低通孔转换的性能,因为它为端点增加额外电容。

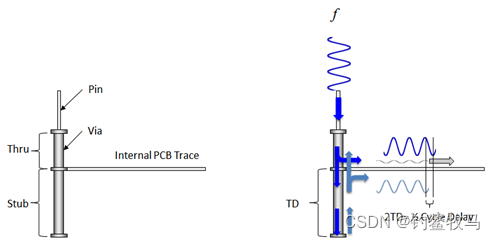

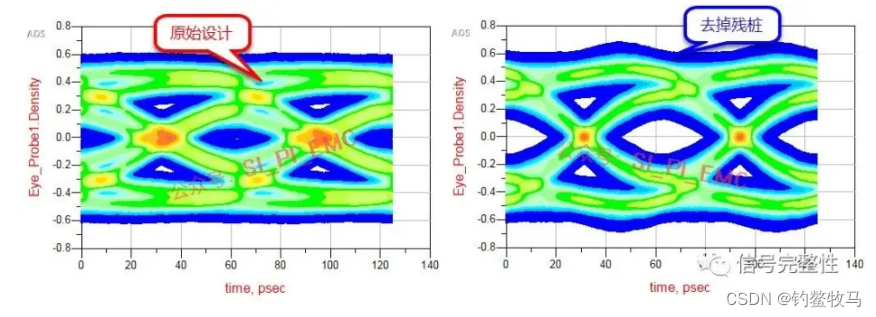

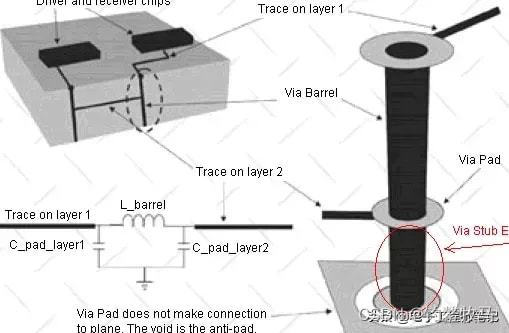

稍微展开讲一下,过孔以走线为界可以分为两个部分,一部分上端的通孔,一部分是下端的stub,当信号从芯片输出到过孔时,一部分信号会继续通过通孔和走线进入到接收端,另一部分信号会沿着stub传输,当到最下端时,由于下端是开路,信号会沿反方向反射回去,这部分也会一部分沿着走线传输,另一部分回到发送端。两者(如下图蓝色和浅蓝信号))最终会在走线通道上进行叠加,当2TD=1/2信号周期时,叠加后的信号受到影响最大(两者刚好相差180度相位)。

过孔结构及其上信号传输演示

评估stub的三种方法:

1)公式估计法:

过孔stub长度控制参考值:stub长度(mil)≤300/速率(Gbps)。频率的话GHz乘以2加入公式替换速率计算。

2)仿真法:

利用仿真软件真实评估最为准确,各大厂家的2.5D和3D的仿真软件完全支持对stub长度的分析。

插入损耗和TDR仿真对比

眼图对比

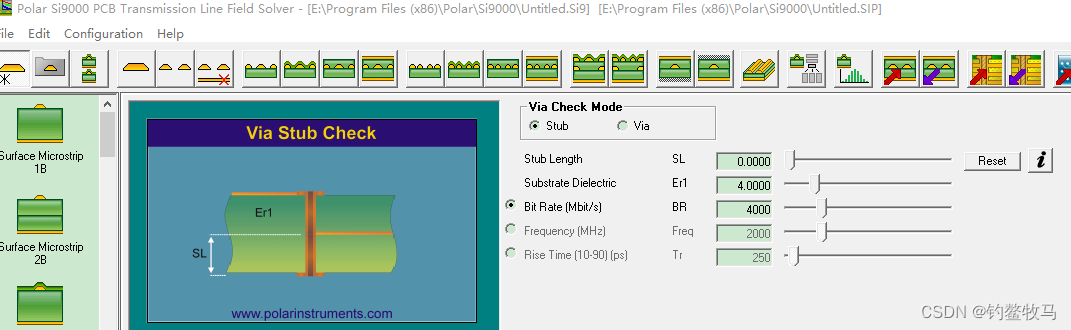

3)软件工具计算法:

如polar 2022版之后就支持了Via stub评估模块,可以快速根据信号的上升时间、频率和速率等要素评估Via stub长度是否能接受。缺点是未能完整考虑PCB的叠层结构,比较粗放。

Stub的解决办法:

1、通过软件检查清除不必要的断线头stub。

2、高速高频通道路径上不允许增加测试点,普通信号测试点stub尽可能短。

3、多余走线检查并清除。

4、优化上下拉电阻,匹配电阻等形成的stub,通过布局布线优化解决。

5、优化走线层,盲埋孔、背钻、多打孔等方式解决过孔残桩,高速多采用背钻方式,高频优先推荐盲埋孔。

6、7选择工艺水平高且稳定的板厂减少背钻不良导致的stub,连接器背钻需考虑鱼眼位置。

8、优化插装器件的布局布线,减少stub,必要时更换表贴器件,消除stub的影响,焊接器件伸出板外过长,可以考虑打磨多余信号针脚。stub较大还可以通过优化布线缩短stub,即采用增加过孔(经过仿真优化)方式消除stub。

9、金手指通过所有层掏空或焊盘隔层参考、缩盘等方式,结合工艺和仿真实现对Launch结构的补偿,提前在PCB板上拉升阻抗以补偿stub的影响。

10、DDRX地址线等,由于多负载形成的stub,首先通过设计优化尽可能减少stub,解决如扇出线过长等问题,多负载可通过容性补偿技术优化即地址主线做低阻抗,分支和互连做高阻抗的方式,工程上一般会选择在主通道末端接上上拉电阻。但是,末端端接只能解决末端反射问题,对于分支上的反射是不能完全消除的。

11、偏置电路布局可以直接电感焊盘放置到微带线上,也可以通过较细的偏置线从微带线上引出到电感焊盘,是一段高阻抗线,可降低其对微带的阻抗影响。

12、硬件工程师在兼容或者选焊器件时采用共用焊盘的形式,进一步缩小stub的长度。

13、优化端接电阻阻值,如在芯片输出端加一颗端接电阻,也可降低Stub线带来的风险。

14、调整信号的上升沿在允许范围内减缓信号上升沿,从而减少stub对信号波形的影响。

Stub在PCB板中出现的形式多种多样,关键是大家需要树立起对stub的认识,在设计中有意识的加以注意,公式也好,仿真也好都是一些我们的手段,关键是对于stub需要提高认识,避免出现一些低级错误!

222

222

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?