///

1,FPGA_Verilog基础篇:Verilog发展进程-CSDN博客

2,FPGA_Verilog基础篇:理解Verilog的四值逻辑-CSDN博客

3,FPGA_Verilog基础篇:Verilog中数值的表示-CSDN博客

4,FPGA_Verilog基础篇:信号声明类型-CSDN博客

5,FPGA_Verilog基础篇:模块的端口声明-CSDN博客

6,FPGA_Verilog基础篇:verilog语言的操作符-CSDN博客

7,FPGA_Verilog基础篇:verilog基本逻辑运算-CSDN博客

8,FPGA_Verilog基础篇:verilog关系操作的逻辑运算实现-CSDN博客

9,FPGA_Verilog基础篇:veriolg算术运算-CSDN博客

10,FPGA_Verilog基础篇:verilog移位操作-CSDN博客

11,FPGA_Verilog基础篇:关系操作符简介-CSDN博客

12,FPGA_Verilog基础篇:拼接运算符简介-CSDN博客

13,FPGA_Verilog基础篇:verilog数值的位宽扩展规则-CSDN博客

14,FPGA_Verilog基础篇:verilog移位与拼接实现-CSDN博客

15,FPGA_Verilog基础篇:verilog双向inout接口表示_fpga inout端口-CSDN博客

16,FPGA_Verilog基础篇:verilog之锁存器和触发器-CSDN博客

17,FPGA_Verilog基础篇:verilog之for循环-CSDN博客

18,FPGA_Verilog基础篇:verilog之函数用法-CSDN博客

19,FPGA_Verilog基础篇:verilog之任务用法-CSDN博客

20,FPGA_Verilog基础篇:verilog之任务与函数用法比较-CSDN博客

21,FPGA_Verilog基础篇:verilog之宏define介绍-CSDN博客

22,FPGA_Verilog基础篇:verilog之条件编译指令介绍-CSDN博客

23,FPGA_Verilog基础篇:verilog之参数parameter介绍-CSDN博客

24,FPGA_Verilog基础篇:verilog之本地参数localparam-CSDN博客

25,FPGA_Verilog基础篇:verilog之generate生成块-CSDN博客

26,FPGA_Verilog基础篇:verilog之常数规则-CSDN博客

27,FPGA_Verilog基础篇:verilog中整数运算的位宽和符号规则-CSDN博客

28,FPGA_Verilog基础篇:verilog中的字符串表示-CSDN博客

29,FPGA_Verilog基础篇:verilog中带整数的算术表达式分析-CSDN博客

30(结束篇),FPGA_Verilog基础篇:verilog中的数值运算规则总结-CSDN博客

///

在《数字电路》或《数字电子技术》教材里,通常说数字电路的理论基础是“二值(0或1)”逻辑的布尔代数。但是我们在学习verilog时,接触的都是“四值”逻辑,分别为:

1)0:逻辑低电平,条件为假

2)1:逻辑高电平,条件为真

3)z:高阻态,悬空

4)x:未知逻辑电平

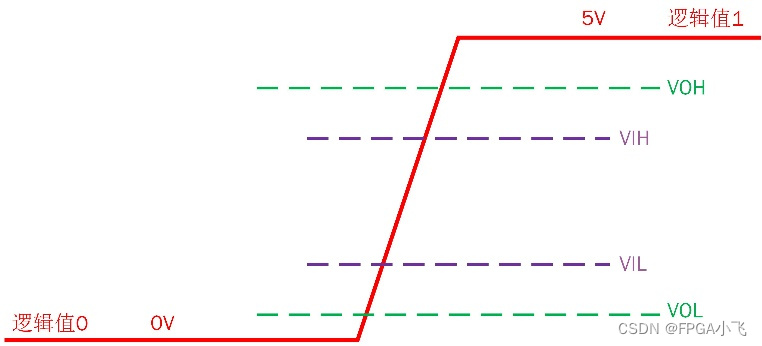

值“0”和“1”不难理解。如下图1所示为5V的TTL电平,当输出电压高于VOH时,认为输出是逻辑值“1”;当输出电压低于VOL时,认为输出为逻辑值“0”;当输入电压高于VIH时,认为输入是逻辑值“1”;当输入电压低于VIL时,认为输入为逻辑值“0”;

图1:TTL电平及逻辑值判断

那么这些“V”的高低之间的区域算什么呢?在真实电路之中,这些区域的电平既可能被认为是“0”,也可能被认为是“1”,也就是不确定值。

在verilog语言的仿真里,不存在这种模棱两可的东西,于是“x”这个第三者出现了,表示信号为未知状态。

未知逻辑电平“x”出现主要有两种可能。第一个就是触发器不满足时钟采样的时序要求,时钟沿采集到信号的边沿;另一个就是信号未被“赋初值”。

未知逻辑电平“x”只在电路仿真中存在,但是高阻态“z”却是在电路系统中真实存在的一种电平状态。高阻态是数字电路里常见的术语,指的是电路的一种输出状态,它既不是高电平,也不是低电平。如果高阻态输出到下一级电路,则对下级电路无任何影响,和没接一样。此时我们如果用万用表测量高阻态输出的电压时,既可能是高也可能是低电平,由它后面接的电路而定。

进行电路分析时,高阻态可当做开路处理。我们可以把它看做输入/输出电阻非常大,极限状态就是悬空(开路)。也就是说,理论上高阻态不是悬空,它是对地或电源电阻极大的状态。而在实际应用中,它与管脚悬空几乎是一样的。

举个例子:我们学过模拟/数字电子学的小伙伴们都知道,当cmos门电路的输出上拉晶体管导通而下拉晶体管截止时,输出为高电平。反之,上拉晶体管截止而下拉晶体管导通就是低电平。但是当上拉和下拉晶体管都截止时,输出端就相当于悬空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制,这就是所谓的高阻态z。

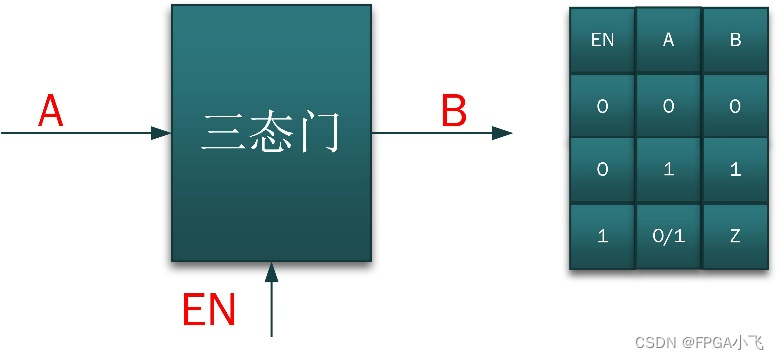

输出高阻态在verilog中可以利用名字叫“三态门”的器件实现,其符号和真值表如下图2所示:

图2:三态门电气符号与真值表

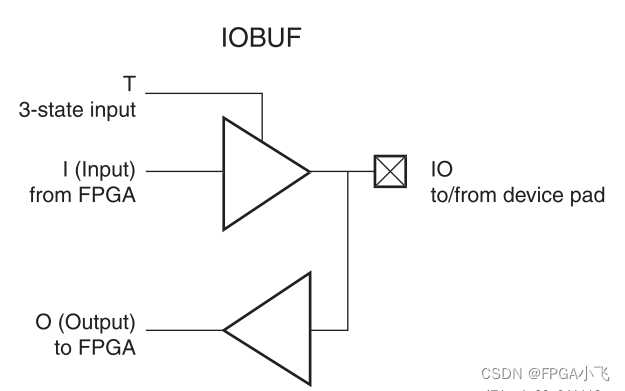

高阻态一般都会在输入/输出管脚处使用,例如FPGA的IOBUF就包含一个典型的三态门,如下图3所示:

图3:FPGA的IOBUF

FPGA的三态门如何使用,博主小飞将在后续的FPGA系列篇中分享,咱们这个系列只说verilog~

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起学习、一起进步吧~

377

377

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?