文章目录

0.总览

可编程逻辑单元CLB(Configurable Logic Block)、可编程I/O单元和布线资源构成了FPGA内部三大主要资源。

本文以Xilinx 7系列FPGA为例进行FPGA结构和片上资源讲解,其采用28nm工艺节点。

1.可配置逻辑块CLB

可配置的逻辑块(CLB)是主要的逻辑资源,用于实现时序和组合逻辑电路。

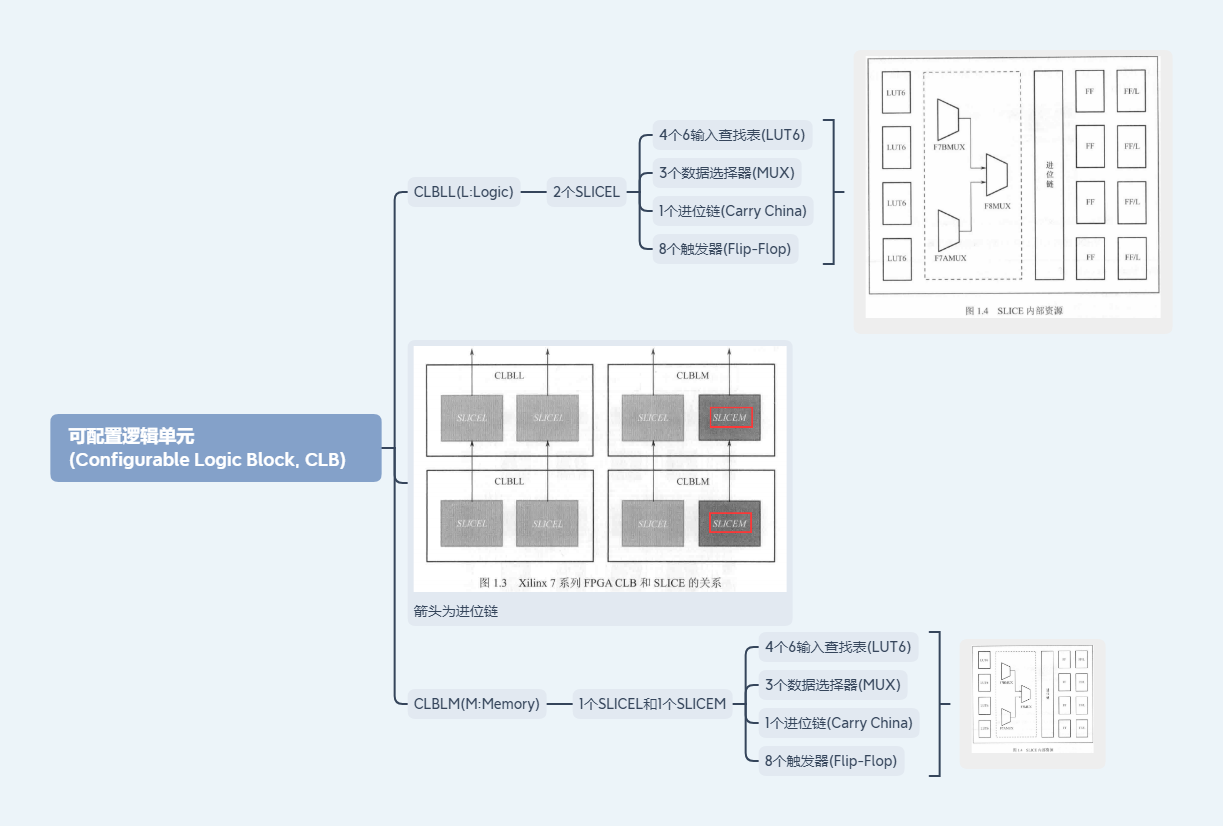

可配置逻辑单元(CLB)在 FPGA 中最为丰富,由两个 SLICE 组成。由于 SLICE 有 SLICEL(L:Logic)和 SLICEM(M:Memory)之分,因此 CLB 可分为 CLBLL 和 CLBLM 两类。

一个CLB包含两个SLICE:2个SLICEL或者1个SLICEL+一个SLICEM。

SLICEL和SLICEM内部都包含4个6输入查找表(Look-Up-Table,LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop)。

1.1 6输入查找表(LUT6)

查找表Look-up Table,本质上就是1个6输入,64深度的ROM (SLICEM中的则是RAM,因为可读)。通过将所有结果保存在其内部,使用时通过由输入构建的地址线对其进行查找,从而实现6输入的函数逻辑。需要注意的是SLICEM中的查找表,除了读功能外还具备写功能,这就使得其内部的LUT由一个ROM变成了一个RAM,这也是其实现移位寄存器功能和分布式DRAM功能的原因。

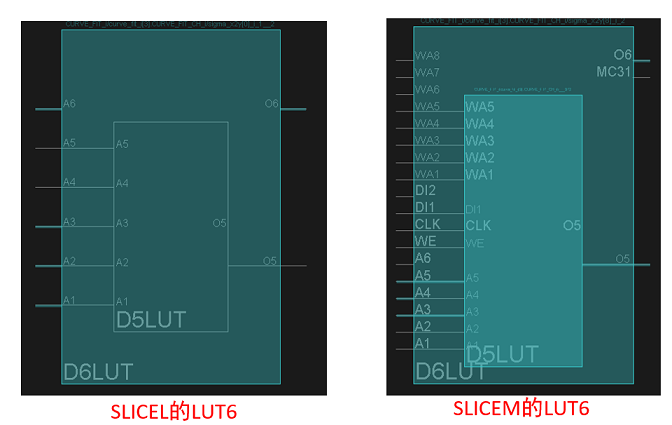

虽然SLICEL和SLICEM的结构组成一样,但两者更细化的结构上略有不同,区别在于LUT6上(如下图所示),从而导致LUT6的功能有所不同(如下表格所示)。

| LUT功能 | SLICEL | SLICEM |

|---|---|---|

| 逻辑函数发生器 | √ | √ |

| ROM | √ | √ |

| 分布式RAM | √ | |

| 移位寄存器 | √ |

逻辑函数发生器:用作逻辑函数发生器时,查找表就扮演着真值表的角色,真值表的内容可在Vivado中查看。

ROM:不论是 SLICEL 还是 SLICEM,他们的 LUT6 都可以作为 ROM 使用,配置为 64x1(占用 1 个 LUT6,64 代表深度,1 代表宽度)、128x1(占用 2 个 LUT6)和 256(占用 4 个 LUT6)的 ROM。

分布式RAM: SLICEM中的查找表可配置为RAM ( Random Access Memory),称为分布式RAM。其中 RAM 的写操作为同步,而读操作是异步的,即与时钟信号无关。如果要实现同步读操作,则要额外占用一个触发器,从而增加了意识时钟的延迟(Latency),但提升了系统的性能。这就解释了为什么我们实现RAM同步读写的时候,读出输出要延迟一个 clk。对于布式存储单元(RAM和ROM),Vivado 提供了相应的IP: Distributed Memory Generator。

移位寄存器:SLICEM 中的 LUT 还可以配置为移位寄存器,每个 LUT6 可实现深度为 32 的移位寄存器,(注意:只能左移)。这样,每个LUT可以将串行数据延迟1到32个时钟周期。移位输入D(LUT DI1脚)和移位输出Q31 (LUT MC31脚)可以进行级联,以形成更大的移位寄存器。一个SLICEM的4个LUT6级且同一个 SLICEM 中的 LUT6(4个)可级联实现 128 深度

本文详细介绍了Xilinx7系列FPGA的可配置逻辑块CLB(包括LUT6、MUX、CarryChain和触发器)、可编程I/O单元的物理和逻辑层面,以及布线资源的结构和功能。此外,还提供了在Vivado中查看和管理这些资源的方法。

本文详细介绍了Xilinx7系列FPGA的可配置逻辑块CLB(包括LUT6、MUX、CarryChain和触发器)、可编程I/O单元的物理和逻辑层面,以及布线资源的结构和功能。此外,还提供了在Vivado中查看和管理这些资源的方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?