目录

所谓的边沿检测(又叫边沿提取),就是检测输入信号的上升沿和下降沿。在设计数字系统时,边沿检测是一种很重要的思想,实际编程时用的最多的时序电路应该就是边沿检测电路和分频电路了。

在always的敏感信号列表中可以直接使用posedge和negedge来提取上升沿和下降沿,但是要是在always程序块的内部检测上升沿或者下降沿,使用posedge和negedge显然是不可以的,因为这样的语句不可综合。

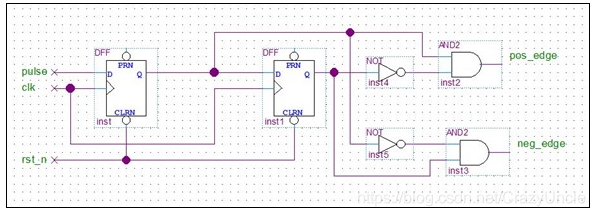

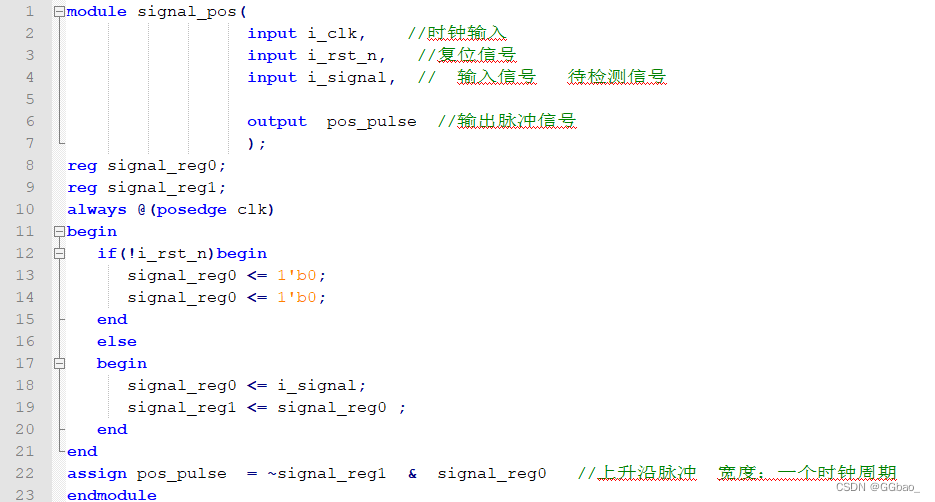

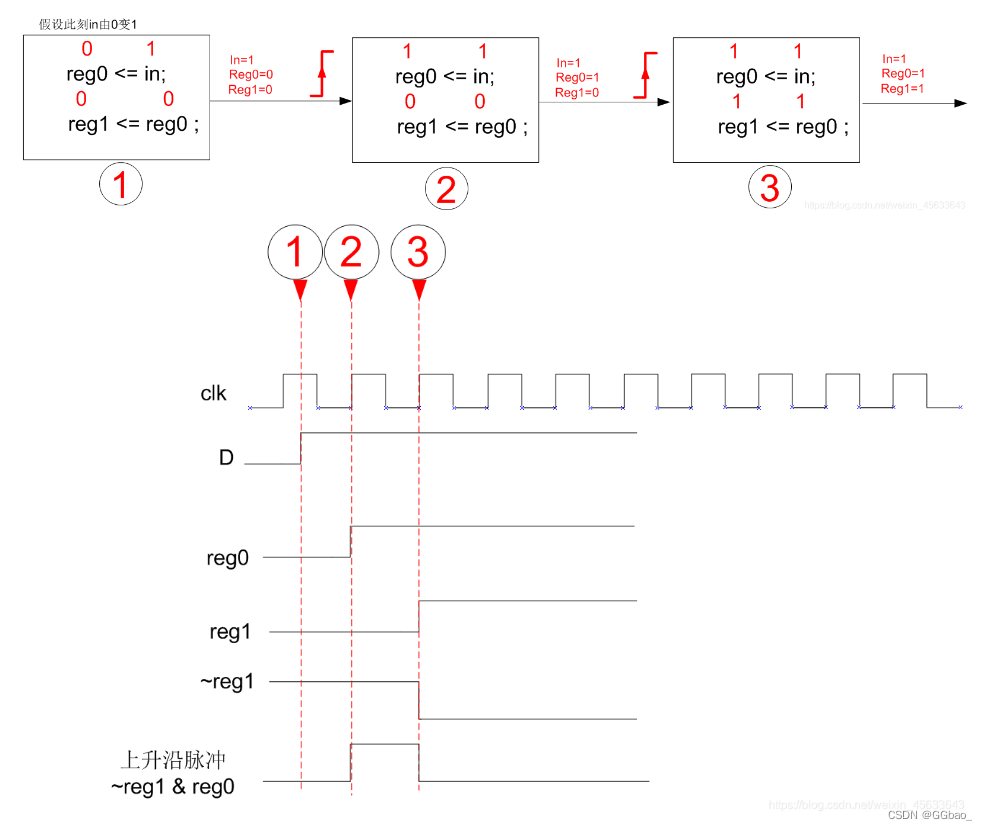

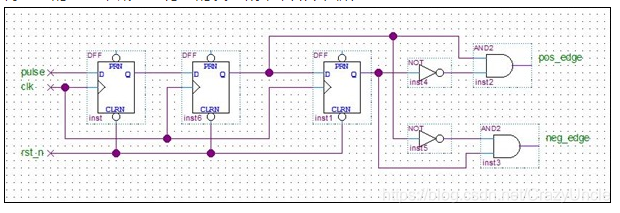

要实现边沿检测,最直接的想法是用两级寄存器,第二级寄存器锁存住某个时钟上升沿到来时的输入电平,第一级寄存器锁存住下一个时钟沿到来时的输入电平,如果这两个寄存器锁存住的电平信号不同,就说明检测到了边沿,具体是上升沿还是下降沿可以通过组合逻辑来实现。

同步信号的边沿检测

当待检测信号pulse是一个异步信号时候,输出可能是亚稳态。

如果pulse信号发生在clk时钟变化边沿的时候,其建立保持时间存在违例,那么第一级寄存器的输出pulse_r1就会进入亚稳态,而此亚稳态会继续传递给pos_edge和neg_edge信号。

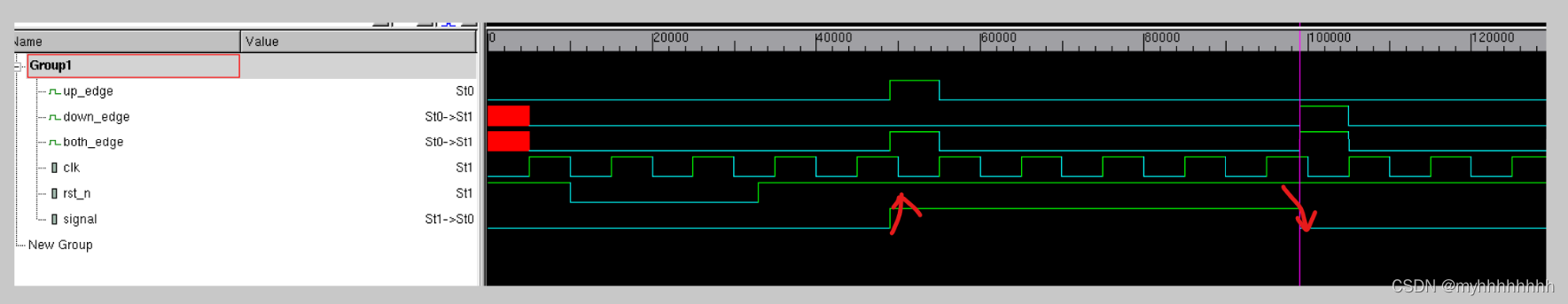

上升沿特征:先进来低电平,后进来高电平。

下降沿特征:先进来高电平,后进来低电平。

对于上升沿来说,用clk与寄存器进行采样,前一拍采集到的是0,用A表示,后一拍输入结果是1,用B表示,通过组合逻辑,表达式为 !A&B。

对于下降沿来说,用clk与寄存器进行采样,前一拍采集到的是1,用A表示,后一拍输入结果是0,用B表示,通过组合逻辑,表达式为 A&!B。

对于双边沿检测来说,输出是 !A&B + A&!B,即A^B异或操作。

一级触发器(打一拍)

两级触发器(打两拍)

打三拍甚至更多拍的方法就是多声明几个reg变量寄存信号,并在else中多次<=赋值。

异步信号的边沿检测

此电路同样适用于同步

异步电路信号检测需要先将异步信号同步化,一般采用多加一级寄存器的方法来减少亚稳态的发生概率。异步信号电路检测中,至少需要采用三级寄存器来实现。

参考:

https://blog.csdn.net/weixin_46022434/article/details/107589091

https://blog.csdn.net/weixin_45633643/article/details/108702774

347

347

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?