- DDR3 SDRAM信号分组

- 数据信号组:MDM(8:0),MDQ(63:0),MECC(7:0)

- 数据选通组:MQS_p(8:0),MQS_n(8:0)

- 地址/命令信号组:MBA(2:0),MA(15:0),MRAS_n,MCAS_n,MWE_n

- 控制信号组:MCS_n(3:0),MCKE(3:0),MODT(3:0)

- 时钟信号组:MCK_p(5:0),MCK_n(5:0)

- 电源:VREF,VTT

表1 数据字节lane分组

| Data | Data Strobe | Data Mask | Lane Number |

| MDQ[0:7] | MDQS0_p, MDQS0_n | MDM0 | Lane 0 |

| MDQ[8:15] | MDQS1_p, MDQS1_n | MDM1 | Lane 1 |

| MDQ[16:23] | MDQS2_p, MDQS2_n | MDM2 | Lane 2 |

| MDQ[24:31] | MDQS3_p, MDQS3_n | MDM3 | Lane 3 |

| MDQ[32:39] | MDQS4_p, MDQS4_n | MDM4 | Lane 4 |

| MDQ[40:47] | MDQS5_p, MDQS5_n | MDM5 | Lane 5 |

| MDQ[48:55] | MDQS6_p, MDQS6_n | MDM6 | Lane 6 |

| MDQ[56:63] | MDQS7_p, MDQS7_n | MDM7 | Lane 7 |

| MECC[0:7] | MDQS8_p, MDQS8_n | MDM8 | Lane 8 |

- 电源设计约束

- 主电源(VDD/VDDQ)

主电源的要求是VDDQ=VDD,一般的使用中都是把VDDQ和VDD合成一个电源使用(有的芯片还有VDDL,是给DLL供电的,也和VDD使用同一电源即可)。

主电源设计时,需要注意:

- 电压、电流是否满足要求,电源的上电顺序和电源的上电时间,单调性是否满足要求

- 电源电压的要求一般在±5%以内

- 要求在PCB设计时,有一个完整的电源平面铺到管脚上

- 在电源入口加大电容储能

- 每个管脚上加一个100nF~10nF的小电容滤波

- 参考电源(VREF/VREFCA/VREFDQ)

该电源电流较小,但VREF的不稳定会导致时序误差、产生比较大的抖动等问题,因此要确保VREF电压值的稳定,要求波动范围+/-2%。对于VREF的走线要求:

- 走线宽度30mil,推荐走在表层

- 距离其他信号走线大于20mil,距其他干扰源(power switch、晶振等)250mil以上

- 在小负载的情况下(内存颗粒少于4个),VREF可通过1%的电阻对VDD分压产生,分压电阻附近放置1个0.1uF电容

另外,与DDR2不同,DDR3有2个参考电压:VREFCA与VREFDQ,

VREFCA:命令、地址信号参考电压

VREFDQ:数据信号参考电压

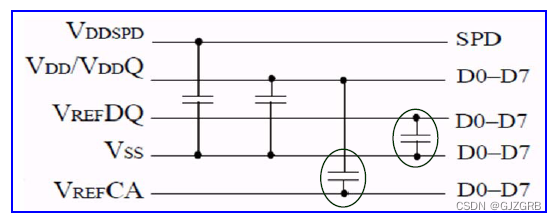

VREFCA与VREFDQ的电源管脚需要增加10nF的滤波电容,如下图所示:

图1 VREFCA与VREFDQ的滤波电容放置方式

- 用于匹配的电压VTT

- VTT的瞬间电流需求较大,必须采用专用的电源芯片产生,禁止使用分压电阻方式

- VTT的铺铜宽度至少150mil

- VTT铺铜走在表层,产生VTT的电源靠近内存颗粒放置,如设计中采用的DIMM内存条的方式,则VTT电源需要靠近DIMM插槽上的VTT引脚放置

- VTT的铺铜平面上靠近DIMM插槽的位置放置4个0.1uF的电容,另外需再放置1~2个10~22uF的电容

- 每个上拉到VTT的匹配电阻旁放一个10nF~100nF的去藕电容,这个VTT电路上需要有uF级的电容进行触能

- PCB布线指导

- 时钟信号组

| 参数 | 描述 |

| 信号组(Signal Group) | Clock: MCK_p(5:0) and MCK_n(5:0) |

| 拓扑(Topology) | 如采用DIMM内存条:点对点差分 如采用内存颗粒:菊花链或fly-by(超过800MHz速率必须采用fly-by走线拓扑) |

| 差分信号组抗 | 单端阻抗:40–50 W 差分阻抗:75-90 W 终端匹配电阻为差分阻抗的1/2 |

| 与非DDR3信号的最小间距 | 25mil |

| 与其它DDR3信号组的最小间距 | 20mil |

| 最大的过孔数 | 2个,推荐在信号换层时在信号线附件增加地的过孔 |

| CKx_p与CKx_n的长度匹配 | 总长度的最大差<5mil |

| 时钟对于时钟对的长度匹配 | 到相同DIMM的总长度的最大差:+/-10mil |

| 注意:时钟信号的走线长度(控制器到内存颗粒)要长于与其对用的strobe信号走线长度。 Note: The clock signal trace length from the memory controller to any given DDR3 chip must be longer than its corresponding strobe trace length. | |

- 控制信号

| 参数 | 描述 |

| 信号组(Signal Group) | Control: MCS_n(3:0),MCKE(3:0),MODT(3:0) |

| 拓扑(Topology) | 如采用DIMM内存条:点对点 如采用内存颗粒:菊花链或fly-by(超过800MHz速率必须采用fly-by走线拓扑) |

| 信号组抗 | 单端阻抗:50 W(走线宽度5~6mil) |

| 与非DDR3信号的最小间距 | 25mil |

| 与其它DDR3信号组的最小间距 | 20mil |

| 控制信号与时钟对的程度匹配 | CLK<CTL<CLK+500mil |

| 注意: | |

- 命令信号

| 参数 | 描述 |

| 信号组(Signal Group) | Command: MBA(2:0),MA(15:0),MRAS_n,MCAS_n,MWE_n |

| 拓扑(Topology) | 如采用DIMM内存条:点对点 如采用内存颗粒:菊花链或fly-by(超过800MHz速率必须采用fly-by走线拓扑) |

| 信号组抗 | 单端阻抗:50 W(走线宽度5~6mil) |

| 与非DDR3信号的最小间距 | 25mil |

| 与其它DDR3信号组的最小间距 | 20mil |

| 控制信号与时钟对的程度匹配 | CLK<CMD<CLK+500mil |

| 注意: | |

- 数据信号

| 参数 | 描述 |

| 信号组(Signal Group) | Data: MDM(8:0),MDQ(63:0),MECC(7:0) |

| 拓扑(Topology) | 点对点信号 |

| 信号组抗 | 单端阻抗:50 W(走线宽度5~6mil) |

| 与非DDR3信号的最小间距 | 25mil |

| 与其它DDR3信号组的最小间距 | 20mil |

| 数据信号与DQS对的长度匹配 | 同一个分组内数据线与DQS等长度误差在+/-10mil |

- 数据选通信号

| 参数 | 描述 |

| 信号组(Signal Group) | Data Strobes: MQS_p(8:0),MQS_n(8:0) |

| 拓扑(Topology) | 点对点信号差分对 |

| 信号组抗 | 单端阻抗:40–50 W 差分阻抗:75-90 W |

| 与非DDR3信号的最小间距 | 25mil |

| 与其它DDR3信号组的最小间距 | 20mil |

| DQS_p与DQS_n长度匹配 | 总长度的最大差别<5mil |

2312

2312

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?