关注、星标公众号,精彩内容每日送达

来源:网络素材将图像处理的算法转换为FPGA系统设计的过程称为算法映射。映射过程中首目标便是确定系统设计的结构,在图像处理中常用的两中系统设计结构:流水线结构;并行阵列结构。

流水线设计基本概念

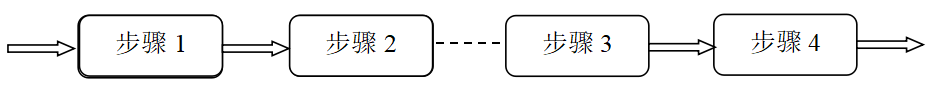

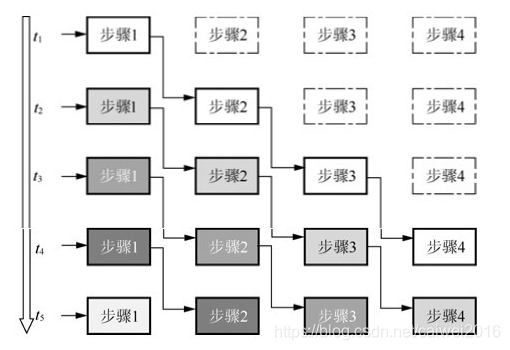

流水线处理源自现代工业生产装配线上的流水作业,是指将待处理的任务分解为相对独立的、可以顺序执行的而又相互关联的一个个子任务。流水线处理是高速设计中的一个常用设计手段,如果某个设计的处理流程分为若干步骤,并且整个数据处理是“单流向”的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,那么可以考虑采用流水线设计方法来提高系统频率。流水线设计结构如图所示。

其基本结构是将适当划分的n个操作步骤单流向串联起来。流水线操作的最大特点是数据流在各个步骤的处理从时间上看是连续的顺序操作,与此同时各个步骤又是同时并行的在运作。

在处理器架构上,一个单核处理器只能一次处理一个任务,是顺序的执行,如要实现并行操作需要多个处理器来执行。

FPGA中典型的流水线设计

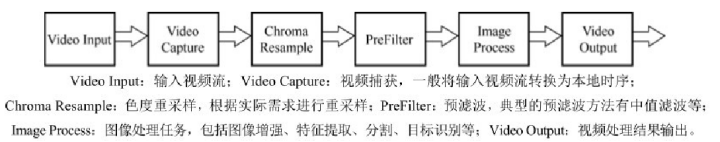

流水线处理采用面积换取速度的思想,可以大大提高电路的工作频率,尤其对于图像处理任务中的二维卷积运算、FIR及FFT滤波器等,采用流水线设计可以保证一个时钟输出一个像素,相对于全并行处理电路占用资源又不会太多。对于大部分的图像处理任务而言,处理过程基本上也是一个“串行”的处理思路。因此,流水线设计无疑是最好的设计方式。如下图所示是一个典型的图像处理任务流程图与图像处理中的典型流水线结构。

本处理任务也是一个典型的图像处理任务。首先,我们从CCD或CMOS传感器得到需要处理的视频流输入Video Input,并通过视频捕获模块Video Capture将输入视频同步为本地视频流。这些视频流“无等待”地流入下一个处理单元Chroma Resample进行色度重采样和空间变换,经过预处理Pre Filter和指定的处理算法Image Process后(例如预滤波、分割、目标识别、Alpha混合等),转换为视频流输出Video Output。

在这个过程中,输入视频流和输出视频流是连续的,流水线结构也保留了这种可能性。每一个处理单元独立为一块单独的电路,与其它处理单元同时运行,提高了速度也降低了设计的复杂度。

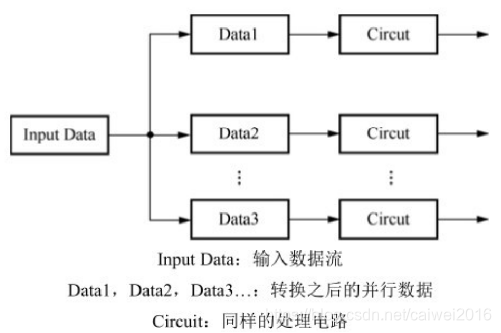

并行阵列

在并行阵列型电路中,多组并行排列的子电路同时接收整体数据的多个部分进行并行计算。并行阵列型电路中的子电路本身可以是简单的组合电路,也可以是复杂的时序电路例如上面提到的流水线型电路。如果受逻辑资源限制,无法同时处理全部数据,那么也可以依次处理部分数据直到完成全部数据的处理,如图所示。

和流水线共享电路的思路不同,并行阵列电路对于每个处理数据都生成一个处理电路,这无疑更大地提高了电路的处理速度,但是也带来了更大的资源消耗,是用面积换取速度原则的又一体现。如果系统设计对资源消耗相对不敏感,但是又需要较快的处理速度时,那么我们会选择并行结构来完成。

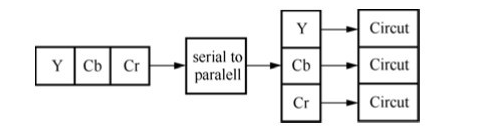

并行阵列的一个典型应用是多通道像素同时进行处理,对一个串行输入的RGB通道或是YCbCr通道的视频流,首先做一个串并转换,接着复制处理逻辑对三个通道同时做处理。这样理论上可以得到3倍的速度提升。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

6773

6773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?