关注、星标公众号,精彩内容每日送达

来源:网络素材吉比特收发器(MGT)是吉比特级串行器/解串器(SERDES)的别名。赛灵思7系列FPGA内部集成了能实现高速数据收发RocketI/O模块,采用了CML高速电平逻辑、CDR、线路编码(8B/10B)和预加重等技术的RocketI/O硬核模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,可用于实现吉比特以太网、PCI-Express、SRIO、SFP等常用接口。

吉比特高速串行I/O的最大缺点在于对信号完整性的严格要求。而且板材、高速连接器和电缆的费用较高

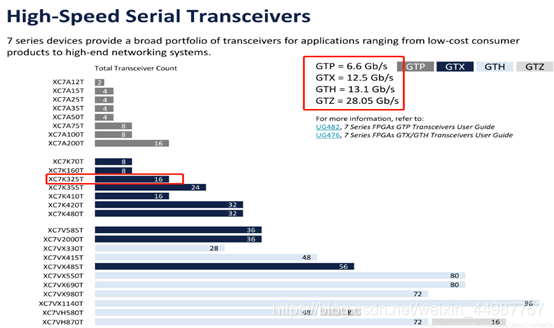

下图为赛灵思7系列FPGA高速串行接口(MGT)在各个型号芯片中的具体资源配置

*GTX结构与功能:

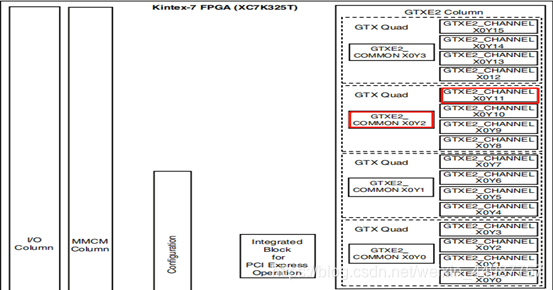

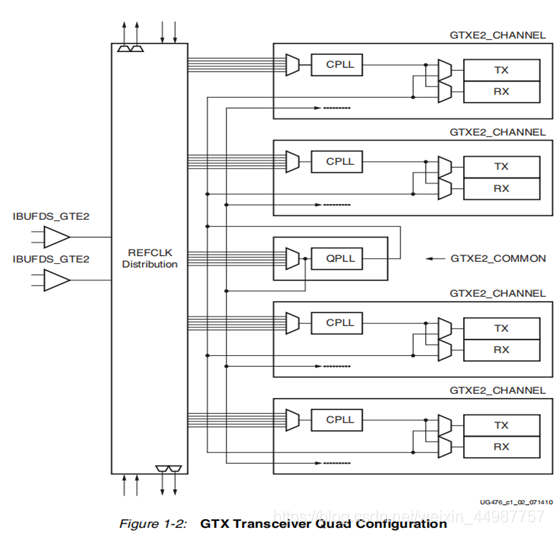

(1) 7系列FPGA通常按照bank来分,对于GTX的bank,一般称为一个Quad,原因是一个bank(Quad)中有4个独立的GTX通道以及一个时钟模块。每个通道称呼为Channel。所以在GTX的代码中可以看到Channel这个底层原语。

GTXE2_CHANNEL/GTHE2_CHANNEL 就是最后IP例化的名称。

GTXE2_COMMON/GTHE2_COMMON 就是最终IP中QPLL的名称.

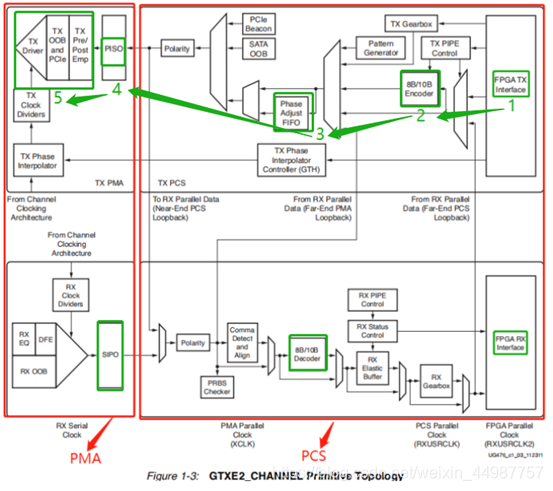

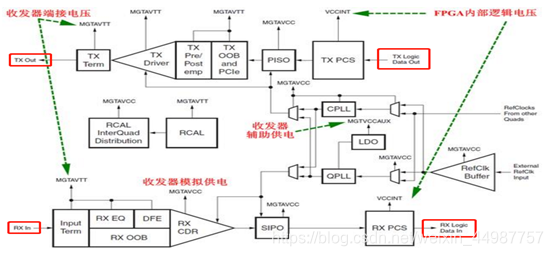

每一个CHANNEL的TX与RX接口都是由PMA和PCS组成;GTX的最小必要单元就是PMA,其主要原因就是核心的模拟部分。而PCS理论上可以全部由FPGA普通逻辑来实现。当然作为硬核提供的PCS功能更多、性能更好、使用更方便;

PCS提供丰富的物理编码层特性,如8b/10b编码等;

PMA部分为模拟电路,提供高性能的串行接口特性****

TX模块工作原理:

①将需要发送的16/32bit并行数据通过内部fifo传给编码模块;

②编码后的数据需要跨时钟域到并串转换模块(PCS到PMA)缓存到fifo;

③并串转换完成后发给TX驱动器调整数据电器特性后从高速IO口发出;*

RX模块工作原理与TX正好相反

调整数据电器特性、串并转换、8B/10B编码。

关于8B/10B编码的知识点:

作用:8B/10B编码有平衡电平,防止出现连续1/0的功能,其最大的优势在于自带错误检查,当8b10b错 误的时候大概率是链路质量问题;

缺点:8B/10B编码效率比较低,有20%的额外开销;常用于8G以下使用;

改进:GTX还提供了GearboX,其内部包含64b/66b编码;

(2)每个CHANNEL都有自己的专用锁相环CPLL;同时每个CHANNEL也可公用 同一个QPLL;

疑问:QPLL与CPLL有什么区别?

解答:解答:QPLL一般用到更高频率时使用;当收发器的线速度非常高,其CPLL的频率范围已无法满足需求时,QPLL就出场了。在GTX里面,CPLL的频率范围为1.6GHz~3.3GHz,支持的最高线速度为6.6Gb/s。QPLL的工作频率在低波段模式时为5.93 GHz到8.0GHz,在高波段的工作频率为9.8GHz~12.5GHz。无论是artix、kintex还是virtex,PLL的频率范围决定了收发器的最高线速度。

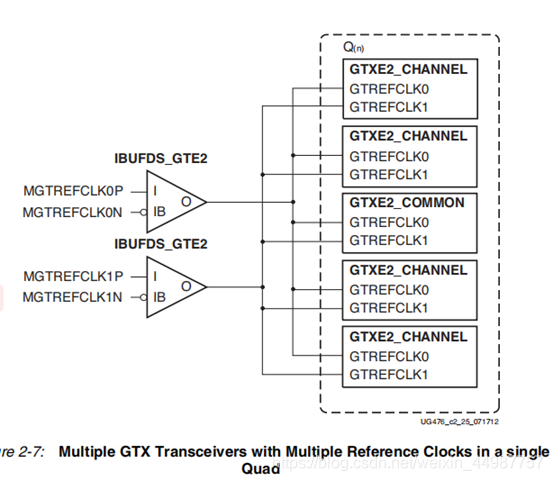

时钟的独立性:TX/RX的时钟独立,channel 时钟的独立,QUAD时钟的独立。

时钟可选择性:TX/RX的时钟可选,channel 时钟的可选,QUAD时钟的可选。

CPLL通常用于低速率传输通常在3.125G以下,QPLL通常用于高速率传输,QPLL的时钟更加精确,原则是能用QPLL就不用CPLL

硬件设计指导(K7-325T为例)

(1)概述:

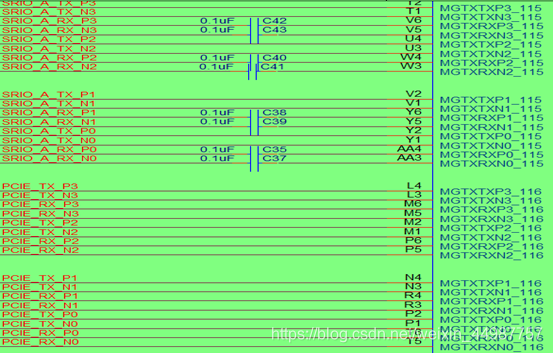

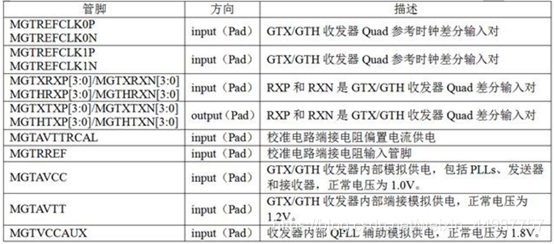

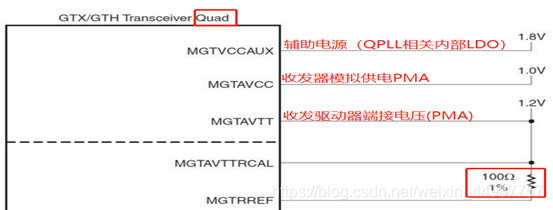

GTX/GTH收发器管脚定义

每种电压在GTX模块内部的具体作用点

K7具体供电电压需求

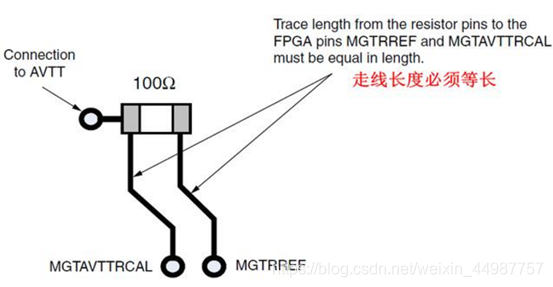

RCAL电路仅在FPGA配置器件执行校准功能,在配置前所有的模拟电压必须达到要求电压及其容忍误差,如果没使用Quad,MGTAVTTRCAL和MGTRREF管脚必须接地,电阻精度1%,PCB走线满足等长;

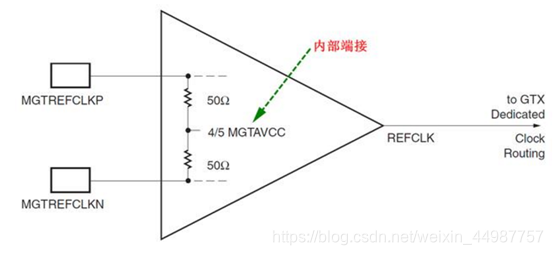

(2)时钟设计

MGTREFCLK输入buffer详细结构图中时钟管脚内部上拉至0.8V,当MGTAVCC收发器驱动电压不满足要求时,其参考时钟有可能出现问题;

当为GTX/GTH收发器选择晶振时,注意一下问题:

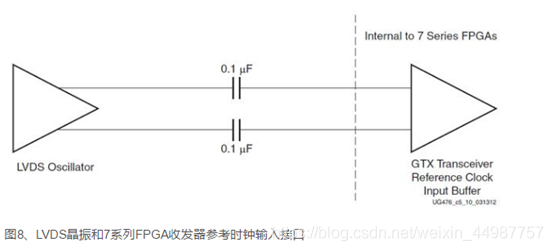

晶振输出管脚与GTX/GTH收发器Quad时钟输入管脚之间需要AC耦合

疑问:Quad时钟输入管脚对应哪一个REFCLK(0 or 1)?

解答:软件可以通过任意一个参考时钟通道连接到QPLL上;参考时钟差分电压摆幅满足开关特性要求;

遵守晶振供电、布局布线、噪声特性要求;

保持差分线阻抗连续(不要跨分割,以完整低平面为参考);

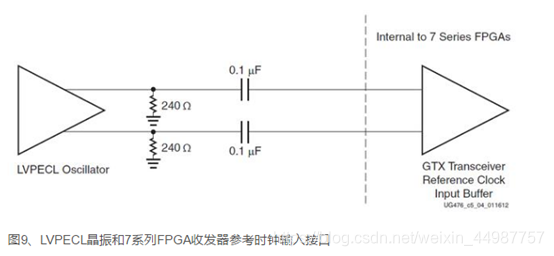

FPGA收发器GTX/GTH参考时钟接口电平有两种连接方式:LVDS与LVPECL;

如果参考时钟未使用,则参考时钟MGTREFCLKP和MGTREFCLKN应该悬空。

LVPECl耦合链路上的偏置电阻应以晶振推荐值为准;

AC耦合电容的作用(0.1uf):

阻断外部晶振与收发器Quad专用时钟管脚之间的DC电流,降低功耗;(隔直通交)

AC耦合电容和参考时钟输入端构成高通滤波器,衰减参考时钟偏移(时域上);

保持电容两端电压独立,互不干扰。

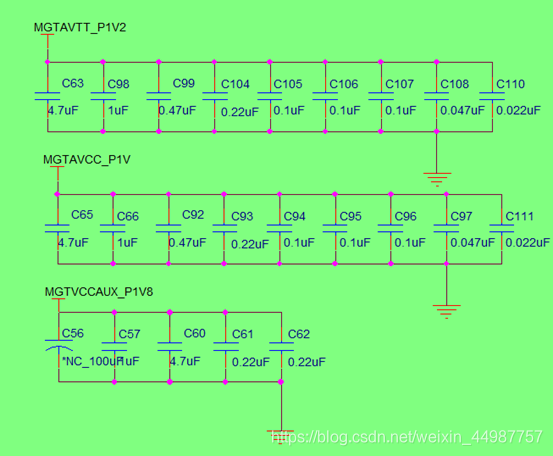

(3)电源滤波设计

GTX/GTH收发器对电源噪声比较敏感,电源噪声会导致收发器性能下降,来源于:

电源稳压器噪声(DCDC)

其他电路耦合

电源分布网络

在FPGA输入管脚测量的总的噪声Vpk-pk不能超过10mV,正常情况下,GTX/GTH模拟电源最后一级稳压器应尽量靠近收发器供电管脚,减小稳压器输出管脚到收发器电源输入管脚之间的距离,降低耦合噪声的概率;

虽然GTX模块对上电时序没有要求,但是任意的上电顺序也不会损坏芯片,但为了减少上电的瞬间电流,推荐一下上电顺序:

MGTVCCAUX > MGTAVCC > MGTAVTT。

其他资源介绍:

GTX的预加重和均衡:当使用到GTX的物理接口出现信号质量不佳,数据丢包,校验出错之类的情况时,为了提高信号质量,可以使用GTX提供的预加重、均衡、调整输出振幅等功能。预加重和调整输出振幅用于数据发送方向,均衡用于数据接收方向

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

5552

5552

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?